用于更新多GPU配置中的存储器侧高速缓存的系统和方法与流程

本公开总体上关于数据处理,并且更具体地关于经由通用图形处理单元进行的数据处理。

背景技术:

1、当前的并行图形数据处理包括被开发成对图形数据执行特定操作的系统和方法,这些特定操作诸如例如,线性内插、曲面细分、栅格化、纹理映射、深度测试等。传统上,图形处理器使用固定功能计算单元来处理图形数据;然而,最近已使图形处理器的多个部分变得可编程,从而使得此类处理器能够支持更宽泛种类的操作以处理顶点数据和片段数据。

2、为了进一步提升性能,图形处理器典型地实现诸如流水线化的处理技术,这些处理技术尝试贯穿图形流水线的不同部分并行地处理尽可能多的图形数据。具有单指令多线程(simt)架构的并行图形处理器被设计成使图形流水线中的并行处理的量最大化。在simt架构中,成组的并行线程尝试尽可能频繁地一起同步地执行程序指令以增加处理效率。可以在shane cook的cuda编程(cuda programming)第三章,第37-51页(2013)中找到对simt架构的软件和硬件的总体概述。

技术实现思路

技术特征:

1.一种异构处理系统,包括:

2.如权利要求1所述的异构处理系统,其中,第一图形处理器与第二高速缓存相关联。

3.如权利要求2所述的异构处理系统,其中,所述一致的芯片到芯片互连能操作以实现所述第一高速缓存与所述第二高速缓存之间的一致性。

4.如权利要求1所述的异构处理系统,其中,所述通用处理器和所述第一图形处理器具有统一虚拟存储器。

5.如权利要求4所述的异构处理系统,其中,所述统一虚拟存储器包括所述第一图形处理器的全部虚拟地址空间,并且所述统一虚拟存储器对所述通用处理器是能访问的。

6.如权利要求5所述的异构处理系统,其中,所述统一虚拟存储器包括所述通用处理器的全部虚拟地址空间,并且所述统一虚拟存储器对所述第一图形处理器是能访问的。

7.如权利要求1所述的异构处理系统,包括第二图形处理器,所述第二图形处理器具有第三存储器,所述第二图形处理器经由点对点互连与所述第一图形处理器耦合。

8.如权利要求7所述的异构处理系统,进一步包括第三集成电路,所述第三集成电路包括所述第二图形处理器。

9.如权利要求7所述的异构处理系统,其中,所述第一图形处理器被配置为用于经由所述点对点互连向所述第三存储器执行第一原子操作。

10.如权利要求9所述的异构处理系统,其中,所述通用处理器被配置为用于经由所述一致的芯片到芯片互连和所述点对点互连向所述第三存储器执行第二原子操作。

11.一种多芯片模块,包括:

12.如权利要求11所述的多芯片模块,其中,第一图形处理器与第二高速缓存相关联。

13.如权利要求12所述的多芯片模块,其中,所述一致的芯片到芯片互连能操作以实现所述第一高速缓存与所述第二高速缓存之间的一致性。

14.如权利要求11所述的多芯片模块,其中,所述通用处理器和所述第一图形处理器具有统一虚拟地址空间。

15.如权利要求14所述的多芯片模块,其中,所述统一虚拟地址空间包括所述第一图形处理器的全部虚拟存储器,并且所述统一虚拟地址空间对所述通用处理器是能访问的。

16.如权利要求15所述的多芯片模块,其中,所述统一虚拟地址空间包括所述通用处理器的全部虚拟存储器,并且所述统一虚拟地址空间对所述第一图形处理器是能访问的。

17.如权利要求11所述的多芯片模块,其中,所述第一图形处理器包括点对点互连,所述点对点互连能配置为用于将所述第一图形处理器与第二图形处理器耦合,所述第二图形处理器具有第三存储器。

18.如权利要求17所述的多芯片模块,其中,所述第二图形处理器被包括在第三封装集成电路中,所述第三封装集成电路在所述多芯片模块的外部。

19.如权利要求17所述的多芯片模块,其中,所述第一图形处理器被配置为用于经由所述点对点互连向所述第三存储器执行第一原子操作。

20.如权利要求19所述的多芯片模块,其中,所述通用处理器被配置为用于经由所述一致的芯片到芯片互连和所述点对点互连向所述第三存储器执行第二原子操作。

21.一种用于访问异构处理系统中的存储器的方法,所述方法包括:

22.如权利要求21所述的方法,包括:由所述第一图形处理器将来自所述第一存储器的数据高速缓存到与所述第一图形处理器相关联的第二高速缓存。

23.如权利要求22所述的方法,包括:由所述第一图形处理器将来自所述第一存储器的数据以高速缓存行粒度高速缓存到所述第二高速缓存。

24.如权利要求23所述的方法,包括:至少部分地经由所述一致的芯片到芯片互连实现所述第一高速缓存与所述第二高速缓存之间的一致性。

25.如权利要求24所述的方法,包括:附加地经由所述存储器管理电路实现所述第一高速缓存与所述第二高速缓存之间的一致性。

26.如权利要求25所述的方法,其中,所述通用处理器和所述第一图形处理器具有统一虚拟存储器。

27.如权利要求26所述的方法,包括:经由所述存储器管理电路使所述第一图形处理器的虚拟地址空间与所述通用处理器的虚拟地址空间同步。

28.如权利要求26所述的方法,包括:提供第三集成电路,所述第三集成电路包括第二图形处理器,并且经由点对点互连将所述第二图形处理器与所述第一图形处理器耦合,所述第二图形处理器具有第三存储器。

29.如权利要求28所述的方法,包括:由所述第一图形处理器经由所述点对点互连向所述第三存储器执行第一原子操作。

30.如权利要求29所述的方法,包括:由所述通用处理器经由所述一致的芯片到芯片互连和所述点对点互连向所述第三存储器执行第二原子操作。

31.一种存储指令的计算机可读介质,所述指令当被执行时使处理器执行如权利要求21至30中任一项所述的方法。

32.一种设备,包括用于执行如权利要求21至30中任一项所述的方法的装置。

技术总结

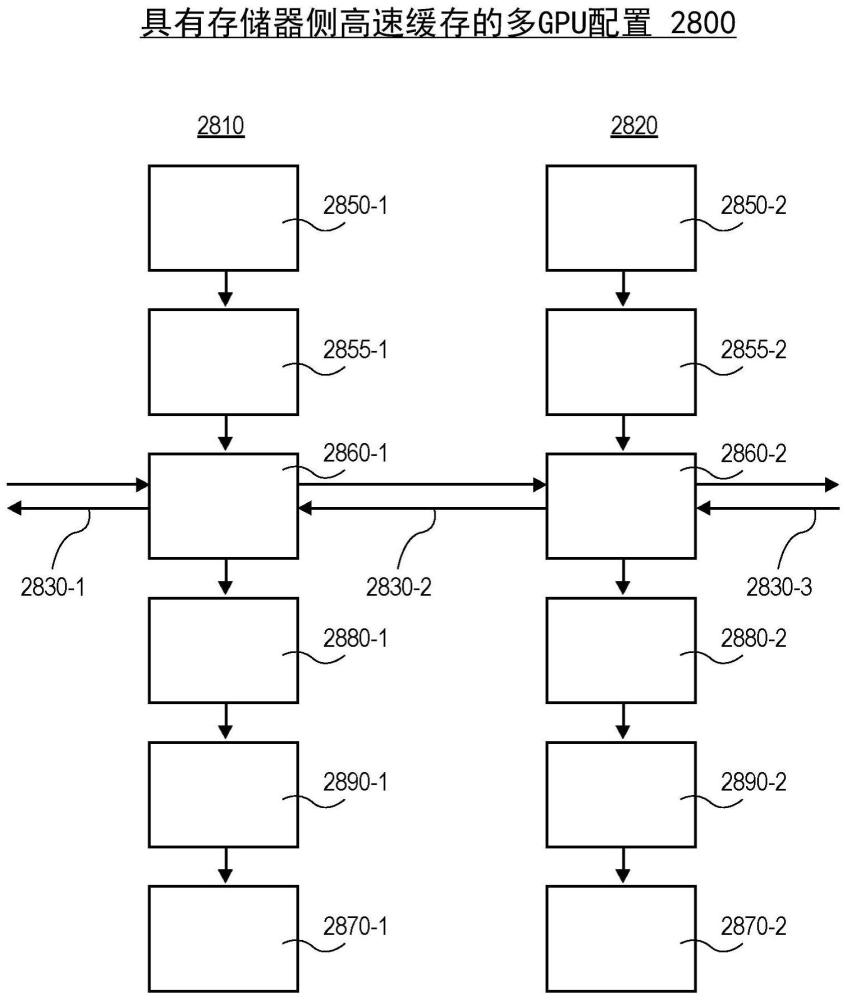

本文公开了用于更新多GPU配置中的远程存储器侧高速缓存的系统和方法。在一个实施例中,用于多片架构的图形处理器包括:第一图形处理单元(GPU)(2810),该第一GPU具有第一存储器(2870‑1)、第一存储器侧高速缓存存储器(2880‑1)、第一通信结构(2860‑1)和第一存储器管理单元(MMU)(2855‑1)。图形处理器包括第二GPU(2820),该第二GPU具有第二存储器(2870‑2)、第二存储器侧高速缓存存储器(2880‑2)、第二MMU(2855‑2)和第二通信结构(2860‑2),第二通信结构通信地耦合至第一通信结构。第一MMU配置成用于控制对第一存储器的存储器请求,更新第一存储器中的内容,更新第一存储器侧高速缓存存储器中的内容,并且确定是否更新第二存储器侧高速缓存存储器中的内容。

技术研发人员:A·考克,J·雷,A·阿南塔拉曼,V·安德烈,A·阿普,S·科尔曼,N·加洛泊凡博列斯,V·乔治,P·开,S·金,M·麦克弗森,S·马余兰,E·乌尔德-阿迈德-瓦尔,V·兰加纳坦,J·瓦莱里奥

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!