一种静态隐匿的DFF-PUF复合电路

本发明涉及电路设计和硬件安全,具体为一种静态隐匿的dff-puf复合电路。

背景技术:

1、现代各类保护信息安全的加密与认证机制都以密钥的保密性为基础,因此密钥的安全至关重要,其安全性在物理层面和软件层面都必须得到保障。然而,随着半导体微纳观测设备的不断发展,攻击者可以避开身份认证、算法加密等复杂的软件保护措施,直接通过物理攻击探测芯片底层器件的工作状态,进而获取密钥等关键数据,因此,为了应对日益严重的信息安全威胁,迫切需要提高芯片硬件的防护能力,尤其提高芯片密钥抵抗物理攻击的能力。物理不可克隆函数由于其不可预测、不可复制等优异的安全特性,成为芯片中极具应用前景的硬件密钥解决方案。

2、然而,在面对具有针对性的物理攻击时,puf仍然无法保证密钥的安全,由于puf具有明显的物理特征,攻击者通过puf电路的结构或者布局特征,可以轻易地对其进行定位并采取针对性的物理攻击,进而获取其关键的密钥信息,且一般的puf因不具有抗侵入式攻击的能力非常容易导致密钥被窃取,因此为保护密钥安全,需要一种不易被攻击者发现的puf。

3、现有的防护手段主要是在芯片中增加防护层以屏蔽旁路信息泄露和防止物理注入攻击,然而,引入防护层会占用大量芯片内部布线资源,或者需要使用额外的复合材料和加工手段,从而导致芯片制造成本急剧增加,同时,由于缺乏高灵敏度的防篡改检测机制,防护层还存在被修改和剥离的风险,无法真正建立起有效的物理攻击防护屏障,进一步地,传统伪装和混淆技术采用冗余电路配合辅助数据或者特征不明显的工艺修调,使不同逻辑电路具有相同的版图结构,虽然可以在一定程度上隐瞒puf电路的物理图像细节,使其与非敏感电路在版图上看起来相同,但无法完全消除伪装电路的物理层特征。

4、为了消除puf电路布局特征,一种有效的方式是将puf电路分散布局在数字版图中,由于数字版图结构复杂,攻击者难以从数字版图分析出原始电路,因此可以实现puf电路位置信息隐匿,所以,为了消除puf密钥单元的工艺特征,在电路层面和制造加工层面,puf密钥电路必须使用与非敏感电路完全相同的设计参数,同时在电路和版图上完全兼容数字逻辑电路,并且能够独立生成密钥,虽然sram-puf满足上述要求,但是其只能在上电时生成密钥,在芯片工作时需要持续存储密钥,丧失了puf随用随取的特点,同时也增加了密钥暴露的风险,故本发明提出了一种静态隐匿的dff-puf复合电路以解决上述问题。

技术实现思路

1、针对现有技术的不足,本发明提供了一种静态隐匿的dff-puf复合电路,具备安全性能好等优点,解决了sram-puf只能在上电时生成密钥,在芯片工作时需要持续存储密钥,丧失了puf随用随取的特点,同时也增加了密钥暴露风险的问题。

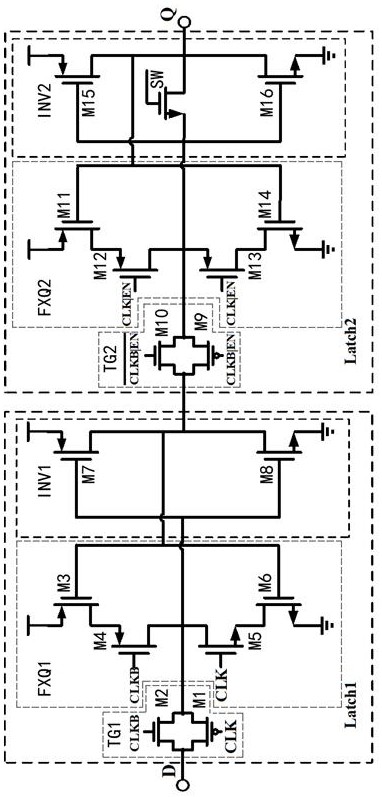

2、为实现上述目的,本发明提供如下技术方案:一种静态隐匿的dff-puf复合电路,包括输入端口d、第一锁存器latch1、第二锁存器latch2、使能开关sw和输出端口q,所述第一锁存器latch1包括第一传送门tg1、第一反相器fxq1和第一非门inv1,所述输入端口d与第一传送门tg1的输入端电性连接,所述第一传送门tg1的输出端分别与第一反相器fxq1的输出端和第一非门inv1的输入端电性连接,所述第二锁存器latch2包括第二传送门tg2、第二反相器fxq2和第二非门inv2,所述第一反相器fxq1的输入端和第一非门inv1的输出端均与第二传送门tg2的输入端电性连接,所述第二传送门tg2的输出端分别与第二反相器fxq2的输出端和第二非门inv2的输入端电性连接,所述第二反相器fxq2的输入端和第二非门inv2的输出端及使能开关sw的漏极均与输出端口q电性连接;

3、所述输入端口d用于输入信号,所述用于第一锁存器latch1用于对输入的信号进行传输或存储,所述第二锁存器latch2用于对第一锁存器latch1输出的信号进行传输或存储,所述第一传送门tg1用于对输入的信号进行传输,所述第二传送门tg2用于对第一锁存器latch1输出的信号进行传输,所述第一反相器fxq1和第二反相器fxq2均用于对输入的信号进行输出翻转或存储,所述第一非门inv1和第二非门inv2均用于对输入的信号进行翻转,所述使能开关sw用于控制第二传送门tg2、第二反相器fxq2的通断以及第二非门inv2是否短接;

4、第一控制时钟信号clk分别连接在第一传送门tg1的第一输入控制信号端、第一反相器fxq1的第一输入控制信号端、第二反相器fxq2的第一输入控制信号端和第二反相器fxq2的第二输入控制信号端,第二控制时钟信号clkb分别连接在第一传送门tg1的第二输入控制信号端、第一反相器fxq1的第二输入控制信号端、第二传送门tg2的第一输入控制信号端和第二传送门tg2的第二输入控制信号端,第一控制时钟信号clk和第二控制时钟信号clkb为反向信号,使能开关sw产生的使能开关信号en分别连接在第二传送门tg2的第一输入控制信号端、第二传送门tg2的第二输入控制信号端、第二反相器fxq2的第一输入控制信号端和第二反相器fxq2的第二输入控制信号端;

5、具体包括以下两种运行状态:

6、dff状态:当使能开关信号en为低电平0时,此时复合电路工作处于触发器状态,当第一控制时钟信号clk为低电平0时,第一传送门tg1导通,此时输入信号通过输入端口d和第一传送门tg1传输进第一反相器fxq1中,并通过第一非门inv1进行翻转,当第二控制时钟信号clkb为高电平1时,第二传送门tg2截止,使得第一非门inv1的输出信号存储在第一反相器fxq1中而不会进入第二传送门tg2中,当第一控制时钟信号clk为高电平1时,第一传送门tg1截止,此时输入信号不再进入第一传送门tg1中,使得第一非门inv1的输出信号保持之前状态不变,当第二控制时钟信号clkb为低电平0时,第二传送门tg2导通,将之前锁存在第一非门inv1的输出信号传输进第二传送门tg2中,然后进入第二非门inv2并通过输出端向外输出,实现输出信号等于输入信号;

7、puf密钥生成状态:当使能开关信号en为高电平1时,此时复合电路处于密钥生成的准备状态,第一传送门tg1、第一反相器fxq1和第一非门inv1仍然根据第一控制时钟信号clk对输入信号进行传输或存储,而第二非门inv2的输入端和输出端短接,且第二反相器fxq2截止,此时令第二非门inv2的输入电压为vm,第二非门inv2的输出电压为vout,则第二反相器fxq2的输出端与第二非门inv2的输入端连接处的电压与第二非门inv2输出的电压均维持在vm,当使能开关信号en和第一控制时钟信号clk均为低电平0时,由于第二非门inv2的输出翻转阈值vdecision等于vm,第二传送门tg2、第二反相器fxq2和第二非门inv2将整体维持在亚稳态,根据第二反相器fxq2驱动强度不匹配引起电流失衡,使得电压vm与vdecision产生偏离电压δv,偏离电压δv进一步被第二非门inv2构成的灵敏放大器放大并锁存,实现数字密钥0或1的转换。

8、进一步,所述第一传送门tg1包括第一前端开关m1和第二前端开关m2,所述输入端口d与第一前端开关m1的漏极、第二前端开关m2的源极电性连接,所述第一前端开关m1的源极、第二前端开关m2的漏极与第一反相器fxq1的输出端和第一非门inv1的输入端电性连接。

9、进一步,所述第一反相器fxq1包括第一中端开关m3、第二中端开关m4、第三中端开关m5和第四中端开关m6,所述第二中端开关m4的漏极和第三中端开关m5的漏极均与第一前端开关m1的源极和第二前端开关m2的漏极电性连接,所述第二中端开关m4的源极与第一中端开关m3的漏极电性连接,所述第三中端开关m5的源极与第四中端开关m6的漏极电性连接,所述第一中端开关m3的栅极、第四中端开关m6的栅极和第一非门inv1的输出端均与第二传送门tg2的输入端电性连接。

10、进一步,所述第一非门inv1包括第一后端开关m7和第二后端开关m8,所述第一后端开关m7的栅极和第二后端开关m8的栅极均与第二中端开关m4的漏极和第三中端开关m5的漏极电性连接,所述第一后端开关m7的漏极和第二后端开关m8的漏极、第一中端开关m3的栅极、第四中端开关m6的栅极均与第二传送门tg2的输入端电性连接。

11、进一步,所述第二传送门tg2包括第三前端开关m9和第四前端开关m10,所述第三前端开关m9的漏极、第四前端开关m10的源极与第一后端开关m7的漏极、第二后端开关m8的漏极电性连接,第三前端开关m9的源极、第四前端开关m10的漏极与第二反相器fxq2的输出端和第二非门inv2的输入端电性连接。

12、进一步,所述第二反相器fxq2包括第五中端开关m11、第六中端开关m12、第七中端开关m13和第八中端开关m14,所述第六中端开关m12的漏极和第七中端开关m13的漏极与第三前端开关m9的源极和第四前端开关m10的漏极电性连接,所述第六中端开关m12的源极与第五中端开关m11的漏极电性连接,所述第七中端开关m13的源极与第八中端开关m14的漏极电性连接,所述第五中端开关m11的栅极和第八中端开关m14的栅极均与第二非门inv2的输出端和输出端口q电性连接。

13、进一步,所述第二非门inv2包括第三后端开关m15和第四后端开关m16,所述第三后端开关m15的栅极、第四后端开关m16的栅极和使能开关sw的源极均与第六中端开关m12的漏极和第七中端开关m13的源极电性连接,所述第五中端开关m11的栅极、第八中端开关m14的栅极、第三后端开关m15的漏极、第四后端开关m16的漏极、使能开关sw的漏极均与输出端口q电性连接。

14、进一步,所述第一前端开关m1、第一中端开关m3、第二中端开关m4、第一后端开关m7、第三前端开关m9、第五中端开关m11、第六中端开关m12、第七中端开关m13和第三后端开关m15均为pmos管,所述第二前端开关m2、第三中端开关m5、第四中端开关m6、第二后端开关m8、第四前端开关m10、第八中端开关m14和第四后端开关m16和使能开关sw均为nmos管。

15、进一步,所述第一控制时钟信号clk分别连接在第一前端开关m1的栅极、第三中端开关m5的栅极、第六中端开关m12的栅极和第七中端开关m13的栅极,所述第二控制时钟信号clkb分别连接在第二前端开关m2的栅极、第二中端开关m4的栅极、第三前端开关m9的栅极和第四前端开关m10的栅极,所述使能开关sw产生的使能开关信号en分别连接在第三前端开关m9的栅极、第四前端开关m10的栅极、第六中端开关m12的栅极和第七中端开关m13的栅极,所述第一中端开关m3的源极、第一后端开关m7的源极、第五中端开关m11的源极和第三后端开关m15的源极均与电源电性连接,所述第四中端开关m6的源极、第二后端开关m8的源极、第八中端开关m14的源极和第四后端开关m16的源极均接地。

16、与现有技术相比,本技术的技术方案具备以下有益效果:

17、1.该静态隐匿的dff-puf复合电路,相较于采用传统puf伪装和混淆技术在一定程度上隐瞒puf电路的物理图像细节,dff-puf复合电路可以完全消除伪装电路的物理层特征,使其在电路和版图上完全兼容数字逻辑电路,实现密钥单元的静态隐匿,从而确保了密钥信息的安全;

18、2.该静态隐匿的dff-puf复合电路,相较于sram-puf基于非门之间阈值电压失配生成密钥,本发明使用对工艺误差更为敏感的亚阈值电流作为失配传输源,进而可以获得标准差更大的失配分布,同时还避免了其密钥不能随用随取的缺点;

19、3.该静态隐匿的dff-puf复合电路,高度复用了dff中本身的电路结构,以较低成本实现了puf的功能,未引入过大的硬件开销。

- 还没有人留言评论。精彩留言会获得点赞!