一种串行通用输入输出方法与系统与流程

本发明涉及数据传输,特别是涉及一种串行通用输入输出方法与系统。

背景技术:

1、近年来,受益于人工智能等相关新兴领域的应用以及云计算的蓬勃发展,数据计算和数据存储需求呈几何级增长,服务器对硬盘的带宽和容量需求日益增加,由此带动服务器硬盘数量增加,导致服务器机房的硬盘管理更加困难,发现并更换已损坏的硬盘变得复杂而又繁琐。

2、通过硬盘状态指示系统的状态可以直接用肉眼查看每个硬盘的运行状态。 目前市场上有采用复杂可编程逻辑器件(complex programmable logic device,简称为:cpld)或现场可编程逻辑门阵列(field programmable gate array,简写为:fpga)或专用集成电路(application specific integrated circuit,简写为:asic)设计的硬盘背板,使用cpld或fpga或asic解析串行通用输入/输出(serial general purpose input/output,简写为:sgpio)信号控制硬盘状态指示系统,并指示硬盘的活动、错误、位置状态指示等功能,使得服务器更加智能和易于维护。

3、硬盘状态指示系统,一般使用led灯指示硬盘状态。每个硬盘有2或3个状态灯,分别表示硬盘的不同状态,具体可以参考sff-8485和sff-8489技术规范。由于硬盘数量多,每个硬盘使用三个状态灯,会导致控制接口数量偏多。为减少控制接口数量,降低实现难度,同时兼容现行主流方案,使用sgpio协议作为控制主机和控制从机的通信方式。

4、目前asic芯片价格偏高,且支持的接口数量在8个以内,往往需要使用多片asic芯片扩展使用才能满足日益增加的硬盘数量需求。而多个asic芯片级联会导致背板面积增加,进一步增加成本;而cpld或fpga价格和功耗都偏高,不能满足市场对低成本和低功耗的需求。

5、鉴于此,克服该预设技术所存在的缺陷是本技术领域亟待解决的问题。

技术实现思路

1、本发明要解决的技术问题是如何在实现对硬盘状态灯进行信号传输控制的前提下,减少服务器背板的占用面积并且降低成本。

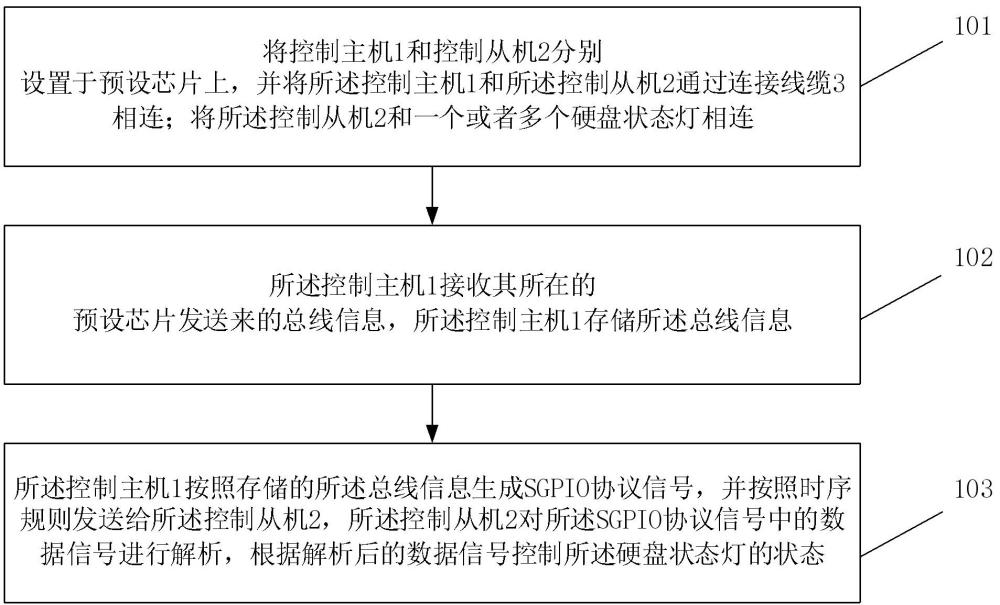

2、第一方面,提供一种串行通用输入输出方法,将控制主机1和控制从机2分别设置于预设芯片上,并将所述控制主机1和所述控制从机2通过连接线缆3相连;将所述控制从机2和一个或者多个硬盘状态灯相连;包括:

3、所述控制主机1接收其所在的预设芯片发送来的总线信息,所述控制主机1存储所述总线信息;

4、所述控制主机1按照存储的所述总线信息生成sgpio协议信号,并按照时序规则发送给所述控制从机2,所述控制从机2对所述sgpio协议信号中的数据信号进行解析,根据解析后的数据信号控制所述硬盘状态灯的状态。

5、优选的,所述sgpio协议信号包括时钟信号、控制信号和数据信号;在所述控制主机1和所述控制从机2之间设置至少四根连接线缆3;

6、所述控制主机1按照存储的所述总线信息生成sgpio协议信号,并按照时序规则发送给所述控制从机2,具体包括:

7、所述控制主机1通过其中两根连接线缆3分别将时钟信号和控制信号传输至所述控制从机2;

8、基于所述时钟信号和控制信号,所述控制主机1通过其中一根连接线缆3向所述控制从机2发送数据信号,所述控制从机2其中一根连接线缆3向所述控制主机1发送数据信号。

9、优选的,所述基于所述时钟信号和控制信号,所述控制主机1通过其中一根连接线缆3向所述控制从机2发送数据信号,所述控制从机2其中一根连接线缆3向所述控制主机1发送数据信号,具体包括:

10、对所述时钟信号的上升沿和下降沿进行检测,一个时钟周期包含一个上升沿和一个下降沿,在每个周期中,执行如下步骤:

11、当所述时钟信号处于上升沿时,所述控制主机1向所述控制从机2发送a bit数据信号,所述控制从机2向所述控制主机1发送a bit数据信号;

12、当所述时钟信号处于下降沿时,所述控制主机1接收来自控制从机2的a bit数据信号,所述控制从机2接收来自控制主机1的a bit数据信号。

13、优选的,所述基于所述时钟信号和控制信号,所述控制主机1通过其中一根连接线缆3向所述控制从机2发送数据信号,所述控制从机2其中一根连接线缆3向所述控制主机1发送数据信号,还包括:

14、每个数据流包括ba bit的数据信号,在发送并接收单个数据流的b个周期内:

15、前b-1个周期中所述控制信号为低电平;

16、当第b-1个周期的下降沿过渡至第b个周期的上升沿时,所述控制信号由低电平变为高电平;

17、当第b个周期的下降沿结束时,所述控制信号由高电平变为低电平;

18、当所述控制信号由高电平变为低电平时,所述控制从机2判断单个数据流接收完成。

19、优选的,所述控制从机2设置有b个引脚,每个所述引脚和单个硬盘状态灯相接;

20、所述控制从机2对所述sgpio协议信号中的数据信号进行解析,根据解析后的数据信号控制所述硬盘状态灯的状态,具体包括:

21、所述控制从机2将接收到的sgpio协议信号中的数据流进行解析;

22、所述控制从机2将解析后的数据流发送给b个硬盘状态灯,每个所述硬盘状态灯接收相应的解析后的a bit的数据信号,从而控制所述硬盘状态灯的状态。

23、第二方面,提供一种串行通用输入输出系统,用于应用所述的串行通用输入输出方法,包括:控制主机1和控制从机2,其中:

24、所述控制主机1和控制从机2分别设置于预设芯片上,所述控制主机1和所述控制从机2通过连接线缆3相连;所述控制从机2上和一个或者多个硬盘状态灯相连;

25、所述控制主机1用于接收其所在预设芯片发送来的总线信息,并将所述总线信息存储;

26、所述控制主机1还用于按照存储的所述总线信息生成sgpio协议信号并按照时序规则发送给所述控制从机2;

27、所述控制从机2用于对所述sgpio协议信号中的数据信号进行解析,根据解析后的数据信号控制所述硬盘状态灯的状态。

28、优选的,所述控制主机1包括:第一总线接口模块11、第一内部寄存器模块12和第一协议转换模块13,其中:

29、所述第一总线接口模块11、第一内部寄存器模块12和第一协议转换模块13依次相接;

30、所述第一总线接口模块11用于接收来自所述预设芯片的总线信息,并将所述总线信息发送给所述第一内部寄存器模块12;

31、所述第一内部寄存器模块12用于预先配置相应的协议规范,以及存储所述控制主机1接收到的信息;

32、所述第一协议转换模块13用于根据所述第一内部寄存器内存储的总线信息以及预先配置的协议规范,生成所述sgpio协议信号,并发送给所述控制从机2。

33、优选的,所述控制从机2包括:第二总线接口模块21、第二内部寄存器模块22和第二协议转换模块23,其中:

34、所述第二总线接口模块21、第二内部寄存器模块22和第二协议转换模块23依次相接;

35、所述第二总线接口模块21用于接收来自所述预设芯片的总线信息,并将所述总线信息发送给所述第二内部寄存器模块22;

36、所述第二内部寄存器模块22用于预先配置相应的协议规范,以及存储所述控制从机2接收到的sgpio协议信号;

37、所述第二协议转换模块23用于根据所述第二内部寄存器模块22内预先配置的协议规范,解析所述第二内部寄存器模块22内的sgpio协议信号,并将解析后的sgpio协议信号发送给相应的硬盘状态灯;还用于从所述第二内部寄存器模块22内调用相应的数据信号发送给所述控制主机1。

38、优选的,所述sgpio协议信号包括时钟信号、控制信号和数据信号;

39、所述控制主机1和所述控制从机2之间设置有至少四根连接线缆3;

40、其中两根连接线缆3用于供所述控制主机1分别将时钟信号和控制信号传输至所述控制从机2;

41、基于所述时钟信号和控制信号,其中一根连接线缆3用于供所述控制主机1向所述控制从机2发送数据信号,其中一根连接线缆3用于供所述控制从机2向所述控制主机1发送数据信号。

42、优选的,所述控制从机2设置有多个引脚,每个所述引脚和单个硬盘状态灯相接;

43、所述控制从机2还用于对所述sgpio协议信号中的数据信号进行解析,并将解析后的数据信号通过所述引脚发送给各个硬盘状态灯,从而控制所述硬盘状态灯的状态。

44、本发明提供了一种串行通用输入输出方法与系统,通过将控制主机和控制从机集成在现有的芯片上,并将所述控制主机和所述控制从机通过连接线缆相连;将所述控制从机和一个或者多个硬盘状态灯相连,所述控制主机接收预设芯片发送来的总线信息,将存储的所述总线信息作为sgpio协议信号,并按照时序规则发送给所述控制从机,所述控制从机将所述sgpio协议信号中的数据信号发送给相应的硬盘状态灯,从而控制所述硬盘状态灯的状态,无需使用专门的硬盘状态指示芯片,并且支持多个硬盘状态灯的信号传输的同时,减少背板电路板面积和背板硬件实现的复杂度,从而降低成本。

- 还没有人留言评论。精彩留言会获得点赞!