一种多级存储器的配置方法与流程

本发明涉及数字信号处理,具体涉及一种多级存储器的配置方法。

背景技术:

1、数字信号处理器(digital signal processing,dsp)是对信号和图像实现实时处理的一类高性能的中央处理器(central processing unit,cpu)。目前,在高性能dsp平台上实现部分复杂图像处理算法成为了dsp应用研究的一个热点,并且数字信号处理器具有运算性能强、低功耗、体积小等特点,广泛的应用于工业和军事领域。

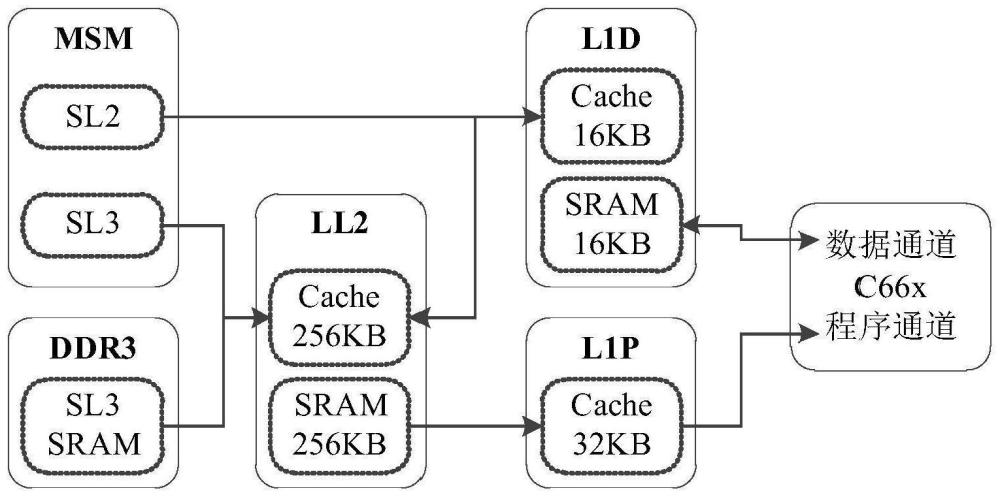

2、由于技术的发展,数字信号处理器从最初的单核发展到现在的多核。其中ti公司生产的tms320c6678就是多核dsp中杰出的代表,采用了keystone架构将8个c66x内核集成到一个dsp上,提升了每个内核的内核频率,使得c66x的内核频率达到了1.25ghz。其运算性能高达160gflops,片内整合了丰富的协处理器、高性能i/o组件和存储资源,给予了tms320c6678强大的运算能力,将其应用于图像处理平台成为业界的趋势。keystone架构的原理图如图1所示。

3、现代计算机中,为了加快cpu访存的速度与较高的性价比,往往都采用了多级存储结构来加快cpu的访存速度。tms320c6678受限于硬件资源的有限,采取了多级存储结构技术加快访存速度。tms320c6678的存储器可以分成三级:l1、ll2、msm+sdram。其中l1存储器又被称为一级存储器,包括l1d和l1p存储器,二者都有32kb的存储大小,该存储器的访问速度与内核速度一致。ll2存储器又被称为二级存储器,其拥有512k大小的存储能力,为一级存储器容量不足提供了一个很好的补充,但是其访问速度仅为内核速度的一半。三级存储器由两部分组成,第一部分是由多核共享存储控制器(multicore shared memorycontroller,msmc)模块管理的容量为4mb的共享存储器,第二部分是外部扩展存储器,外部扩展存储器是对片内存储器存储容量极大的扩充。

4、tms320c6678除了提供了存储器的分级结构与相关配套设施,还允许开发人员根据实际需要对一级存储器l1、二级存储器ll2进行配置。配置方案包括将存储器配置成sram、将存储器配置成cache或者将存储器配置成静态随机存储器(static random accessmemory,sram)与cache混合模式。不过需要注意的是,混合配置模式使用的存储器总容量是不会变的,此消彼长。一般存储器配置方案图及数据流向如图2所示。

5、传统计算机中数据在各设备之间的传送需要cpu进行干预,如此一来,每次传送数据时都会影响cpu执行当前的任务,因此造成了任务执行效率的下降。存储器直接访问(direct memory access,dma)技术的出现解决了数据传送需要cpu进行参与的问题,释放的cpu可以处理其他事务,从而提高任务处理效率。特别地,当多核处理任务中的某一核由于数据传送导致处理时间增加,从而必然导致多核间的同步操作延时增加,会严重的影响系统性能。dma技术在大数据量进行搬移的过程中不需要内核的参与,其优异特性可以解决研究中发现的内核在参与大数据搬移时造成的延迟问题。

6、ti公司生产的数字信号处理器使用的dma技术从最初基于寄存器而实现的dma技术到基于ram结构实现的增强型直接存储器访问(enhanced direct memory access,edma)与快速直接内存访问(quick direct memory access,qdma)技术,再发展到内部直接内存访问(internal dma,idma)技术,再到根据keystone架构而设计的包直接存储器访问(packet dma,pktdma)技术。

7、edma:keystone架构中支持的增强dma技术为edma3,该版本的edma技术较之前版本相比,使用更加灵活,提供的信道数几乎增加了一倍。edma3支持1维、2维、3维数据进行传输。其中2维传输是基于1维传输技术之上的,2维传输通过索引,将二维在逻辑上转换成多个1维数据进行传输,而3维传输技术是建立在二维传输技术之上实现的,同样也是使用索引技术,需要注意的是各个索引之间是相互独立的。数据传输方式的多样性使得处理图像这类需要大数据传输的应用更加方便。

8、qdma:qdma其实是对edma技术的一个补充,二者使用的技术相差并不大。相比edma,qdma不支持2维、3维数据传送,不支持事件触发数据传送,但是qdma提交数据传送的请求周期较短,并且不同数据传输只需要改变少量参数,所以性能来说优于edma。

9、idma:相比edma、qdma对数据传送源和目的地址没有限制而言,idma限制了该技术只能使用在l1与ll2存储器之间的数据传送。并且idma部件被设计到了核内,由于内核空间、功率的限制,决定了idma结构不能过于复杂,工作频率与主核一致。idma技术中包含两个相互独立物理通道,通道0负责对寄存器的快速配置,完成数据传送之前的相关配置,通道1负责数据的传送工作。

10、idma相比cache技术传送效率更快,因为idma配置工作较小,只需要配置几个寄存器即可,而cache技术需要内核的参与。并且如果重新配置已经配置过的idma,只需要更改一个寄存器的状态即可。

11、pktdma:由于pktdma主要是根据keystone架构进行设计的,所以其主要被用于多核导航器内。与其他dma技术目的相同,pktdma技术也是为了解决在点对点的数据传送中解放内核而产生的,与其他dma不同的是pktdma并不关心传送数据的结构,无论有效载荷数据的结构是什么,最终pktdma在传送数据时是以数据包的方式进行传送。

12、pktdma有多个被称为rx的接收通道和tx的发送通道,接收信道与发送信道各自有一个dma引擎,并且一个信道同时只能被一个包所占用。pktdma传送与接收有效载荷的数据,实际上是任务描述符的索引。而enhanced dma与internal dma,实际上只有一个信道用于收发的功能。

13、用dsp来完成图像处理任务时,由于图像处理中涉及的数据量较大,而数字信号处理器的内存较小,会造成各级存储器之间存在大量数据搬移的需求,数据搬移的速度是影响系统处理任务速度的重要因素之一。

14、dsp的片内存储器的容量比片外存储器容量要小很多,但是片内存储器的性能更高,cpu读写开销更小。用dsp来完成图像处理任务时,由于处理的数据量往往都很大,片内存储器容量难以满足要求,数据需要保存到片外存储器上,这样一来每次处理数据的时候都需要片内存储器与片外存储器进行交互,若片内与片外存储器进行数据交互时都仅依靠cpu发出load与stw指令,那将会极大的降低系统处理任务的效率。

技术实现思路

1、本发明的目的是:各级存储器之间的数据高效搬移。

2、为了实现上述发明目的,本发明的技术方案是提供了一种多级存储器的配置方法,其特征在于,应用于大数据交互搬移,所述方法包括:

3、将存储器分为内部存储器模块、外部存储器模块以及内外部存储器模块;

4、内部存储器模块的多个内核子系统设有多个idma引擎,内部存储器模块包括本地存储器l1p、l1d和ll2存储器,将l1p存储器配置成cache模式,将l1d和ll2存储器配置为cache和sram的混合模式,且cache和sram分别占一半的l1d和ll2存储器容量;

5、外部存储器模块包括外部存储器msm(multicore shared memory,msm)和ddr3;

6、内外部存储器模块包括外部存储器msm和多个内核子系统中的ll2存储器;

7、当在内部存储器模块进行大数据交互搬移时,多级存储器启动多个idma引擎进行大数据交互搬移;

8、当在外部存储器模块进行大数据交互搬移时,多级存储器将图像数据帧存储于ddr3中,多个内核子系统共同处理的数据和处理后的图像数据帧通常存放在msm中,以避免需要处理的前后帧相同的图像数据来回搬移,造成数据抖动过于激烈。多级存储器采用edma技术进行大数据交互搬移;

9、当在内外部存储器模块进行大数据交互搬移时,多级存储器采用edma技术在msm存储器与ll2存储器之间进行数据搬移,内部存储器模块将ll2存储器的数据通过idma技术搬移至l1d中进行数据处理;

10、当多级存储器与外部设备之间进行大数据交互搬移时,采用pktdma技术进行大数据交互搬移。

11、优选地,所述当在内部存储器模块进行大数据交互搬移时,有效传输带宽的传输速率达到7000mbps-8000mbps之间。

12、优选地,所述当在外部存储器模块进行大数据交互搬移时,所述外部存储器模块中的msm用于存储前后帧相同的图像数据,以避免数据来回搬移。

13、优选地,所述当在外部存储器模块进行大数据交互搬移时,所述当在外部存储器模块进行大数据交互搬移时,所述外部存储器模块的搬移带宽的传输速率达到5000mbps。

14、优选地,所述当在内外部存储器模块进行大数据交互搬移时,所述内外部存储器模块的搬移带宽的传输速率达到5000mbps。

15、优选地,所述当在内外部存储器模块进行大数据交互搬移时,所述多级存储器与外部设备之间进行大数据交互搬移时,载荷数据的大小与单信道的pktdma数据传送速度成正比关系。

16、本发明提出的技术方案一种多级存储器的配置方法,基于多种dma技术支撑,在大数据交互搬移时具有高带宽优势,能够在无内核参与的情况下完成各级存储器之间的数据高效搬移。内部存储器模块之间数据搬移的有效传输带宽可达到7000mbps以上,较接近理论值8000mbps。外部存储器模块之间以及内部与外部存储器模块之间的数据搬移带宽可达到5000mbps。本发明提出的技术方案解决了大批量图像数据传输速度瓶颈的同时,又能让dsp处理器专门从事算法处理工作,极大地提高了系统的并行性能,适用于大批量的数字信号处理领域,尤其是雷达信号数据的处理,能大提高数据处理的实时性。

- 还没有人留言评论。精彩留言会获得点赞!