一种混合时钟树结构设计方法、装置、设备及存储介质与流程

本技术涉及集成电路物理设计的,尤其是涉及一种混合时钟树结构设计方法、装置、设备及存储介质。

背景技术:

1、在数字集成电路中,时钟信号是数据传输的基准,寄存器的状态只有在时钟信号到达时才会改变。在同一时钟域内,各寄存器由共同的时钟信号控制,要想电路实现正确的逻辑功能,时钟信号就必须在相同的时间内达到各寄存器的时钟输入端,即时钟偏差要尽可能地接近于零。对于先进工艺条件下的超大规模集成电路来说,一个好的时钟树结构不仅需要考虑时钟偏差、延迟、面积和功耗,它在寄存器布局不均匀情况下的适用性和对工艺偏差的抵抗能力也同样变得重要。因此,开发一种时钟偏差和延迟小,同时具有良好的普适性和抗干扰能力的时钟树结构对于集成电路物理设计领域具有重要意义。

2、目前,传统时钟树综合方案主要包括二叉型时钟树和h型时钟树,二叉型时钟树是以时钟源为根节点,通过每一级的缓冲器分支传递时钟信号至寄存器,其布线方式比较灵活,适用于绝大部分的设计;h型时钟树具有天生的对称结构,从时钟源到最后一级缓冲器之间的布线长度相等,具有减小时钟偏差的特点。

3、然而,二叉型时钟树在平衡时钟偏差时需要插入大量缓冲器,导致时钟延迟增加,消耗更多的面积和功耗;h型时钟树虽然减小了时钟偏差,但其理想的结构无法适用于实际集成电路的复杂布局,且在抵抗工艺不确定性和芯片不稳定性方面存在局限性;因此,现有的时钟树结构难以同时缓解时钟偏差大、延迟高、适应性差、抗干扰能力差的问题。

技术实现思路

1、为了缓解现有时钟树结构偏差大、延迟高、适应性差、抗干扰能力差的问题,本技术提供一种混合时钟树结构设计方法、装置、设备及存储介质。

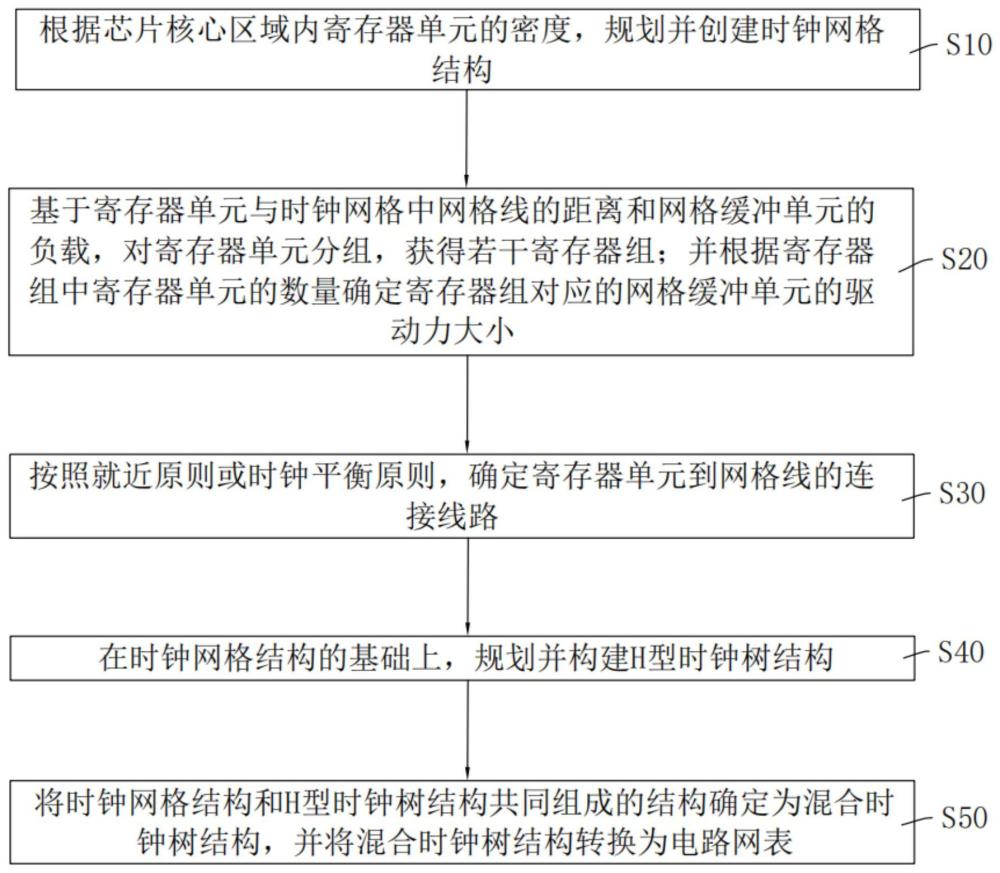

2、第一方面,本技术提供一种混合时钟树结构设计方法,采用如下的技术方案:所述方法应用于时钟树结构设计系统,所述时钟树结构设计系统包括芯片核心区域内的若干寄存器单元和网格缓冲单元,所述方法包括:

3、根据芯片核心区域内所述寄存器单元的密度,规划并创建时钟网格结构;

4、基于所述寄存器单元与所述时钟网格中网格线的距离和所述网格缓冲单元的负载,对所述寄存器单元分组,获得若干寄存器组;并根据所述寄存器组中寄存器单元的数量确定所述寄存器组对应的网格缓冲单元的驱动力大小;

5、按照就近原则或时钟平衡原则,确定所述寄存器单元到所述网格线的连接线路;

6、在所述时钟网格结构的基础上,规划并构建h型时钟树结构;

7、将所述时钟网格结构和所述h型时钟树结构共同组成的结构确定为混合时钟树结构,并将所述混合时钟树结构转换为电路网表。

8、在一个具体的可实施方案中,所述根据芯片核心区域内所述寄存器单元的密度,规划并创建时钟网格包括:

9、确定芯片核心区域对应的宽度、高度和所述核心区域内寄存器单元的密度;

10、基于所述宽度、高度和所述寄存器单元的密度,计算时钟网格对应的网格线的数量,所述网格线的数量包括纵向网格线的数量和横向网格线的数量;

11、结合所述宽度、高度、所述纵向网格线的数量和所述横向网格线的数量,创建所述时钟网格,使所述网格线在芯片核心区域内均匀排布,并将所述纵向网格线和所述横向网格线的交叉点确定为所述网格缓冲单元的位置。

12、在一个具体的可实施方案中,所述基于所述宽度、高度和所述寄存器单元的密度,计算时钟网格对应的网格线的数量包括:

13、根据所述寄存器单元的密度和预设参数计算网格线的间距;

14、结合所述宽度和所述间距计算纵向的所述网格线的数量;

15、结合所述高度和所述间距计算横向的所述网格线的数量。

16、在一个具体的可实施方案中,所述基于所述寄存器单元与所述时钟网格中网格线的距离和所述网格缓冲单元的负载,对所述寄存器单元分组包括:

17、以网格缓冲单元所在位置为中心,所述间距为边长划分每个网格缓冲单元对应的矩形区域,对所述寄存器单元进行快速分组,得到若干寄存器组;

18、计算每个矩形区域内寄存器的数量,对所述寄存器数量超过预设阈值的矩形区域进行调整,使网格缓冲单元的负载在预设范围之内。

19、在一个具体的可实施方案中,所述在所述时钟网格结构的基础上,规划并构建h型时钟树结构包括:

20、将所述时钟网格结构中纵向网格线和横向网格线的交叉点确定为h底层子结构的端点;

21、将每四个相邻的所述h底层子结构的端点进行连接,获得若干个h底层子结构;

22、将若干个所述h底层子结构确定为h型时钟树的底层;

23、基于所述h型时钟树的底层和字母h的形状结构,向上逐级构建h型时钟树,直至构建到最顶层。

24、在一个具体的可实施方案中,所述基于所述h型时钟树的底层和字母h的形状结构,向上逐级构建h型时钟树,直至构建到最顶层包括:

25、将所述h底层子结构的中心点确定为h次底层子结构的端点;

26、将每四个相邻的所述h次底层子结构端点进行连接,获得若干个h次底层子结构;

27、再次将所述h次底层子结构的中心点确定为h次次底层子结构的端点,直至构建到最顶层。

28、在一个具体的可实施方案中,在所述将所述混合时钟树结构转换为电路网表之后,还包括:

29、对所述电路网表进行电路仿真,获取仿真结果数据;

30、判断所述仿真结果数据是否满足预设的约束要求;

31、若不满足,则修改网格线间距、调整寄存器的分组或改变局部布线策略,重新进行所述混合时钟树的构建。

32、第二方面,本技术提供一种时钟树结构设计装置,采用如下技术方案:所述装置包括:

33、时钟网格创建模块,用于根据芯片核心区域内所述寄存器单元的密度,规划并创建时钟网格结构;

34、寄存器组划分模块,用于基于所述寄存器单元与所述时钟网格中网格线的距离和所述网格缓冲单元的负载,对所述寄存器单元分组,获得若干寄存器组;并根据所述寄存器组中寄存器单元的数量确定所述寄存器组对应的网格缓冲单元的驱动力大小;

35、局部布线模块,用于按照就近原则或时钟平衡原则,确定所述寄存器单元到所述网格线的连接线路;

36、h时钟树构建模块,用于在所述时钟网格结构的基础上,规划并构建h型时钟树结构;

37、电路网表转换模块,用于将所述时钟网格结构和所述h型时钟树结构共同组成的结构确定为混合时钟树结构,并将所述混合时钟树结构转换为电路网表。

38、第三方面,本技术提供一种计算机设备,采用如下技术方案:包括存储器和处理器,所述存储器上存储有能够被处理器加载并执行如上述任一种混合时钟树结构设计方法的计算机程序。

39、第四方面,本技术提供一种计算机可读存储介质,采用如下技术方案:存储有能够被处理器加载并执行上述任一种混合时钟树结构设计方法的计算机程序。

40、综上所述,本技术具有以下有益技术效果:

41、1、本发明在时钟树的上层充分利用了h型时钟树的高度对称特性,在获得较小时钟偏差的同时保证较低的时钟延迟;在时钟树的底层利用时钟网格结构,缓解了寄存器分布不平衡时底层缓冲器与寄存器互连线的长度偏差问题,同时时钟网格的冗余特性减小了工艺不确定性带来的影响,提高芯片的良率和稳定性;

42、2、本发明中影响时钟偏差、传播延迟和时钟信号过渡时间等指标的关键在于时钟网格大小的设计、寄存器的分组方式和局部布线的策略;采用自下而上的手动设计方式,可以快速地修改设计方案,在不同的设计策略之间灵活地转换;

43、3、本发明提出的一种混合时钟树结构及其定制化实现方案,在时钟偏差与面积功耗之间达到平衡,并且具有良好的适用性和抗干扰能力,与传统的技术方案相比具有明显的优越性。

- 还没有人留言评论。精彩留言会获得点赞!