现场可编程门阵列电路的制作方法

本申请的所公开实施例涉及fpga,且更具体而言,涉及现场可编程门阵列电路。

背景技术:

1、现场可编程门阵列(field program gate array,fpga)是一种支持重复编程的集成电路,但是,由于其一般不具备存储介质,需要外扩存储芯片。

2、通常,在fpga芯片上外扩存储芯片后,通过控制器控制存储芯片中的程序下载或更新,然后fpga再自动运行存储芯片中的程序,但是,外扩的存储芯片中的程序下载或更新会受到fpga上的管脚电平的影响,从而导致程序下载或更新成功率降低。

3、于是,为了解决现有技术中存在的程序下载或更新成功率低的问题,提出本申请。

技术实现思路

1、根据本申请的实施例,本申请提出一种现场可编程门阵列电路,以解决现有技术中存在的程序下载或更新成功率的问题。

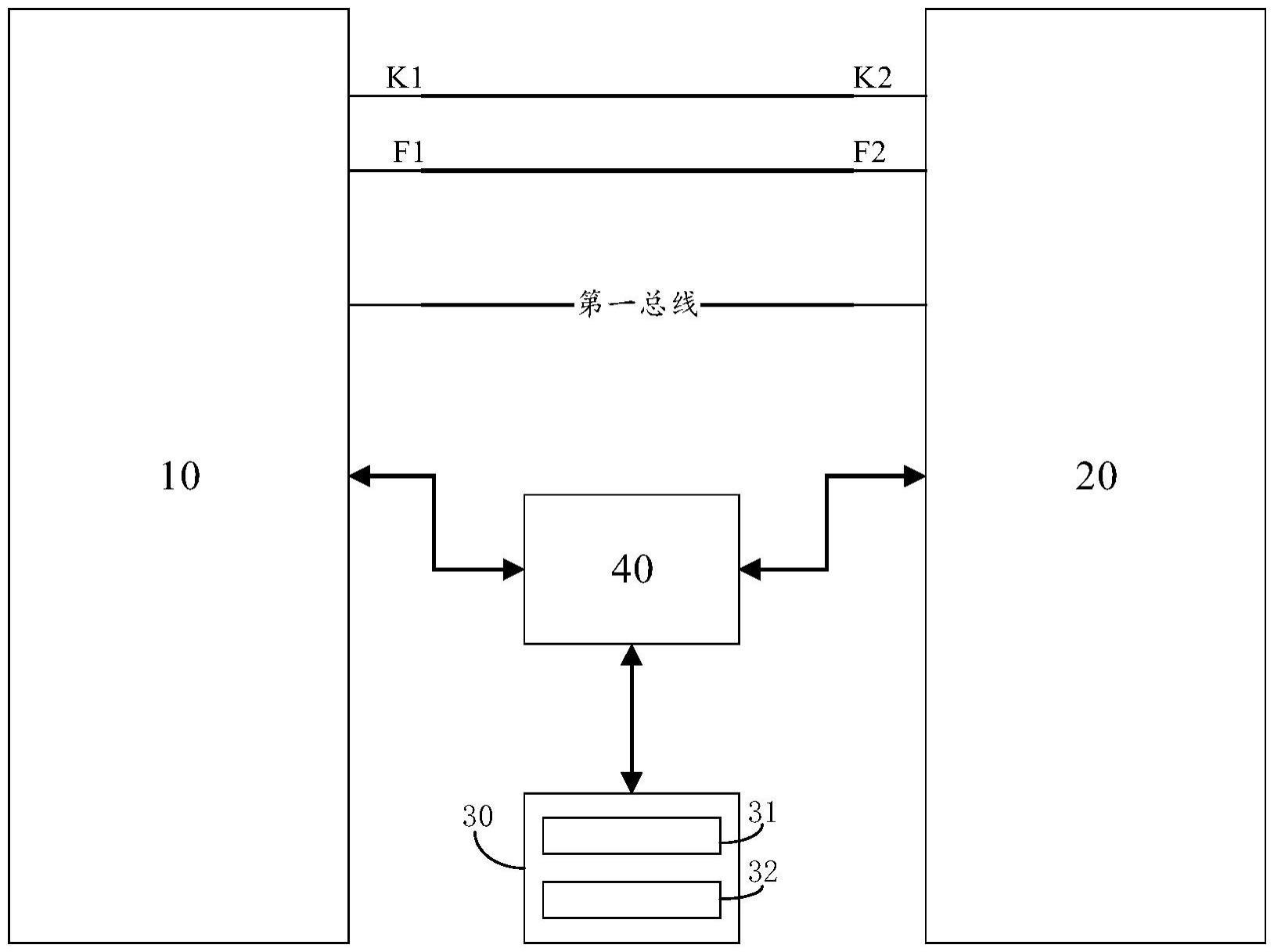

2、本申请公开一种现场可编程门阵列电路,包括:控制器、fpga芯片、存储芯片以及切换器;存储芯片用于存储控制程序;切换器连接至所述控制器、所述fpga芯片和所述存储芯片,其中,所述fpga芯片通过所述切换器连接至所述存储芯片;其中,在所述控制程序下载或更新阶段,所述控制器控制所述切换器将所述存储芯片连接至所述控制器以下载或更新所述控制程序;在默认阶段,所述控制器控制所述切换器将所述存储芯片连接至所述fpga芯片以使所述fpga芯片自动加载所述控制程序进行运行。

3、上述方案,通过在fpga芯片外设存储芯片,通过切换器切换存储芯片与fpga芯片和控制器之间的连接关系,且fpga芯片与存储芯片不直接连接,因此,存储芯片在进行程序下载或更新时不受fpga芯片上管脚电平的影响,从而能够提高程序下载或更新的成功率。

4、其中,所述控制器包括第一控制引脚,所述fpga芯片包括第二控制引脚,其中,所述控制器的第一控制引脚连接所述fpga芯片的所述第二控制引脚;响应于所述fpga电路工作在所述默认阶段,所述控制器通过所述第一控制引脚使所述fpga芯片的所述第二控制引脚工作在第一状态,所述fpga芯片从所述存储芯片中加载所述控制程序。

5、上述方案,控制器通过第一控制引脚连接至fpga芯片的第二控制引脚,以在fpga芯片在默认阶段下能够自动加载控制程序并运行,进而提高效率。

6、其中,所述第一状态为逻辑低电平状态。

7、其中,所述控制器包括第一反馈引脚,所述fpga芯片包括第二反馈引脚,其中,所述控制器的所述第一反馈引脚连接所述fpga芯片的所述第二反馈引脚;响应于所述fpga电路工作在所述默认阶段,所述控制器基于所述第一反馈引脚上的反馈信号确定所述fpga芯片是否加载所述控制程序的加载状态。

8、上述方案,通过控制器的第一反馈引脚与fpga芯片的第二反馈引脚连接,fpga芯片能够向控制器反馈控制程序的加载状态,进一步提高效率。

9、其中,响应于所述第一反馈引脚上的所述反馈信号处于第一工作电平时,所述控制器确定所述fpga芯片成功加载所述控制程序;响应于所述第一反馈引脚上的所述反馈信号处于第二工作电平时,所述控制器确定所述fpga芯片未成功加载所述控制程序。

10、其中,所述第一工作电平为逻辑高电平;所述第二工作电平为逻辑低电平。

11、其中,所述存储芯片包括第一存储单元和第二存储单元,所述第一存储单元用于存储备份控制程序,所述第二存储单元用于存储应用控制程序。

12、上述方案,存储芯片中存储不同的程序,在程序下载或更新失败后fpga芯片仍然能够加载备份控制程序实现正常运行,避免由于程序下载或更新失败导致系统无法正常运行,从而进一步提高效率。

13、其中,所述备份控制程序为进行所述程序下载或更新阶段前未下载或更新的控制程序;所述应用控制程序为进行所述程序下载或更新阶段后已下载或更新的控制程序。

14、上述方案,存储芯片中存储不同的程序,在程序下载或更新失败后fpga芯片仍然能够加载备份控制程序实现正常运行,避免由于程序下载或更新失败导致系统无法正常运行,从而进一步提高效率。

15、其中,所述切换器包括切换芯片和施密特触发器,所述切换芯片连接至所述控制器、fpga芯片和存储芯片,所述切换芯片还通过所述施密特触发器连接至所述控制器。

16、其中,所述切换芯片还包括第一使能引脚和第二使能引脚,所述控制器还包括第三控制引脚;所述第一使能引脚经过所述施密特触发器连接至所述控制器的第三控制引脚,所述第二使能引脚连接至所述控制器的第三控制引脚。

技术特征:

1.一种现场可编程门阵列电路,其特征在于,包括:

2.根据权利要求1所述的电路,其特征在于,

3.根据权利要求2所述的电路,其特征在于,

4.根据权利要求1所述的电路,其特征在于,

5.根据权利要求4所述的电路,其特征在于,

6.根据权利要求5所述的电路,其特征在于,

7.根据权利要求1所述的电路,其特征在于,所述存储芯片包括第一存储单元和第二存储单元,所述第一存储单元用于存储备份控制程序,所述第二存储单元用于存储应用控制程序。

8.根据权利要求7所述的电路,其特征在于,所述备份控制程序为进行所述程序下载或更新阶段前未下载或更新的控制程序;所述应用控制程序为进行所述程序下载或更新阶段后已下载或更新的控制程序。

9.根据权利要求1所述的电路,其特征在于,所述切换器包括切换芯片和施密特触发器,所述切换芯片连接至所述控制器、fpga芯片和存储芯片,所述切换芯片还通过所述施密特触发器连接至所述控制器。

10.根据权利要求9所述的电路,其特征在于,所述切换芯片还包括第一使能引脚和第二使能引脚,所述控制器还包括第三控制引脚;所述第一使能引脚经过所述施密特触发器连接至所述控制器的第三控制引脚,所述第二使能引脚连接至所述控制器的第三控制引脚。

技术总结

本申请公开现场可编程门阵列电路,包括:控制器、FPGA芯片、存储芯片以及切换器;存储芯片用于存储控制程序;切换器连接至控制器、FPGA芯片和存储芯片,其中,FPGA芯片通过切换器连接至存储芯片;其中,在控制程序下载或更新阶段,控制器控制切换器将存储芯片连接至控制器以下载或更新控制程序;在默认阶段,控制器控制切换器将存储芯片连接至FPGA芯片以使FPGA芯片自动加载控制程序进行运行。上述方案,通过在FPGA芯片外设存储芯片,通过切换器切换存储芯片与FPGA芯片和控制器之间的连接关系,且FPGA芯片与存储芯片不直接连接,因此,存储芯片在进行程序下载或更新时不受FPGA芯片上管脚电平的影响,从而能够提高程序下载或更新的成功率。

技术研发人员:鲁通

受保护的技术使用者:苏州时代新安能源科技有限公司

技术研发日:20230210

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!