一种任意多通道复用处理器的制作方法

本技术涉及到电子电路,具体涉及到一种任意多通道复用处理器。

背景技术:

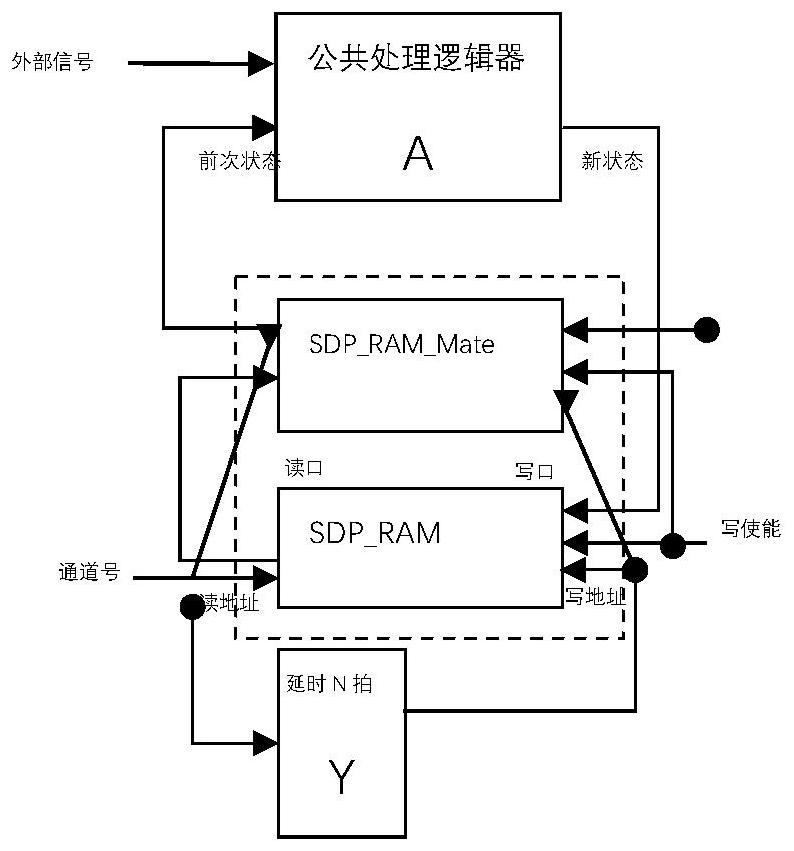

1、多通道复用处理是电路设计或者芯片设计中经常要用到的技术,它用相同的逻辑资源来分时处理不同通道的任务,它的好处是节省逻辑资源,通道数量越多,节省逻辑资源越多。多通道复用处理电路基本由公共处理逻辑和sdp_ram(简单双口随机访问存储器)组成。公共处理逻辑通常是纯组合逻辑,在1个时钟周期(也称1拍)内完成,这里它不是我们要讨论和关注的部分。sdp_ram(简单双口随机访问存储器)包含一个写口和一个读口。通道号作为读地址,延时n拍后读出前次状态,前次状态和外部信号经过公共处理逻辑后产生新状态,通过写口写入。为了使通道对齐,通道号延时n拍后作为写地址。假设sdp_ram(简单双口随机访问存储器)读出延时为n(大于等于0),写入延时为m(大于等于1),同一通道号的最小间隔为d(大于等于1),则电路能正常工作的条件是d>=(m+n)。

2、但是,在一些应用中,系统要求d等于1(即同一通道号可以在任意时刻出现,通道复用关系完全没有任何限制),而m+n又大于1的情况(一般是通道数量过大,或者(和)时钟频率很高,m+n等于1不能满足时序指标),此时则不能满足需求。

技术实现思路

1、为了解决以上现有技术的不足,本实用新型的目的在于提供一种任意多通道复用处理器,可实现同一通道号可以在任意时刻出现,通道复用关系完全没有任何限制的复用处理器,即解决背景技术中d等于1而m+n又大于1的情况。

2、本实用新型采用的技术方案如下:一种任意多通道复用处理器,包括公共处理逻辑器、简单双口随机访问存储器和延时器;还包括简单双口随机存储器伴随模块;所述公共处理逻辑器和简单双口随机访问存储器之间信号连接,所述简单双口随机访问存储器和简单双口随机存储器伴随模块之间信号连接,所述公共处理逻辑器还连接有外部信号,所述简单双口随机访问存储器和简单双口随机存储器伴随模块均连接有写使能信号和通道号信号,所述通道号信号还通过延时器与公共处理逻辑器信号连接;所述简单双口随机存储器伴随模块包括数据选择器,与数据选择器连接的输入移位寄存器和复用控制器,所述数据选择器与简单双口随机访问存储器的读数据连接,输入移位寄存器的输入与简单双口随机访问存储器的写数据连接,数据选择器的输出作为简单双口随机存储器伴随模块的输出与公共处理逻辑器连接,所述复用控制器连接有简单双口随机访问存储器的写使能信号、写地址信号和读地址信号;

3、进一步的,数据选择器采用四选一数据选择器,所述四选一数据选择器连接有三路输入移位寄存器,分别记为第一移位寄存器、第二移位寄存器和第三移位寄存器,且第一移位寄存器的输出作为四选一数据选择器和第二移位寄存器的输入,第二移位寄存器的输出作为四选一数据选择器和第三移位寄存器的输入,第三移位寄存器的输出作为四选一数据选择器的输入;简单双口随机访问存储器的读数据信号作为四选一数据选择器的输入。

4、进一步的,数据选择器采用四选一数据选择器,所述四选一数据选择器的输出还连接有输出寄存器,输出寄存器的输出作为简单双口随机存储器伴随模块的输出;所述四选一数据选择器连接有两路输入移位寄存器,分别记为第一移位寄存器和第二移位寄存器;所述四选一数据选择器还连接有简单双口随机访问存储器的读数据信号和写数据信号,其中简单双口随机访问存储器的写数据信号作为第一移位寄存器的输入,第一移位寄存器的输出分别与四选一数据选择器和第二移位寄存器连接,作为四选一数据选择器和第二移位寄存器的输入,第一移位寄存器的输出与四选一数据选择器连接,作为四选一数据选择器输。

5、有益效果:本实用新型提供的一种任意多通道复用处理器,在电路中增加一个简单双口随机存储器伴随模块,简单双口随机访问存储器的全部输入及输出都连接到简单双口随机存储器伴随模块,作为简单双口随机存储器伴随模块的输入信号,简单双口随机存储器伴随模块的输出信号取代简单双口随机访问存储器模块读数据,作为新的读数据(前次状态)输入到公共处理逻辑部分。如果把简单双口随机存储器伴随模块和简单双口随机访问存储器两个模块包封成一个新的模块(可命名为sdp_ram_s),则sdp_ram_s和简单双口随机访问存储器输入输出信号完全一样,这样的设计便于现存设计的升级替换,只需要把简单双口随机访问存储器替换成sdp_ram_s即可,大大节省工作量。

技术特征:

1.一种任意多通道复用处理器,包括公共处理逻辑器、简单双口随机访问存储器和延时器,其特征在于:还包括简单双口随机存储器伴随模块;所述公共处理逻辑器和简单双口随机访问存储器之间信号连接,所述简单双口随机访问存储器和简单双口随机存储器伴随模块之间信号连接,所述公共处理逻辑器还连接有外部信号,所述简单双口随机访问存储器和简单双口随机存储器伴随模块均连接有写使能信号和通道号信号,所述通道号信号还通过延时器与公共处理逻辑器信号连接;所述简单双口随机存储器伴随模块包括数据选择器,与数据选择器连接的输入移位寄存器和复用控制器,所述数据选择器与简单双口随机访问存储器的读数据连接,输入移位寄存器的输入与简单双口随机访问存储器的写数据连接,数据选择器的输出作为简单双口随机存储器伴随模块的输出与公共处理逻辑器连接,所述复用控制器连接有简单双口随机访问存储器的写使能信号、写地址信号和读地址信号。

2.根据权利要求1所述的一种任意多通道复用处理器,其特征在于:所述数据选择器采用四选一数据选择器,所述四选一数据选择器连接有三路输入移位寄存器,分别记为第一移位寄存器、第二移位寄存器和第三移位寄存器,且第一移位寄存器的输出作为四选一数据选择器和第二移位寄存器的输入,第二移位寄存器的输出作为四选一数据选择器和第三移位寄存器的输入,第三移位寄存器的输出作为四选一数据选择器的输入;简单双口随机访问存储器的读数据信号作为四选一数据选择器的输入。

3.根据权利要求1所述的一种任意多通道复用处理器,其特征在于:所述数据选择器采用四选一数据选择器,所述四选一数据选择器的输出还连接有输出寄存器,输出寄存器的输出作为简单双口随机存储器伴随模块的输出;所述四选一数据选择器连接有两路输入移位寄存器,分别记为第一移位寄存器和第二移位寄存器;所述四选一数据选择器还连接有简单双口随机访问存储器的读数据信号和写数据信号,其中简单双口随机访问存储器的写数据信号作为第一移位寄存器的输入,第一移位寄存器的输出分别与四选一数据选择器和第二移位寄存器连接,作为四选一数据选择器和第二移位寄存器的输入,第一移位寄存器的输出与四选一数据选择器连接,作为四选一数据选择器输入。

技术总结

本技术涉及到电子电路技术领域,具体涉及到一种任意多通道复用处理器。通过在电路中增加一个简单双口随机存储器伴随模块,简单双口随机访问存储器的全部输入及输出都连接到简单双口随机存储器伴随模块,作为简单双口随机存储器伴随模块的输入信号,简单双口随机存储器伴随模块的输出信号取代简单双口随机访问存储器模块读数据,作为新的读数据(前次状态)输入到公共处理逻辑部分。若把简单双口随机存储器伴随模块和简单双口随机访问存储器两个模块包封成一个新的模块(可命名为SDP_RAM_S),则SDP_RAM_S和简单双口随机访问存储器输入输出信号完全一样,这样的设计便于现存设计的升级替换,只需要把简单双口随机访问存储器替换成SDP_RAM_S即可,大大节省工作量。

技术研发人员:匡启成

受保护的技术使用者:四川辉电启明智能科技有限公司

技术研发日:20230424

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!