多时钟并行装置及芯片测试机的制作方法

本申请属于芯片自动化测试,具体涉及一种多时钟并行装置及芯片测试机。

背景技术:

1、芯片测试,指的是利用自动测试设备(automatic test equipment,ate)对被测器件(device under test,dut)的各项参数指标进行检测,剔除残次品以控制芯片的出厂品质。

2、在芯片自动化测试中的时钟是非常重要的一个参数,关乎整个测试机的运行,时钟异常可能会导致多种问题。

3、现有技术中,芯片自动化测试设备都是采用单时钟。依靠单时钟分开在模块中使用,而没有贯穿整个模块,那么进行时钟同步就是非常困难,并且还需要进行逐一排查。

技术实现思路

1、本申请的目的是提供一种多时钟并行装置及芯片测试机以解决测试设备时钟同步困难的问题。

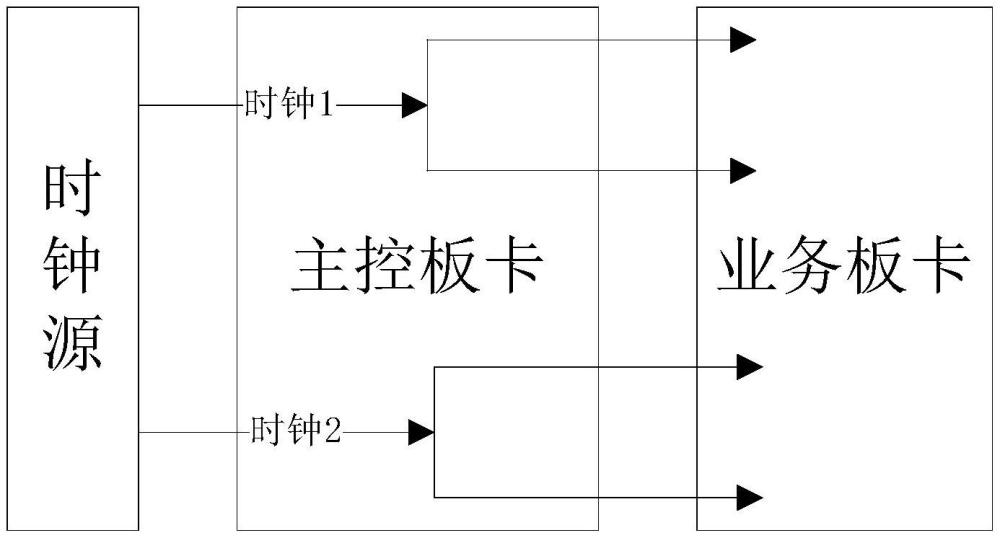

2、根据本申请实施例的第一方面,提供了一种多时钟并行装置,该装置可以包括:

3、时钟源,用于多种时钟控制;

4、主控板卡,与时钟源通信连接,用于将多种时钟引入并分频,形成多个同源时钟;

5、业务板卡,与主控板卡通信连接,用于引入多个同源时钟。

6、在本申请的一些可选实施例中,主控板卡包括第一主控制单元;业务板卡包括第一业务控制单元和第一业务可编程逻辑器件;

7、第一业务控制单元与第一业务可编程逻辑器件通信连接;

8、第一业务控制单元与第一主控制单元通信连接;

9、第一主控制单元还与时钟源通信连接。

10、在本申请的一些可选实施例中,第一业务控制单元为多个,第一业务可编程逻辑器件为多个,且第一业务控制单元与第一业务可编程逻辑器件一一对应,且通信连接;

11、第一主控制单元用于将时钟源引入的时钟分频后形成多路并经过第一业务控制单元分频后传输至第一业务可编程逻辑器件。

12、在本申请的一些可选实施例中,主控板卡包括晶振、第二主控制单元、匹配单元及第一主可编程逻辑器件;业务板卡包括第二业务可编程逻辑器件;

13、晶振与第二主控制单元通信连接;

14、第二主控制单元与匹配单元通信连接;

15、匹配单元分别与第一主可编程逻辑器件和第二业务可编程逻辑器件通信连接。

16、在本申请的一些可选实施例中,第二业务可编程逻辑器件为多个,多个第二业务可编程逻辑器件均与匹配单元通信连接。

17、在本申请的一些可选实施例中,第一主可编程逻辑器件为多个,多个第一主可编程逻辑器件均与匹配单元通信连接。

18、在本申请的一些可选实施例中,主控板卡包括第三主控制单元、第四主控制单元及第二主可编程逻辑器件;业务板卡包括第二业务控制单元和第三业务可编程逻辑器件;

19、第三主控制单元分别与第四主控制单元和第二业务控制单元通信连接;

20、第四主控制单元与第二主可编程逻辑器件通信连接;

21、第二业务控制单元与第三业务可编程逻辑器件通信连接。

22、在本申请的一些可选实施例中,第二业务控制单元为多个,第三业务可编程逻辑器件为多个;

23、多个第三业务可编程逻辑器件中每个第三业务可编程逻辑器件均分别与多个第二业务控制单元中每个第二业务控制单元通信连接。

24、在本申请的一些可选实施例中,第四主控制单元为多个,第二主可编程逻辑器件为多个;

25、多个第四主控制单元与多个第二主可编程逻辑器件一一对应,且通信连接。

26、根据本申请实施例的第一方面,提供了一种芯片测试机,该测试机包括第一方面任一项实施例所示的多时钟并行装置。

27、本申请的上述技术方案具有如下有益的技术效果:

28、本申请实施例装置通过利用主控板卡将时钟源提供的多种时钟引入并分频形成多个同源时钟,业务板卡引入其中多个同源时钟,以使时钟贯穿整个装置,这样装置的各个部分时钟同源,一致性较高,参数便于调整。并且该装置采用多时钟并行,相对于单时钟的装置,极大提高芯片测试机的测试效率。

技术特征:

1.一种多时钟并行装置,其特征在于,包括:

2.根据权利要求1所述的多时钟并行装置,其特征在于,所述主控板卡包括第一主控制单元;所述业务板卡包括第一业务控制单元和第一业务可编程逻辑器件;

3.根据权利要求2所述的多时钟并行装置,其特征在于,所述第一业务控制单元为多个,所述第一业务可编程逻辑器件为多个,且所述第一业务控制单元与所述第一业务可编程逻辑器件一一对应,且通信连接;

4.根据权利要求1所述的多时钟并行装置,其特征在于,所述主控板卡包括晶振、第二主控制单元、匹配单元及第一主可编程逻辑器件;所述业务板卡包括第二业务可编程逻辑器件;

5.根据权利要求4所述的多时钟并行装置,其特征在于,所述第二业务可编程逻辑器件为多个,多个所述第二业务可编程逻辑器件均与所述匹配单元通信连接。

6.根据权利要求4所述的多时钟并行装置,其特征在于,所述第一主可编程逻辑器件为多个,多个所述第一主可编程逻辑器件均与所述匹配单元通信连接。

7.根据权利要求1所述的多时钟并行装置,其特征在于,所述主控板卡包括第三主控制单元、第四主控制单元及第二主可编程逻辑器件;所述业务板卡包括第二业务控制单元和第三业务可编程逻辑器件;

8.根据权利要求7所述的多时钟并行装置,其特征在于,所述第二业务控制单元为多个,所述第三业务可编程逻辑器件为多个;

9.根据权利要求7所述的多时钟并行装置,其特征在于,所述第四主控制单元为多个,所述第二主可编程逻辑器件为多个;

10.一种芯片测试机,其特征在于,包括权利要求1-9任一项所述的多时钟并行装置。

技术总结

本申请公开了一种多时钟并行装置及芯片测试机,属于芯片测试技术领域,其中,多时钟并行装置包括:时钟源,用于多种时钟控制;主控板卡,与时钟源通信连接,用于将多种时钟引入并分频,形成多个同源时钟;业务板卡,与主控板卡通信连接,用于引入多个同源时钟。该装置通过利用主控板卡将时钟源的多种时钟引入并分频形成多个同源时钟,业务板卡引入其中多个同源时钟,以使时钟贯穿整个装置,这样装置的各个部分时钟同源,一致性较高,参数便于调整。并且该装置采用多时钟并行,相对于单时钟的装置,极大提高芯片测试机的测试效率。

技术研发人员:蔡定芸,赵川,杨强,刘婷,姚琦

受保护的技术使用者:杭州长川科技股份有限公司

技术研发日:20230615

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!