一种基于FMC多通道同步采集的新型子卡电路的制作方法

本技术属于fmc多通道采集,具体涉及一种基于fmc多通道同步采集的新型子卡电路。

背景技术:

1、多处理器片上系统mpsoc由多个不同的处理器元件组成。现有的mpsoc(与mpsoc一个概念)芯片在通过fmc子板进行采集时,大多数都是单通道进行采集,在面对多个采集对象时,无法进行同时采集,从而具有效率低等缺点。

2、因此,针对上述问题,予以进一步改进。

技术实现思路

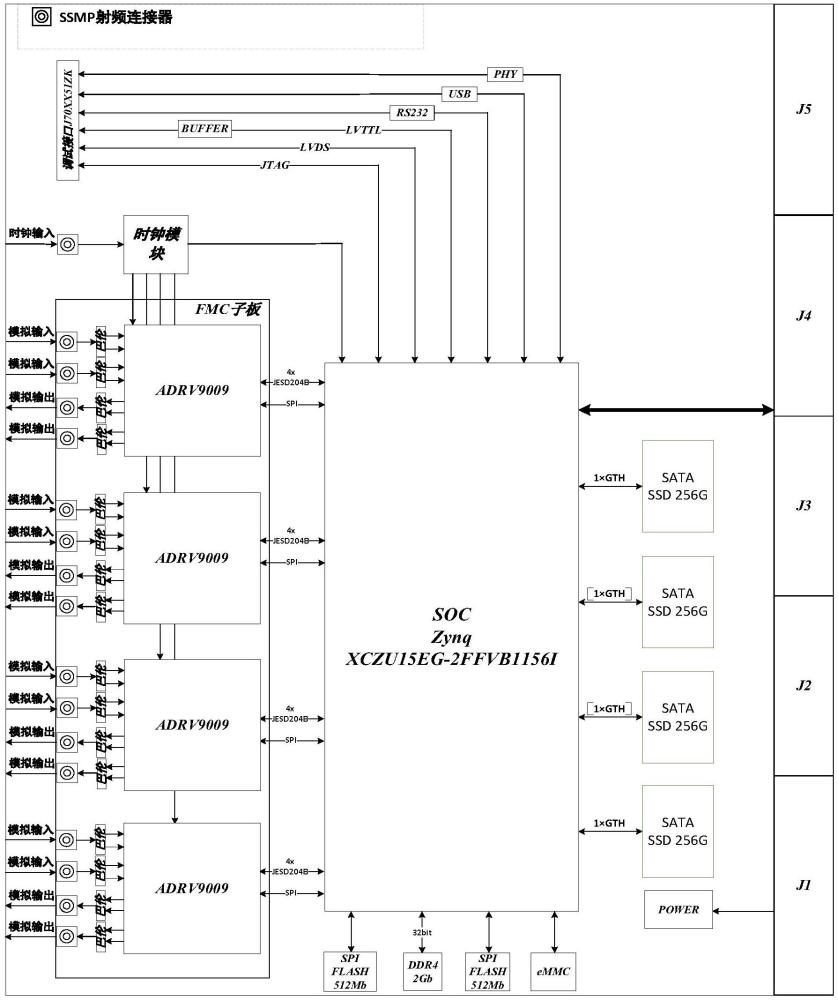

1、本实用新型的主要目的在于提供一种基于fmc多通道同步采集的新型子卡电路,其通过数据处理单元、数据存储单元、射频收发单元、时钟分配单元和电源功能单元进行联动,以使得soc芯片可以通过fmc子板进行多通道同时采集,进而提高采集效率。

2、为达到以上目的,本实用新型提供一种基于fmc多通道同步采集的新型子卡电路,包括数据处理单元、数据存储单元、射频收发单元、时钟分配单元和电源功能单元,其中:

3、所述处理单元包括soc芯片;

4、所述数据存储单元包括第一固态硬盘(sata ssd)、第二固态硬盘、第三固态硬盘和第四固态硬盘,所述第一固态硬盘、所述第二固态硬盘、所述第三固态硬盘和所述第四固态硬盘均与所述soc芯片电性连接;

5、所述射频收发单元包括第一收发器、第二收发器、第三收发器和第四收发器,所述第一收发器、所述第二收发器、所述第三收发器和所述第四收发器分别与所述soc芯片电性连接并且均通过巴伦设有两路模拟输入和两路模拟输出;

6、所述时钟分配单元包括soc时钟和收发器时钟,所述soc时钟与所述soc芯片电性连接并且所述收发器时钟与所述射频收发单元电性连接,所述soc时钟包括工作时钟、ddr4参考时钟和gth参考时钟;

7、所述电源功能单元分别与所述数据处理单元、所述数据存储单元、所述射频收发单元和所述时钟分配单元电性连接(用于供电)。

8、作为上述技术方案的进一步优选的技术方案,基于fmc多通道同步采集的新型子卡电路还包括调试接口,其中:

9、所述soc芯片通过rgmii接口连接到phy芯片并且所述phy芯片与所述调试接口连接;

10、所述soc芯片通过usb与所述调试接口连接;

11、所述soc芯片通过rs232与所述调试接口连接;

12、所述soc芯片分别通过lvttl、lvds和jtag与所述调试接口连接。

13、作为上述技术方案的进一步优选的技术方案,所述soc芯片还分别与flash芯片、ddr4存储器和emmc存储器电性连接。

14、作为上述技术方案的进一步优选的技术方案,所述soc芯片通过jesd204b与所述射频收发单元电性连接。

15、作为上述技术方案的进一步优选的技术方案,模拟输入和模拟输出均采用射频连接器。

技术特征:

1.一种基于fmc多通道同步采集的新型子卡电路,其特征在于,包括数据处理单元、数据存储单元、射频收发单元、时钟分配单元和电源功能单元,其中:

2.根据权利要求1所述的一种基于fmc多通道同步采集的新型子卡电路,其特征在于,基于fmc多通道同步采集的新型子卡电路还包括调试接口,其中:

3.根据权利要求2所述的一种基于fmc多通道同步采集的新型子卡电路,其特征在于,所述soc芯片还分别与flash芯片、ddr4存储器和emmc存储器电性连接。

4.根据权利要求3所述的一种基于fmc多通道同步采集的新型子卡电路,其特征在于,所述soc芯片通过jesd204b与所述射频收发单元电性连接。

5.根据权利要求4所述的一种基于fmc多通道同步采集的新型子卡电路,其特征在于,模拟输入和模拟输出均采用射频连接器。

技术总结

本技术公开了一种基于FMC多通道同步采集的新型子卡电路,包括数据处理单元、数据存储单元、射频收发单元、时钟分配单元和电源功能单元,所述处理单元包括SOC芯片;所述数据存储单元包括第一固态硬盘、第二固态硬盘、第三固态硬盘和第四固态硬盘,所述第一固态硬盘、所述第二固态硬盘、所述第三固态硬盘和所述第四固态硬盘均与所述SOC芯片电性连接。本技术公开的一种基于FMC多通道同步采集的新型子卡电路,其通过数据处理单元、数据存储单元、射频收发单元、时钟分配单元和电源功能单元进行联动,以使得SOC芯片可以通过FMC子板进行多通道同时采集,进而提高采集效率。

技术研发人员:张峻涛,王文勇,邵乐天

受保护的技术使用者:浙江天泓波控电子科技有限公司

技术研发日:20230828

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!