总线的超时检测电路、方法、芯片及电子设备与流程

本发明涉及电路领域,具体涉及总线的超时检测电路、方法、芯片及电子设备。

背景技术:

1、总线是soc芯片中的重要组成部分,其是cpu与其他设备(器件)的交互通道。当从设备的配置或连接出现永久或短暂失效时,从设备可能无法及时对主设备发出的读写传输进行响应,进而导致传输丢失或总线挂死,这种情况下即总线超时。

2、为了检测总线超时,现有技术提出了不少解决方案,但是现有的检测方案存在不足。

技术实现思路

1、基于上述现状,本发明的主要目的在于提供总线的超时检测电路、方法、芯片及电子设备,以相对简单的电路实现对复杂目标总线的超时检测。

2、为实现上述目的,本发明采用的技术方案如下:

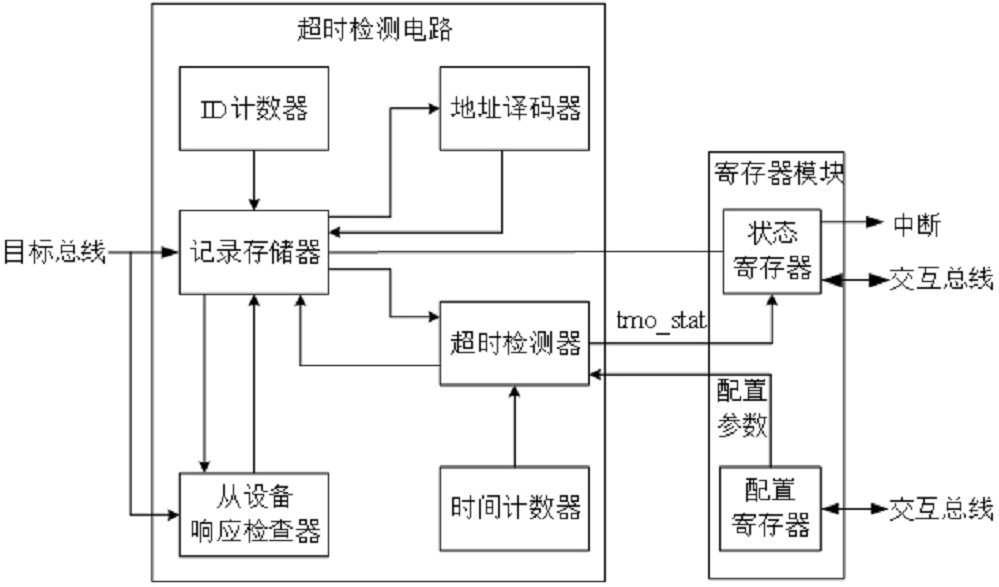

3、一种总线的超时检测电路,包括记录存储器和超时检测器,还包括时间计数器;所述记录存储器包括具有相同序号的状态存储区、id存储区、计数存储区和顺序存储区;所述状态存储区、id存储区、计数存储区和顺序存储区包括k个具有各自序号的状态存储单元、id存储单元、计数存储单元和顺序存储单元;其中,k为大于1的整数;所述时间计数器在时钟驱动下持续产生计数值;当目标总线上出现操作请求时,执行如下操作:将所述状态存储区中状态标志为无效的状态存储单元作为当前状态存储单元,将所述当前状态存储单元的状态标志修改为有效,将所述当前状态存储单元的序号作为当前序号;从所述操作请求中获取当前id,将所述当前id写入所述当前序号的id存储单元;从所述时间计数器读取当前的计数值,写入所述当前序号的计数存储单元;从所述id存储区统计所述当前id出现的总次数,将所述总次数写入所述当前序号的顺序存储单元;所述超时检测器按照设定频率执行如下操作:从所述时间计数器读取检测时刻的计数值,从所述顺序存储区读取次数值为1所对应的所有序号作为目标序号,并计算所述目标序号的计数存储单元中的计数值与检测时刻的计数值之间的计数变化量,将所述计数变化量大于计数阈值的目标序号对应的操作请求判定为超时。

4、优选的,所述记录存储器还包括与状态存储区具有相同序号的超时存储区,所述超时存储区包括k个具有各自序号的超时存储单元;所述超时检测器还将所述计数变化量小于所述计数阈值的目标序号对应的操作请求判定为未超时,将未超时对应的所述目标序号的超时存储单元的超时标志置为未超时;所述超时检测器将超时对应的所述目标序号的超时存储单元的超时标志置为超时,并将超时对应的所述目标序号的状态存储单元、id存储单元、计数存储单元和顺序存储单元清零。

5、优选的,所述的超时检测电路还包括从设备响应检查器,当目标总线上出现操作请求响应时,所述从设备响应检查器执行如下操作:从所述操作请求响应中获取响应id,从所述id存储区中查找与所述响应id相同的id所对应的序号作为可能序号,在所述可能序号的顺序存储单元中查找次数值为1所对应的序号作为响应序号,将所述响应序号对应的状态存储单元、id存储单元、计数存储单元和顺序存储单元清零,在所述可能序号的顺序存储单元中,将次数值大于1的次数值减1,作为更新的次数值。

6、优选的,所述记录存储器还包括与状态存储区具有相同序号的地址存储区,所述地址存储区包括k个具有各自序号的地址存储单元;当目标总线上出现操作请求时,所述记录存储器还执行如下操作:从所述操作请求中获取当前地址,将所述当前地址写入所述当前序号的地址存储单元;所述超时检测器还按照设定频率执行如下操作:当所述目标序号的超时存储单元的超时标志置为超时,将所述目标序号的地址存储单元中的地址锁存。

7、优选的,所述超时检测器在超时的超时标志的触发下,将寄存器模块中的超时中断标志置为有效;cpu根据所述寄存器模块中有效的超时中断标志执行预设操作后,将所述超时中断标志置为无效。

8、优选的,所述超时检测器在将寄存器模块中的超时中断标志置为有效后的设定数量个时钟周期到来时,将超时的超时标志置为未超时。

9、优选的,所述的超时检测电路还包括地址译码器,所述地址译码器从所述状态存储区中查找状态标志为无效的状态存储单元的序号输出至所述记录存储器。

10、优选的,所述的超时检测电路还包括id计数器,所述id计数器用于从所述id存储区统计所述当前id出现的总次数,写入所述当前序号的顺序存储单元。

11、优选的,所述cpu根据所述从交互总线向所述超时检测器写入所述计数阈值。

12、本发明还提供了一种总线的超时检测电路的超时检测方法,所述总线的超时检测电路包括记录存储器,所述记录存储器包括具有相同序号的状态存储区、id存储区、计数存储区和顺序存储区;所述状态存储区、id存储区、计数存储区和顺序存储区包括k个具有各自序号的状态存储单元、id存储单元、计数存储单元和顺序存储单元;其中,k为大于1的整数;所述超时检测方法包括如下步骤:在时钟驱动下持续产生计数值;当目标总线上出现操作请求时,执行如下操作:将所述状态存储区中状态标志为无效的状态存储单元作为当前状态存储单元,将所述当前状态存储单元的状态标志修改为有效,将所述当前状态存储单元的序号作为当前序号;从所述操作请求中获取当前id,将所述当前id写入所述当前序号的id存储单元;从所述时间计数器读取当前的计数值,写入所述当前序号的计数存储单元;从所述id存储区统计所述当前id出现的总次数,将所述总次数写入所述当前序号的顺序存储单元;按照设定频率执行如下操作:从所述时间计数器读取检测时刻的计数值,从所述顺序存储区读取次数值为1所对应的所有序号作为目标序号,并计算所述目标序号的计数存储单元中的计数值与检测时刻的计数值之间的计数变化量,将所述计数变化量大于计数阈值的目标序号对应的操作请求判定为超时。

13、优选的,所述记录存储器还包括与状态存储区具有相同序号的超时存储区,所述超时存储区包括k个具有各自序号的超时存储单元;所述超时检测方法还包括如下步骤:将所述计数变化量小于所述计数阈值的目标序号对应的操作请求判定为未超时,将未超时对应的所述目标序号的超时存储单元的超时标志置为未超时;将超时对应的所述目标序号的超时存储单元的超时标志置为超时,并将超时对应的所述目标序号的状态存储单元、id存储单元、计数存储单元和顺序存储单元清零。

14、优选的,当目标总线上出现操作请求响应时,执行如下操作:从所述操作请求响应中获取响应id,从所述id存储区中查找与所述响应id相同的id所对应的序号作为可能序号,在所述可能序号的顺序存储单元中查找次数值为1所对应的序号作为响应序号,将所述响应序号对应的状态存储单元、id存储单元、计数存储单元和顺序存储单元清零,在所述可能序号的顺序存储单元中,将次数值大于1的次数值减1,作为更新的次数值。

15、优选的,所述记录存储器还包括与状态存储区具有相同序号的地址存储区,所述地址存储区包括k个具有各自序号的地址存储单元;所述的超时检测方法还包括如下步骤:当目标总线上出现操作请求时,还执行如下操作:从所述操作请求中获取当前地址,将所述当前地址写入所述当前序号的地址存储单元;还按照设定频率执行如下操作:当所述目标序号的超时存储单元的超时标志置为超时,将所述目标序号的地址存储单元中的地址锁存。

16、优选的,在超时的超时标志的触发下,将寄存器模块中的超时中断标志置为有效;cpu根据所述寄存器模块中有效的超时中断标志执行预设操作后,将所述超时中断标志置为无效。

17、本发明还提供了一种芯片,包括任一所述的超时检测电路。

18、本发明还提供了一种电子设备,包括所述的芯片。

19、在上述方案中,具有各自序号的状态存储单元中的状态标志表示对应序号下的相关存储区的存储单元是否有效存储了某个操作请求的相关内容,id存储单元存储对应序号下的操作请求的id,计数存储单元对应序号下的操作请求被检测到时时间计数器的计数值,顺序存储单元存储对应序号下操作请求中的id截至当前出现的次数值,通过判断次数值1的操作请求是否超时,即可以判断该id最早的操作请求是否超时,因而,本超时检测电路能够以相对简单的电路实现对复杂目标总线的超时检测,尤其适合于高速的目标总线,以及对总线数据丢失及其看重的处理芯片,例如车载soc。

20、本发明的其他有益效果,将在具体实施方式中通过具体技术特征和技术方案的介绍来阐述,本领域技术人员通过这些技术特征和技术方案的介绍,应能理解所述技术特征和技术方案带来的有益技术效果。

- 还没有人留言评论。精彩留言会获得点赞!