PCIe交换机芯片硅前仿真系统的制作方法

本发明涉及pcie交换机芯片硅前仿真系统,属于仿真。

背景技术:

1、pcie是一种高速串行计算机扩展总线标准,使用基于点对点拓扑的高速串行互连,拓扑由端点之间的几个串行链路(或通道)组成。pcie总线的各个层次由芯片硬件逻辑实现,协议共分为4层:物理层、数据链路层、事务层和应用层,其中,物理层实现高速串行链路的收/发和编/解码,数据链路层实现纠错、流控制和确认,事务层使用事务层数据包(tlp)将用户应用程序数据或完成数据转换为pcie事务,应用层则由用户根据应用场景和需求定制和设计,tlp载荷中承载应用层的存储/网络/计算等上层应用相关的协议内容,目前大部分的存储/网络/计算类的设备也均采用标准pcie接口,例如存储类的nvme固态硬盘和hba存储卡,网络类的以太网卡,计算类的gpu卡和加速卡等。

2、pcie交换机芯片是一种集成电路芯片,用于构建基于pcie总线的多个设备的互连拓扑,它实现了tlp的高速转发和路由,提供了pcie端口的扩展和汇聚能力。基于pcie交换机芯片可将多个pcie设备连接到一个根端口上。pcie交换机芯片的主要功能包括tlp报文的接收和发送,数据包的分片和重组,多端口的调度和仲裁,各类应用的流量控制和服务质量保证等,在多个输入端口和多个输出端口之间进行tlp的路由和转发,在pcie互连拓扑中实现不同设备之间的数据交换,具有高带宽、低延迟和可靠性高的特点。如下图所示,pcie交换机芯片通常包含一个上行端口(usp:upstream port)和多个下行端口(downstreamport),其中上行端口负责与上游的根联合体(rc,root complex)连接,下行端口负责与下游的各种存储/网络/计算类pcie终端设备(ep,endpoint)连接。每个端口都可以与一个设备相连,端口之间通过一条或多条高速数据通道进行通信,其中每个端口都有独立的通道带宽,实现多端口间的高性能并行数据传输。

3、pcie交换机芯片系统互连拓扑见图1。

4、在pcie总线的tlp载荷中,承载应用层的存储/网络/计算等上层应用协议相关内容,比较典型的如存储类的nvme协议。基于pcie的nvme协议是一种基于非易失性存储器的读写命令和数据的规范,它定义了宿主(host)与非易失性存储器的通信方式,双方通过队列对进行交互,队列对包括两个队列,分别是提交队列(sq,submission queue)和完成队列(cq,completion queue),其中提交队列用于宿主向nvme设备发送nvme命令,而完成队列则用于nvme设备向宿主反馈命令执行情况。提交队列和完成队列的实体是宿主内存的一个区域,在数据结构上体现为一个环形缓冲区,通过头指针和尾指针分别指示该环形缓冲区的首/尾元素。nvme协议通过门铃机制来告知存储设备提交队列是否有新的命令,在设备侧每个队列都有一个门铃寄存器,对于提交队列而言,这个门铃寄存器表示的是尾指针。宿主将nvme命令写入到提交队列后,更新映射到位于设备寄存器空间中的尾指针门铃寄存器,此时存储设备端知晓有新的命令到来,对其进行处理并进行相应的nvme操作;对于完成队列而言,这个门铃寄存器表示的是头指针,当存储设备完成一个nvme命令时,通过完成队列来把完成的结果告知宿主端,宿主端对其处理后更新映射到位于设备寄存器空间中的头指针门铃寄存器。

5、nvme协议充分利用pcie总线的低延时以及并行性,还有处理器、平台与应用的并行性,在可控制的存储成本下,极大的提升固态硬盘的读写性能,nvme存储设备目前在存储市场中已经被广泛采用,nvme是pcie交换机芯片的一个典型应用场景。硅前仿真作为保障pcie交换机芯片性能的重要手段,需要覆盖pcie交换机芯片连接nvme设备的测试场景,但nvme协议本身较为复杂,涉及到诸多非易失存储介质的命令和操作流程,存在建模难度大且模型复杂度太高影响仿真效率的问题。而网络设备和计算设备协议在pcie侧同样采用了类似nvme的环形队列的宿主-设备交互方式,但在数据结构和流程上与nvme协议存在差别,各家厂商的网卡设备和gpu卡/加速卡设备的pcie总线行为也有所不同,pcie交换机芯片的硅前性能仿真同样需要上述网络类和计算类的设备应用场景。

6、当前现有的技术方案中,如中国专利公开号cn114880977a:软硬件联合仿真系统、方法、装置、设备和存储介质,通过软件仿真器模拟真实软件的运行平台,生成虚拟运行平台以及在所述虚拟运行平台上运行所述真实软件,通过硬件仿真器模拟真实pcie设备的硬件(芯片),通过虚拟连接器仿真所述真实运行平台和真实硬件之间的连接设备,基于上述软件仿真器和硬件仿真器产生读取请求模拟pcie总线上的读写操作。

7、现有的技术方案中,依靠软件仿真器运行真实软件,以此模拟宿主在pcie根联合体的总线行为,虽然能够产生准确的产生各类pcie总线事务,但是受限于软件仿真器的性能以及虚拟连接器的效率,通常性能较低,只能够用于软件和芯片适配和交互流程的仿真验证,不适用于pcie交换机芯片的性能仿真验证,且现有技术缺乏对各类存储设备、网络设备、计算类设备的pcie总线行为的准确描述和建模,无法覆盖包含上述各类设备互连系统中pcie交换机芯片的性能验证场景。

8、基于此,提出本发明。

技术实现思路

1、本发明针对现有技术存在的不足,提供了pcie交换机芯片硅前仿真系统,具体技术方案如下:

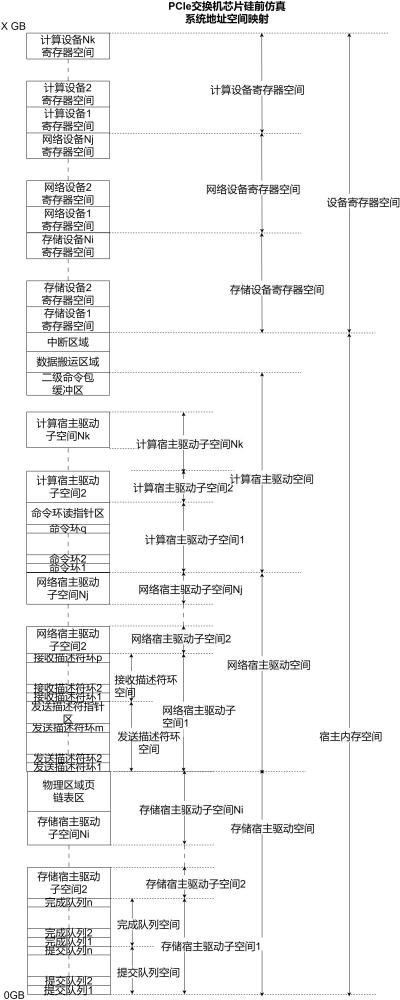

2、pcie交换机芯片硅前仿真系统,包括仿真系统地址空间映射和pcie总线模型;

3、所述仿真系统地址空间映射包括:

4、位于根联合体侧的宿主内存空间、位于终端侧的设备寄存器空间;

5、所述pcie总线模型包括根联合体总线模型、pcie交换机芯片硅前模型、存储设备总线模型、网络设备总线模型、计算设备总线模型、后端延时发生器、总线性能监控器。

6、更进一步的改进,所述宿主内存空间包括存储宿主驱动空间、网络宿主驱动空间、计算宿主驱动空间、数据搬运区域、中断区域;

7、所述存储宿主驱动空间包含ni个存储宿主驱动子空间和一个物理区域页链表区,每个存储宿主驱动子空间用于保存对应存储设备的提交队列和完成队列;

8、所述物理区域页链表区,用于保存存储命令的内存物理地址链表,当且仅当存储命令操作涉及的数据块超过2个物理页内存的大小时,存储设备总线模型收到提交队列条目后需要向存储宿主驱动子空间的物理区域页链表区发起地址和长度固定的读操作;

9、所述网络宿主驱动空间包含nj个网络宿主驱动子空间,每个网络宿主驱动子空间用于保存网络发送描述符环、发送描述符环头指针区和接收描述符环;

10、所述计算宿主驱动空间包含nk个计算宿主驱动子空间和1个二级命令缓冲区,每个计算宿主驱动子空间用于保存命令环和命令环读指针区;

11、所述二级命令缓冲区,用于保存非直接的二级计算命令,计算设备总线模型收到命令环中的一级计算命令后需要向计算宿主驱动子空间的二级命令缓冲区发起地址和长度固定的读操作;

12、所述数据搬运区域,用于存储设备、网络设备或计算设备发起直接内存访问时数据的写入和读出;

13、所述中断区域,用于存储设备、网络设备或计算设备发起中断信号消息报文所指向的地址空间;

14、所述设备寄存器空间包括存储设备寄存器空间、网络设备寄存器空间、计算设备寄存器空间;

15、所述存储设备寄存器空间,用于保存提交队列尾指针门铃寄存器和完成队列头指针门铃寄存器;

16、所述网络设备寄存器空间,用于保存发送描述符环尾指针寄存器和接收描述符环尾指针寄存器;

17、所述计算设备寄存器空间,用于保存命令环的写指针寄存器;

18、所述根联合体总线模型负责模拟宿主侧的存储驱动、网络驱动和计算驱动在pcie总线上的行为,包括:ni个存储宿主驱动子模型、nj个网络宿主驱动子模型、nk个计算宿主驱动子模型、报文多路复用器和报文解复用器,ni与存储设备总线模型的数量保持一致,nj与网络设备总线模型的数量保持一致,nk与计算设备总线模型的数量保持一致;根联合体总线模型还负责接收和处理针对宿主内存空间数据搬运区域和中断区域的pcie读、写事务;

19、所述存储宿主驱动子模型,依据存储设备协议以及存储命令输入或输出操作的pcie事务流程,构建和发送针对存储设备寄存器空间的pcie读或写事务,接收和处理针对存储宿主驱动空间的pcie读或写事务;

20、所述网络宿主驱动子模型,依据网络设备协议以及网络收或发包输入或输出操作的pcie事务流程,构建和发送针对网络设备寄存器空间的pcie读或写事务,接收和处理针对网络宿主驱动空间的pcie读或写事务;

21、所述计算宿主驱动子模型,依据计算设备协议以及计算命令输入或输出操作的pcie事务流程,构建和发送针对计算设备寄存器空间的pcie读或写事务,接收和处理针对计算宿主驱动空间的pcie读或写事务;

22、所述报文多路复用器,负责将多个存储宿主驱动子模型、网络宿主驱动子模型或计算宿主驱动子模型发出的tlp报文进行多路仲裁和选通,按照公平仲裁原则选通其中一路后将对应的tlp报文由根联合体总线模型发往pcie交换机芯片硅前模型;

23、所述报文解复用器,负责将pcie交换机芯片硅前模型发送到根联合体总线模型的tlp报文进行解析,依据报文中地址和请求者或完成者标识确定报文目的地,并将其分发到对应的存储宿主驱动子模型、网络宿主驱动子模型或计算宿主驱动子模型;

24、所述pcie交换机芯片硅前模型,即待验证的pcie交换机芯片的真实设计,在芯片设计流程的不同阶段表现为不同抽象层次的设计模型:

25、在架构设计阶段为芯片的行为级模型,在逻辑设计阶段为rtl模型,上述模型行为均要求时钟精确;

26、所述存储设备总线模型,其总数为ni,与所述存储宿主驱动子空间个数、存储宿主驱动子模型个数保持一致;所述存储设备总线模型负责模拟存储设备在pcie总线上的行为,依据存储设备协议以及存储命令输入或输出操作的pcie事务流程,构建和发送针对宿主内存空间中的存储宿主驱动子空间、物理区域页链表区、数据搬运区域、中断区域的pcie读或写事务,接收和处理针对该存储设备寄存器空间的pcie读或写事务;

27、所述网络设备总线模型,其总数为nj,与所述网络宿主驱动子空间个数、网络宿主驱动子模型个数保持一致;所述网络设备总线模型负责模拟网络设备在pcie总线上的行为,依据网络设备协议以及网络收或发包输入或输出操作的pcie事务流程,构建和发送针对宿主内存空间中的网络宿主驱动子空间、数据搬运区域、中断区域的pcie读或写事务,接收和处理针对该网络设备寄存器空间的pcie读或写事务;

28、所述计算设备总线模型,其总数nk,与所述计算宿主驱动子空间个数、计算宿主驱动子模型个数保持一致;所述计算设备总线模型负责模拟计算设备在pcie总线上的行为,依据计算设备协议以及计算命令输入或输出操作的pcie事务流程,构建和发送针对宿主内存空间中的计算宿主驱动子空间、数据搬运区域、中断区域的pcie读或写事务,接收和处理针对该计算设备寄存器空间的pcie读或写事务;

29、所述后端延时发生器,负责在根联合体总线模型和设备模型的接收或处理pcie报文过程中,按照pcie交换机芯片硅前仿真系统的输入参数,注入等量的pcie报文传输延时,以模拟和逼近真实宿主驱动和存储设备、网络设备、计算设备在带宽、时延以及每秒输入或输出操作次数性能指标;设备模型是存储设备总线模型、网络设备总线模型或计算设备总线模型;

30、所述总线性能监控器,负责在根联合体总线模型侧监控各个设备在pcie总线上的性能,实时打印各个设备的带宽、时延和每秒输入或输出操作次数性能仿真结果数据。

31、更进一步的改进,所述存储命令输入或输出操作的pcie事务流程步骤包括:

32、根联合体侧,生产提交队列条目;

33、根联合体侧,写提交队列尾指针门铃寄存器;

34、存储设备侧,读取提交队列条目;

35、根联合体侧,返回发送命令队列条目;

36、存储设备侧,读取物理区域页链表区;

37、根联合体侧,返回物理区域页链表区;

38、存储设备侧,直接内存写访问;

39、存储设备侧,直接内存读访问;

40、根联合体侧,返回直接内存读响应;

41、存储设备侧,写完成队列条目;

42、存储设备侧,发中断信号消息;

43、根联合体侧,写完成队列头指针门铃寄存器。

44、更进一步的改进,所述网络收包输入或输出操作的pcie事务流程步骤包括:

45、根联合体侧,生产接收描述符;

46、根联合体侧,写接收描述符环尾指针寄存器;

47、网络设备侧,读取接收描述符;

48、根联合体侧,返回接收描述符;

49、网络设备侧,直接内存写访问;

50、网络设备侧,回写接收描述符;

51、网络设备侧,发中断信号消息。

52、更进一步的改进,所述网络发包输入或输出操作的pcie事务流程步骤包括:

53、根联合体侧,生产发送描述符;

54、根联合体侧,写发送描述符环尾指针寄存器;

55、网络设备侧,读取发送描述符;

56、根联合体侧,返回发送描述符;

57、网络设备侧,直接内存读访问;

58、根联合体侧,返回直接内存读响应;

59、网络设备侧,回写发送描述符环头指针;

60、网络设备侧,发中断信号消息。

61、更进一步的改进,所述计算命令输入或输出操作的pcie事务流程步骤如下:

62、根联合体侧,生产计算命令包;

63、根联合体侧,写命令环写指针寄存器;

64、计算设备侧,读取计算命令包;

65、根联合体侧,返回计算命令包;

66、计算设备侧,读二级命令包;

67、根联合体侧,返回二级命令包;

68、计算设备侧,直接内存读访问;

69、根联合体侧,返回直接内存读响应;

70、计算设备侧,直接内存写访问;

71、计算设备侧,回写命令环读指针;

72、计算设备侧,发中断信号消息。

73、更进一步的改进,所述存储宿主驱动子空间=队列个数×队列深度×(提交队列条目宽度+完成队列条目宽度);

74、队列个数、队列深度均由所述pcie交换机芯片硅前仿真系统的输入参数定义;

75、完成队列与提交队列为一一对应关系;

76、提交队列条目宽度、完成队列条目宽度均由存储设备标准协议定义;

77、存储宿主驱动子空间的数量ni与存储设备总线模型个数保持一致;

78、所述网络宿主驱动子空间大小=发送描述符环个数×发送描述符环深度×发送描述符宽度+发送描述符环个数×发送描述符环头指针宽度+接收描述符环个数×接收描述符环深度×接收描述符宽度;

79、发送描述符环个数、发送描述符环深度、接收描述符环个数、接收描述符环深度均由pcie交换机芯片硅前仿真系统的输入参数定义;

80、发送描述符宽度、发送描述符头指针宽度、接收描述符宽度均由网络设备协议定义;

81、网络宿主驱动子空间的数量nj与网络设备总线模型个数保持一致;

82、所述计算宿主驱动子空间大小=命令环个数×(命令环深度×计算命令宽度+命令环读指针宽度);

83、命令环个数、命令环深度均由pcie交换机芯片硅前仿真系统的输入参数定义;

84、计算命令宽度、命令环读指针宽度均由计算设备协议定义;

85、计算宿主驱动子空间的数量nk与计算设备总线模型个数保持一致;

86、所述存储设备寄存器空间大小=存储设备个数×队列个数×(提交队列尾指针门铃寄存器宽度+完成队列头指针门铃寄存器宽度);

87、提交队列尾指针门铃寄存器宽度固定为4个字节,完成队列头指针门铃寄存器宽度固定为4个字节;

88、所述网络设备寄存器空间大小=网络设备个数×(发送描述符环个数×发送描述符环尾指针寄存器宽度+接收描述符环个数×接收描述符环尾指针寄存器宽度);

89、发送描述符环尾指针寄存器宽度固定为4个字节,接收描述符环尾指针寄存器宽度固定为4个字节;

90、所述计算设备寄存器空间大小=计算设备个数×命令环个数×命令环写指针寄存器宽度;

91、命令环写指针寄存器宽度固定为4个字节。

92、更进一步的改进,所述存储宿主驱动子空间的物理区域页链表区的大小固定为4096个字节;

93、计算宿主驱动子空间的二级命令缓冲区大小固定为64个字节;

94、所述数据搬运区域的空间大小固定为4096个字节;

95、所述中断区域的空间大小固定为4个字节。

96、本发明提供了pcie交换机芯片硅前仿真系统,以pcie交换机芯片为中心,在其外围模拟各种pcie标准接口的计算设备、存储设备、网络设备以及根联合体侧宿主驱动的pcie总线行为,以各类设备的标称性能指标作为基准,建立pcie交换机芯片互连系统的仿真测试能力和性能评估能力。在芯片流片前获得pcie交换机芯片的关键技术性能指标结果,覆盖主流pcie设备应用和性能测试场景,提高芯片硅前性能仿真的准确度和效率,提升流片信心。

97、在芯片流片前覆盖主流的存储设备、网络设备、计算设备的性能测试场景,解决pcie交换机芯片硅前性能评估难度大的问题,提升芯片验证效率,减少流片风险。

98、本发明的有益效果:

99、1、本发明通过构建性能仿真系统地址空间映射以及对pcie根联合体和存储设备、网络设备、计算设备的总线行为建模,精确模拟上述各类设备以及宿主驱动在pcie接口上的输入、输出执行流程和与之相关的总线事务行为,相对于传统方案,能够更准确和有效的覆盖主流pcie应用相关的性能测试场景,在芯片流片前快速获得主流应用场景的性能指标结果,有效提升pcie交换机芯片硅前性能仿真结果的准确性和覆盖率,降低芯片性能在硅前验证不充分的风险。

100、2、相对于传统方案,宿主和设备只仿真模拟其在pcie总线上的事务和行为,而不需要运行真实的软件,因而不受软件仿真器和虚拟连接器的性能限制,同时也降低了仿真平台的复杂度,仿真性能和效率得到提高。

- 还没有人留言评论。精彩留言会获得点赞!