芯片测试机时钟同步方法、装置、电子设备和存储介质与流程

本技术涉及芯片测试,特别是涉及一种芯片测试机时钟同步方法、装置、电子设备和存储介质。

背景技术:

1、数字芯片测试机是一种用于测试和验证数字芯片(如集成电路、处理器、fpga等)性能和功能的专用设备。它通常由硬件和软件组成,可以对芯片进行各种测试和测量,以确保其在设计规格和预期性能范围内正常工作。数字芯片测试机可以执行电气测试、时序测试、逻辑功能测试、性能测试、可靠性测试等功能。数字芯片测试机在芯片设计和生产过程中起着重要的作用,可以帮助开发人员和制造商确保芯片的质量和性能,并发现和解决潜在的问题和缺陷。

2、为了保证芯片的可靠性,数字芯片测试机通常利用pattern(时序芯片)测试来判断芯片功能是否正常,从而实现数字芯片大规模量产时的快速测试。数字芯片测试机一般支持几百个pattern测试通道,例如512、768、1024通道等,每个通道输出的pattern数字波形都需要同时输出到待测数字芯片的引脚处,即pattern数字芯片需要边沿对齐,以保证输出到待测数字芯片引脚处的信号间时序是正确的。以此为目的,要保证所有数字芯片测试机所有pattern通道输出的数字波形边沿对齐,需要每个数字测量办卡的时钟是同步的。

3、相关技术中,为了实现多个数字芯片测试机的时钟信号同步,通常需要将多块测试背板根据彼此之间的主从模式连接,并使得pattern模块利用输入时钟的第一个边沿触发来检测时钟的开始,即需要保证进入pattern模块用于控制同步的时钟的第一个边沿必须保证完全同步。

4、然而,目前的数字芯片测试机的时钟同步方法,存在如下的技术问题:

5、不同的芯片测试机可能存在不同的专有时钟芯片,导致在时钟切换的过程中,pattern模块难以根据统一的标准检测到最新时钟的第一个边沿,导致时钟同步处理困难。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种能够提高多芯片测试机系统内多个芯片测试机的时钟同步处理的精度和稳定性的一种芯片测试机时钟同步方法、装置、电子设备和计算机可读存储介质。

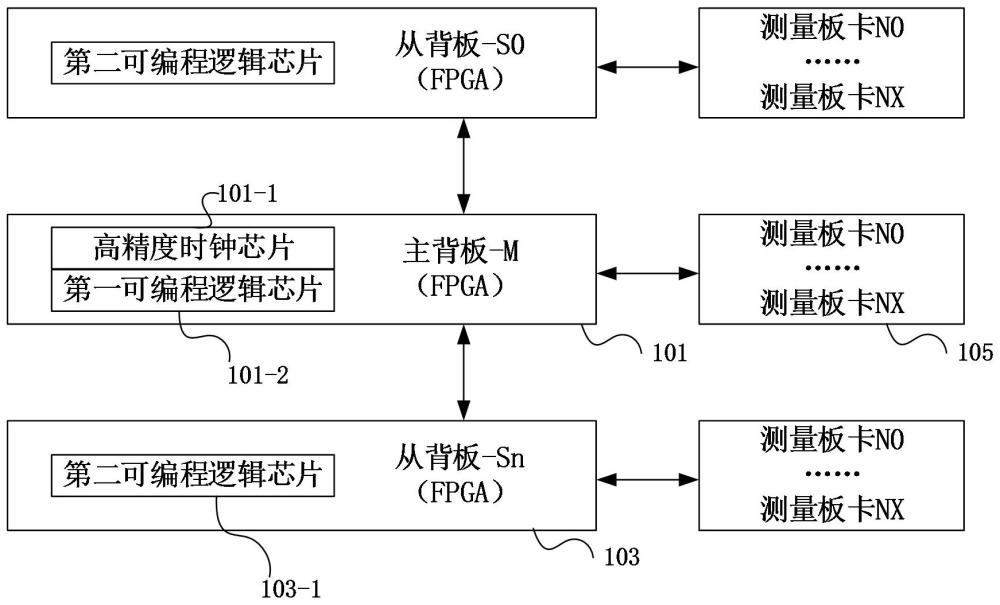

2、第一方面,本技术提供了一种芯片测试机时钟同步方法。所述芯片测试机包括主背板以及若干个从背板,所述主背板以及所述从背板均通讯连接有多个测试板卡,所述主背板包括高精度时钟芯片以及第一可编程逻辑芯片,所述从背板包括第二可编程逻辑芯片,所述方法包括:

3、响应于对多个所述测试板卡进行时钟同步处理的指令,基于所述高精度时钟芯片配置并发送预设频率的低频检测时钟信号至所述第一可编程逻辑芯片和所述第二可编程逻辑芯片;

4、当所述第一可编程逻辑芯片检测到所述低频检测时钟信号时,基于所述高精度时钟芯片配置目标频率的高精度时钟信号,所述目标频率高于所述预设频率;

5、当验证所述第一可编程逻辑芯片和所述第二可编程逻辑芯片当前获取的时钟信号满足预设的状态约束条件时,基于所述高精度时钟芯片发送所述高精度时钟信号至所述第一可编程逻辑芯片和所述第二可编程逻辑芯片,以完成所有所述测试板卡的时钟同步。

6、在其中一个实施例中,所述当所述第一可编程逻辑芯片检测到所述低频检测时钟信号时,还包括:

7、基于所述第一可编程逻辑芯片发送触发信号至所述第二可编程逻辑芯片;

8、基于所述触发信号指示所述第一可编程逻辑芯片以及所述第二可编程逻辑芯片进行同步计时。

9、在其中一个实施例中,所述基于所述触发信号指示所述第一可编程逻辑芯片以及所述第二可编程逻辑芯片进行同步计时包括:

10、当所述第一可编程逻辑芯片计时达到第一预设时长且所述第二可编程逻辑芯片计时达到第二预设时长时,判定所述第一可编程逻辑芯片与所述第二可编程逻辑芯片当前获取的所述时钟信号的开始标志位一致,所述第一预设时长为所述第二预设时长与所述低频检测时钟信号的周期之和。

11、在其中一个实施例中,所述基于所述触发信号指示所述第一可编程逻辑芯片以及所述第二可编程逻辑芯片进行同步计时之前,还包括:

12、关闭所述测试板卡以及与所述测试板卡相关联的所述主背板和所述从背板之间的使能通道。

13、在其中一个实施例中,所述基于所述高精度时钟芯片配置并发送预设频率的低频检测时钟信号至所述第一可编程逻辑芯片和所述第二可编程逻辑芯片之后,还包括:

14、响应于检测到的所述主背板以及所述从背板,设置所述开始标志位并启动计时;

15、当所述第二可编程逻辑芯片达到所述第二预设时长时,判定所述第一可编程逻辑芯片和所述第二可编程逻辑芯片获取的所述高精度时钟信号同步完成;

16、开放所述使能通道,以基于目标背板向相对于的目标测试板卡发送所述高精度时钟信号。

17、在其中一个实施例中,所述主背板包括第一系统时钟芯片,所述从背板包括第二系统时钟芯片,所述响应于对多个所述测试板卡进行时钟同步处理的指令之前,还包括:

18、基于所述第一系统时钟芯片和所述第二系统时钟芯片配置相应背板的初始时钟,以使所述主背板和所述从背板的完成系统时钟配置。

19、在其中一个实施例中,所述触发信号为所述第一可编辑逻辑芯片以所述系统时钟作为参考时钟在所述低频检测时钟信号的上升沿生成的同步起始脉冲信号。

20、第二方面,本技术还提供了一种芯片测试机时钟同步装置,所述芯片测试机包括主背板以及若干个从背板,所述主背板以及所述从背板均通讯连接有多个测试板卡,所述主背板包括高精度时钟芯片以及第一可编程逻辑芯片,所述从背板包括第二可编程逻辑芯片,所述方法包括:

21、低频检测时钟模块,用于响应于对多个所述测试板卡进行时钟同步处理的指令,基于所述高精度时钟芯片配置并发送预设频率的低频检测时钟信号至所述第一可编程逻辑芯片和所述第二可编程逻辑芯片;

22、高精度时钟配置模块,用于当所述第一可编程逻辑芯片检测到所述低频检测时钟信号时,基于所述高精度时钟芯片配置目标频率的高精度时钟信号,所述目标频率高于所述预设频率;

23、时钟同步模块,用于当验证所述第一可编程逻辑芯片和所述第二可编程逻辑芯片当前获取的时钟信号满足预设的状态约束条件时,基于所述高精度时钟芯片发送所述高精度时钟信号至所述第一可编程逻辑芯片和所述第二可编程逻辑芯片,以完成所有所述测试板卡的时钟同步。

24、在其中一个实施例中,所述高精度时钟配置模块,还包括:

25、触发信号生成模块,用于基于所述第一可编程逻辑芯片发送触发信号至所述第二可编程逻辑芯片;

26、同步计时模块,用于基于所述触发信号指示所述第一可编程逻辑芯片以及所述第二可编程逻辑芯片进行同步计时。

27、在其中一个实施例中,所述同步计时模块包括:

28、同步校验模块,用于当所述第一可编程逻辑芯片计时达到第一预设时长且所述第二可编程逻辑芯片计时达到第二预设时长时,判定所述第一可编程逻辑芯片与所述第二可编程逻辑芯片当前获取的所述时钟信号的开始标志位一致,所述第一预设时长为所述第二预设时长与所述低频检测时钟信号的周期之和。

29、在其中一个实施例中,所述同步计时模块之前,还包括:

30、使能通道限制模块,用于关闭所述测试板卡以及与所述测试板卡相关联的所述主背板和所述从背板之间的使能通道。

31、在其中一个实施例中,所述低频检测时钟模块之后,还包括:

32、计时启动模块,用于响应于检测到的所述主背板以及所述从背板,设置所述开始标志位并启动计时;

33、同步完成模块,用于当所述第二可编程逻辑芯片达到所述第二预设时长时,判定所述第一可编程逻辑芯片和所述第二可编程逻辑芯片获取的所述高精度时钟信号同步完成;

34、使能通道开放模块,用于开放所述使能通道,以基于目标背板向相对于的目标测试板卡发送所述高精度时钟信号。

35、在其中一个实施例中,所述主背板包括第一系统时钟芯片,所述从背板包括第二系统时钟芯片,所述低频检测时钟模块之前,还包括:

36、系统时钟配置模块,用于基于所述第一系统时钟芯片和所述第二系统时钟芯片配置相应背板的初始时钟,以使所述主背板和所述从背板的完成系统时钟配置。

37、在其中一个实施例中,所述触发信号为所述第一可编辑逻辑芯片以所述系统时钟作为参考时钟在所述低频检测时钟信号的上升沿生成的同步起始脉冲信号。

38、第三方面,本技术还提供了一种计算机可读存储介质。所述计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现如第一方面中任意一项实施例所述的一种芯片测试机时钟同步方法中的步骤。

39、第四方面,本技术还提供了一种电子设备。包括至少一个处理器,以及与所述至少一个处理器通信连接的存储器;其中,所述存储器存储有可被所述至少一个处理器执行的指令,所述至少一个处理器通过执行所述存储器存储的指令实现如第一方面中任意一项所述的一种芯片测试机时钟同步方法。

40、上述一种芯片测试机时钟同步方法、装置、计算机设备、存储介质和计算机程序产品,通过独权中的技术特征进行推导,能够达到对应背景技术中的技术问题的如下有益效果:

41、在芯片测试机的时钟同步处理中,在接收到对多个测试板卡进行时钟同步处理的指令后,首先根据高精度时钟芯片配置预设频率的低频检测时钟信号,并发送至第一可编程逻辑芯片以及第二可编程逻辑芯片中。随后,当第一可编程逻辑芯片检测到低频检测时钟信号后,可以基于高精度时钟芯片配置得到目标频率的高精度时钟信号,此时的高精度时钟信号的目标频率高于预设频率。当验证得到第一可编程逻辑芯片以及第二可编程逻辑芯片当前获取的时钟信号满足预设的状态约束条件时,可以判定此时的主背板以及从背板之间的通讯时钟状态的稳定性已经能够满足时钟同步的需求,此时可以将生成的高精度时钟信号发送至第一可编程逻辑芯片以及第二可编程逻辑芯片中,从而使得主背板以及从背板能够同步接收到信号频率精确且状态状态稳定的高精度时钟信号,最终实现了测试板卡之间的时钟同步处理。在实施中,能够通过较易生成的低频检测信号判断信号的稳定性以及精确度等状态,在确定信号状态后,生成所需要的高精度时钟信号,并进行配置分发,能够提高系统内芯片测试机的时钟同步的效率以及精确度。

- 还没有人留言评论。精彩留言会获得点赞!