芯片的三维建模方法、装置、电子设备及存储介质与流程

本技术属于半导体,尤其涉及一种芯片的三维建模方法、装置、电子设备及存储介质。

背景技术:

1、芯片设计与芯片制造通过gds格式的版图文件进行交互,版图文件通常为俯视平面图,由多层形状、颜色各异的图层堆叠在一起,每一图层对应于不同的工艺步骤,且图层有明场(clear tone)、暗场(dark tone)区分。

2、通常需要构建芯片的几何模型在对芯片进行器件仿真,分析芯片性能,但gds格式的版图文件不能直接作为器件仿真的文件,无法直观分析芯片各层结构特征,同时,芯片的版图文件版图中未绘制出芯片的轻掺杂漏(lightly doped drain,ldd)区域,ldd正是影响器件电学性能、可靠性的关键区域,对俯视平面的版图进行三维建模时,容易漏掉ldd区域,构建的几何模型无法降低器件漏端附近峰值电场,达到削弱热载流子注入效应的目的,影响芯片的性能分析。

3、目前,亟需一种芯片三维几何模型的构建手段,可以构建出芯片版图中未绘制的ldd区域的几何结构。

技术实现思路

1、本技术旨在至少解决现有技术中存在的技术问题之一。为此,本技术提出一种芯片的三维建模方法、装置、电子设备及存储介质,可以通过芯片的平面版图,构建包括ldd区域的三维模型,完整、准确地展示芯片的几何结构,提升芯片仿真精度。

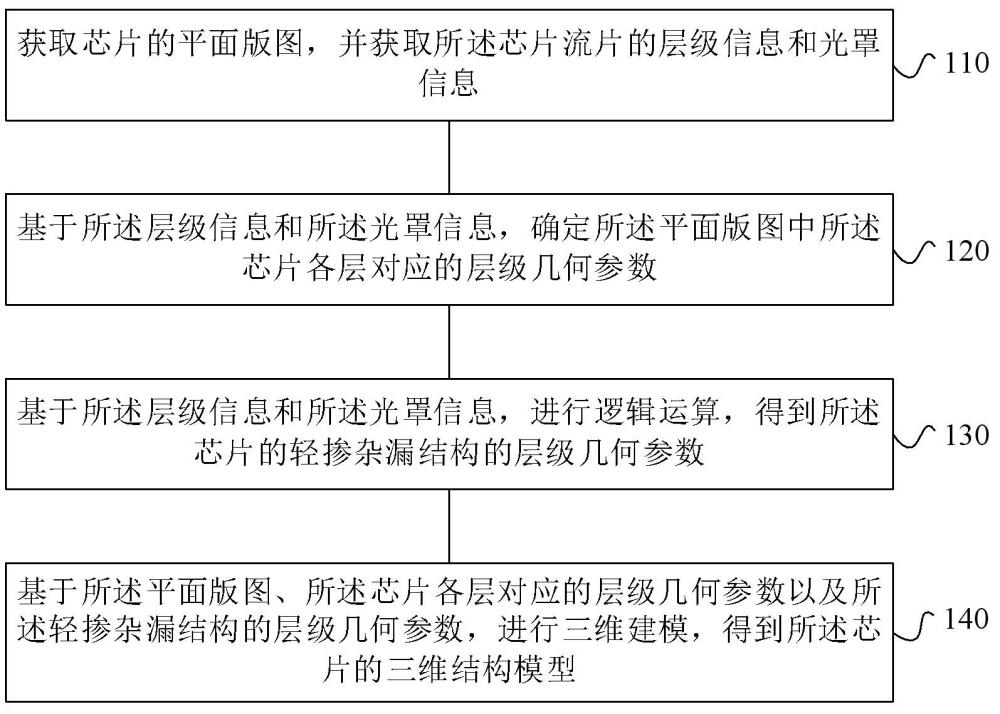

2、第一方面,本技术提供了一种芯片的三维建模方法,该方法包括:

3、获取芯片的平面版图,并获取所述芯片流片的层级信息和光罩信息;

4、基于所述层级信息和所述光罩信息,确定所述平面版图中所述芯片各层对应的层级几何参数;

5、基于所述层级信息和所述光罩信息,进行逻辑运算,得到所述芯片的轻掺杂漏结构的层级几何参数;

6、基于所述平面版图、所述芯片各层对应的层级几何参数以及所述轻掺杂漏结构的层级几何参数,进行三维建模,得到所述芯片的三维结构模型,所述三维结构模型包括所述轻掺杂漏结构对应的模块。

7、根据本技术的芯片的三维建模方法,通过芯片的层级信息和光罩信息进行逻辑运算,得到平面版图中未绘制的轻掺杂漏结构的层级几何参数,使用芯片的平面版图和流片的层级信息及光罩信息即可实现芯片的三维建模,构建出包括ldd区域的三维结构模型,完整、准确地展示芯片的几何结构,保证模型中器件电学性能及可靠性的准确性,有助于提升芯片仿真精度。

8、根据本技术的一个实施例,所述基于所述层级信息和所述光罩信息,进行逻辑运算,得到所述芯片的轻掺杂漏结构的层级几何参数,包括:

9、基于所述层级信息,确定所述轻掺杂漏结构所在的标识层;

10、基于所述光罩信息,对所述标识层进行逻辑运算,确定所述标识层的轻掺杂漏区;

11、基于所述轻掺杂漏区和所述轻掺杂漏结构的离子注入工艺信息,确定所述轻掺杂漏结构的层级几何参数。

12、根据本技术的一个实施例,所述基于所述光罩信息,对所述标识层进行逻辑运算,确定所述标识层的轻掺杂漏区,包括:

13、基于所述芯片的n型离子注入层和p型阱对应的所述光罩信息,对所述标识层进行逻辑运算,确定所述标识层中n型轻掺杂漏区;

14、基于所述芯片的p型离子注入层和n型阱对应的所述光罩信息,对所述标识层进行逻辑运算,确定所述标识层中p型轻掺杂漏区;

15、其中,所述轻掺杂漏区包括所述n型轻掺杂漏区和所述p型轻掺杂漏区。

16、根据本技术的一个实施例,所述基于所述芯片的n型离子注入层和p型阱对应的所述光罩信息,对所述标识层进行逻辑运算,确定所述标识层中n型轻掺杂漏区,包括:

17、求所述标识层和所述p型阱的交集,得到第一n型区域;

18、求所述第一n型区域和所述n型离子注入层的交集,得到所述n型轻掺杂漏区。

19、根据本技术的一个实施例,所述基于所述芯片的p型离子注入层和n型阱对应的所述光罩信息,对所述标识层进行逻辑运算,确定所述标识层中p型轻掺杂漏区,包括:

20、求所述标识层和所述n型阱的交集,得到第一p型区域;

21、求所述第一p型区域和所述p型离子注入层的交集,得到所述p型轻掺杂漏区。

22、根据本技术的一个实施例,所述基于所述轻掺杂漏区和所述轻掺杂漏结构的离子注入工艺信息,确定所述轻掺杂漏结构的层级几何参数,包括:

23、基于所述轻掺杂漏结构的离子注入工艺信息,确定所述轻掺杂漏结构的厚度;

24、基于所述离子注入工艺信息、所述轻掺杂漏结构的厚度和所述轻掺杂漏区,确定所述轻掺杂漏结构的边长。

25、根据本技术的一个实施例,所述基于所述离子注入工艺信息、所述轻掺杂漏结构的厚度和所述轻掺杂漏区,确定所述轻掺杂漏结构的边长,包括:

26、基于所述轻掺杂漏结构的厚度和离子入射角度,确定第一边长,所述第一边长为所述芯片的栅极侧墙下方的所述轻掺杂漏结构的长度;

27、将所述轻掺杂漏区和所述芯片的多晶硅层的长度作差,得到漏区边长;

28、基于所述第一边长和所述漏区边长,确定第二边长,所述第二边长为所述轻掺杂漏区的所述轻掺杂漏结构的长度,所述第一边长和所述第二边长为所述芯片同一方向上的长度。

29、根据本技术的一个实施例,所述基于所述层级信息和所述光罩信息,确定所述平面版图中所述芯片各层对应的层级几何参数,包括:

30、基于所述层级信息,确定所述芯片各层对应的物理版图标识;

31、基于所述物理版图标识,在所述芯片的工艺设计文件查找所述芯片各层对应的结构厚度;

32、基于所述芯片各层对应的结构厚度和所述光罩信息,确定所述芯片各层对应的层级几何参数。

33、第二方面,本技术提供了一种芯片的三维建模装置,该装置包括:

34、获取模块,用于获取芯片的平面版图,并获取所述芯片流片的层级信息和光罩信息;

35、第一处理模块,用于基于所述层级信息和所述光罩信息,确定所述平面版图中所述芯片各层对应的层级几何参数;

36、第二处理模块,用于基于所述层级信息和所述光罩信息,进行逻辑运算,得到所述芯片的轻掺杂漏结构的层级几何参数;

37、第三处理模块,用于基于所述平面版图、所述芯片各层对应的层级几何参数以及所述轻掺杂漏结构的层级几何参数,进行三维建模,得到所述芯片的三维结构模型,所述三维结构模型包括所述轻掺杂漏结构对应的模块。

38、根据本技术的芯片的三维建模装置,通过芯片的层级信息和光罩信息进行逻辑运算,得到平面版图中未绘制的轻掺杂漏结构的层级几何参数,使用芯片的平面版图和流片的层级信息及光罩信息即可实现芯片的三维建模,构建出包括ldd区域的三维结构模型,完整、准确地展示芯片的几何结构,保证模型中器件电学性能及可靠性的准确性,有助于提升芯片仿真精度。

39、第三方面,本技术提供了一种电子设备,包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如上述第一方面所述的芯片的三维建模方法。

40、第四方面,本技术提供了一种非暂态计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现如上述第一方面所述的芯片的三维建模方法。

41、第五方面,本技术提供了一种计算机程序产品,包括计算机程序,所述计算机程序被处理器执行时实现如上述第一方面所述的芯片的三维建模方法。

42、本技术的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!