一种中央处理器CPU装置的制作方法

本申请涉及计算机,尤其涉及一种中央处理器cpu装置。

背景技术:

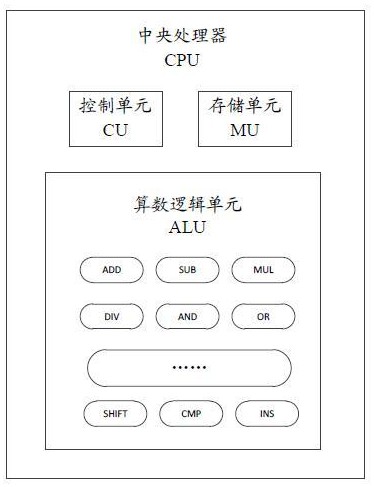

1、cpu内部的典型算力主要来源于alu,由alu提供加减乘除等运算,在cpu进行运算时,其实质就是调用alu中的某个运算指令。

2、现有技术中,若存在多个运算时,alu一次只能完成一个运算,将运算结果输出后,再进行下一次运算,这会导致cpu的计算效率很低;若使用其他运算单元,又会造成数据传输之间出现内存墙以及通信延迟的问题。

技术实现思路

1、本申请实施例提供一种中央处理器cpu装置,用于提升cpu的运算效率。

2、第一方面,本申请实施例提供一种中央处理器cpu的运算装置,包括:

3、控制单元cu、算术逻辑单元alu、存储单元mu;所述alu中包括多个算子模块;

4、所述cu用于确定待执行运算的算子调用顺序并将所述算子调用顺序和所述待执行运算中的操作数发送至所述alu;

5、所述alu用于依序调用所述算子调用顺序中的各算子模块进行对应操作数的运算,得到所述待执行运算的运算结果,并将所述运算结果存储至所述mu中。

6、本申请实施例中,通过控制单元cu确定待执行运算的算子调用顺序,使得算数逻辑单元alu在执行待执行运算时按照逻辑运算的顺序依次执行,保证运算结果的正确性;控制单元cu将待执行运算的算子调用顺序以及待执行运算所需的操作数发送至alu,在alu执行待执行运算时,不需频繁与存储单元交互,在alu内部可以一次完成待执行运算,在完成待执行运算后再将运算结果存储至mu中,避免了alu多次与存储单元交互而导致运算效率降低。

7、可选地,所述alu中还包括与各算子模块连通的交换模块、算子调用模块及子存储模块;

8、所述cu还用于将所述算子调用顺序发送至所述算子调用模块,并将所述待执行运算中的操作数发送至所述子存储模块;

9、所述算子调用模块用于依序调用所述算子调用顺序中的各算子模块进行对应操作数的运算;

10、所述交换模块用于依序将所述算子调用顺序指示的相邻的算子模块连通,将上一算子模块的子运算结果发送至下一算子模块。

11、本申请实施例中,通过交换模块使各个算子模块之间实现连通,可以在完成单一的算子运算后继续完成下一个算子运算,不需与alu外部的存储模块连通,在alu内部一次完成全部的算子运算,提升了cpu的运算效率;通过算子调用模块依序调用算子模块,使得待执行运算按照逻辑运算的顺序完成各算子的运算,保证了待执行运算的正确性;通过子存储模块,存储待执行运算中的操作数,避免了在待执行运算的执行过程中从外部设备中获取运算数据,同样提升了cpu的运算效率。

12、可选地,所述cu还用于向所述交换模块发送内部运算使能信号;

13、所述交换模块用于根据所述内部运算使能信号,按时钟信号依序将所述算子调用顺序指示的相邻的算子模块连通。

14、本申请实施例中,通过向交换模块发送内部运算使能信号,使得交换模块按照算子调用顺序将相邻算子连通,在未发送内部运算使能信号时,按照现有运算进行运算,使得本申请实施例可以通过控制信号控制实施,兼具了现有运算方式和本申请的运算方式。

15、可选地,所述cu具体用于通过第一配置信号将所述算子调用顺序发送至所述算子调用模块;通过第二配置信号将所述待执行运算中的操作数发送至所述子存储模块。

16、本申请实施例中,通过根据不同的配置信号完成不同的任务,避免了信号之间的冲突导致资源的冲突,进而影响cpu的运算效率。

17、可选地,所述cu具体用于在所述第一配置信号和所述第二配置信号之后,发送所述内部运算使能信号。

18、本申请实施例中,通过在第一配置信号和第二配置信号之后发送内部运算使能信号,避免了在内部运算使能信号发送后,alu还未完成内部配置而导致运算报错的问题。

19、可选地,所述alu还用于在未接收到所述内部运算使能信号时,在所述cu控制下依序执行所述待执行运算的各算子单元,并将单一算子模块的子运算结果存储至所述mu中。

20、本申请实施例中,通过在未接收到内部运算使能信号时,按照单一算子模块的运算方式执行待执行运算,避免了在不能使用alu内部运算时无法完成运算的情况;同时,保留原有的运算方式还可以在不需使用alu内部运算时完成运算。

21、第二方面,本申请实施例提供一种中央处理器cpu的运算方法,所述方法包括:

22、所述cpu中的控制单元cu确定待执行运算的算子调用顺序并将所述算子调用顺序和所述待执行运算中的操作数发送至所述cpu中的算术逻辑单元alu;

23、所述alu依序调用所述算子调用顺序中的各算子模块进行对应操作数的运算,得到所述待执行运算的运算结果,并将所述运算结果存储至所述cpu中的存储单元mu中。

24、可选地,将所述算子调用顺序和所述待执行运算中的操作数发送至所述cpu中的算术逻辑单元alu,包括:

25、所述cu将所述算子调用顺序发送至所述alu中的算子调用模块,并将所述待执行运算中的操作数发送至所述alu中的子存储模块;

26、所述alu依序调用所述算子调用顺序中的各算子模块进行对应操作数的运算,包括:

27、所述算子调用模块依序调用所述算子调用顺序中的各算子模块进行对应操作数的运算;

28、所述alu中的交换模块依序将所述算子调用顺序指示的相邻的算子模块连通,将上一算子模块的子运算结果发送至下一算子模块。

29、可选地,所述alu中的交换模块依序将所述算子调用顺序指示的相邻的算子模块连通之前,还包括:

30、所述cu向所述交换模块发送内部运算使能信号;所述内部运算使能信号用于触发所述交换模块处于工作模式。

31、可选地,所述cu向所述交换模块发送内部运算使能信号之前,还包括:

32、所述cu通过第一配置信号将所述算子调用顺序发送至所述算子调用模块;通过第二配置信号将所述待执行运算中的操作数发送至所述子存储模块。

33、本申请实施例中,通过控制单元cu确定待执行运算的算子调用顺序,使得算数逻辑单元alu在执行待执行运算时按照逻辑运算的顺序依次执行,保证运算结果的正确性;控制单元cu将待执行运算的算子调用顺序以及待执行运算所需的操作数发送至alu,在alu执行待执行运算时,不需频繁与存储单元交互,在alu内部可以一次完成待执行运算,在完成待执行运算后再将运算结果存储至mu中,避免了alu多次与存储单元交互而导致运算效率降低。

技术特征:

1.一种中央处理器cpu装置,其特征在于,包括:控制单元cu、算术逻辑单元alu、存储单元mu;所述alu中包括多个算子模块;

2.如权利要求1所述的装置,其特征在于,所述cu还用于向所述交换模块发送内部运算使能信号;

3.如权利要求2所述的装置,其特征在于,所述cu具体用于通过第一配置信号将所述算子调用顺序发送至所述算子调用模块;通过第二配置信号将所述待执行运算中的操作数发送至所述子存储模块。

4.如权利要求3所述的装置,其特征在于,所述cu具体用于在所述第一配置信号和所述第二配置信号之后,发送所述内部运算使能信号。

5.如权利要求2所述的装置,其特征在于,所述alu还用于在未接收到所述内部运算使能信号时,在所述cu控制下依序执行所述待执行运算的各算子单元,并将单一算子模块的子运算结果存储至所述mu中。

6.一种中央处理器cpu的运算方法,其特征在于,所述方法包括:

7.如权利要求6所述的方法,其特征在于,将所述算子调用顺序和所述待执行运算中的操作数发送至所述cpu中的算术逻辑单元alu,包括:

8.如权利要求7所述的方法,其特征在于,所述alu中的交换模块依序将所述算子调用顺序指示的相邻的算子模块连通之前,还包括:

9.如权利要求8所述的方法,其特征在于,所述cu向所述交换模块发送内部运算使能信号之前,还包括:

技术总结

本申请实施例提供了一种中央处理器CPU装置,涉及计算机技术领域,该装置包括:控制单元CU、算术逻辑单元ALU、存储单元MU;所述ALU中包括多个算子模块;所述CU用于确定待执行运算的算子调用顺序并将所述算子调用顺序和所述待执行运算中的操作数发送至所述ALU;所述ALU用于依序调用所述算子调用顺序中的各算子模块进行对应操作数的运算,得到所述待执行运算的运算结果,并将所述运算结果存储至所述MU中。通过控制单元CU将待执行运算的算子调用顺序以及待执行运算所需的操作数发送至ALU,在ALU执行待执行运算时,在ALU内部可以一次完成待执行运算,避免了ALU多次与存储单元交互而导致运算效率降低。

技术研发人员:刘瑞楷,葛蕾,葛云飞,马占刚

受保护的技术使用者:上海芯联芯智能科技有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!