一种验证方法、装置、电子设备及可读存储介质与流程

本发明涉及计算机,尤其涉及一种验证方法、装置、电子设备及可读存储介质。

背景技术:

1、一般来说,中央处理器(central processing unit,cpu)的随机验证是通过构建与模块功能相同的参考模型,通过向cpu和参考模型给予同样的激励,并采集输出结果比对来完成功能正确性的验证。对于内部路径复杂且数据计算与时序相关性强的待测设计(design under test,dut)来说,由于内部时序信号对数据运算具有较大影响,因此在参考模型(reference model,rm)的编写过程中,如果参考模型与待测设计的时序信号未对齐,会对参考模型的计算结果造成影响,例如高速缓存(cache)的错误替换、状态位的错误刷新等;并且,参考模型与待测设计的时序未对齐还会造成一些验证点无法覆盖,对验证完备性造成负面影响。

技术实现思路

1、本发明实施例提供一种验证方法、装置、电子设备及可读存储介质,可以实现待测设计与参考模型的时序对齐,避免参考模型与待测设计的时序未对齐对验证结果造成的负面影响。

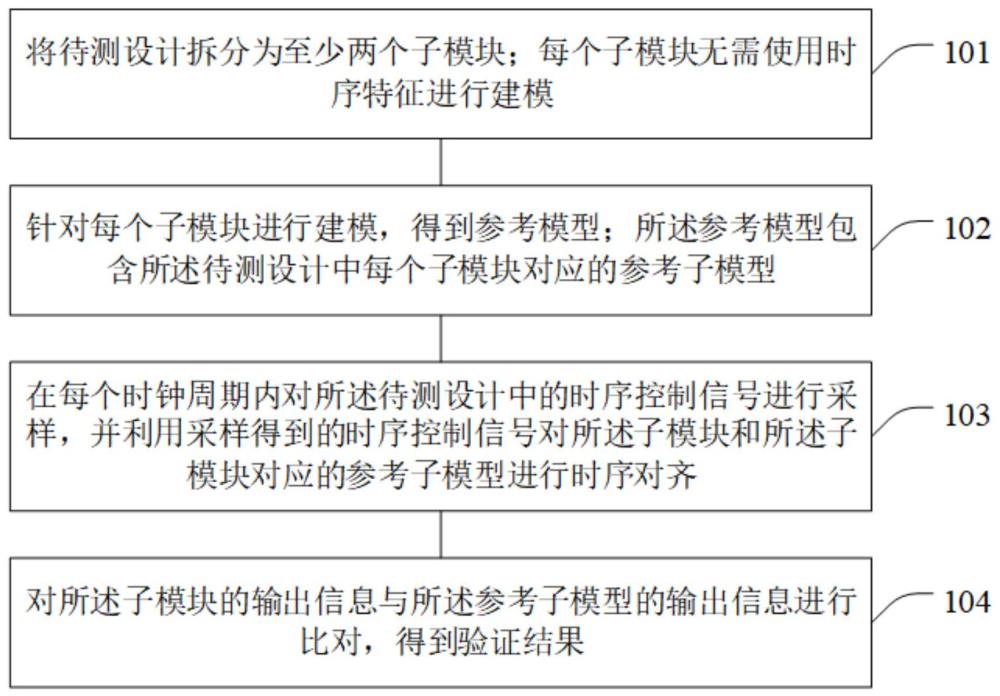

2、为了解决上述问题,本发明实施例公开了一种验证方法,所述方法包括:

3、将待测设计拆分为至少两个子模块;每个子模块无需使用时序特征进行建模;

4、针对每个子模块进行建模,得到参考模型;所述参考模型包含所述待测设计中每个子模块对应的参考子模型;

5、在每个时钟周期内对所述待测设计中的时序控制信号进行采样,并利用采样得到的时序控制信号对所述子模块和所述子模块对应的参考子模型进行时序对齐;

6、对所述子模块的输出信息与所述参考子模型的输出信息进行比对,得到验证结果。

7、可选地,所述在每个时钟周期内对所述待测设计中的时序控制信号进行采样,并利用采样得到的时序控制信号对所述子模块和所述子模块对应的参考子模型进行时序对齐,包括:

8、在每个时钟周期内对所述待测设计中的时序控制信号进行采样;

9、根据采样得到的时序控制信号确定第一参考子模型;所述第一参考子模型为所述待测设计中接收所述时序控制信号的第一子模块对应的参考子模型;

10、基于所述时序控制信号驱动所述第一参考子模型进行数据处理。

11、可选地,所述基于所述时序控制信号驱动所述第一参考子模型进行数据处理,包括:

12、根据所述时序控制信号在请求列表中查询第二参考子模型中当前处理的目标请求;所述请求列表用于记录各个参考子模型内部待处理的请求;所述第二参考子模型为所述待测设计中发送所述时序控制信号的第二子模块对应的参考子模型;

13、获取所述第二参考子模型对所述目标请求的处理结果,并基于所述处理结果更新所述目标请求的状态信息;

14、将所述目标请求发送至所述第一参考子模型,以使所述第一参考子模型处理所述目标请求。

15、可选地,所述根据采样得到的时序控制信号确定第一参考子模型,包括:

16、利用断言对采样得到的时序控制信号进行验证;

17、在所述时序控制信号通过断言验证的情况下,根据所述时序控制信号确定第一参考子模型。

18、可选地,所述参考模型中还包括请求控制模块,所述请求控制模块用于记录所述参考子模型的配置信息;所述方法还包括:

19、在所述配置信息指示第三参考子模型拒绝接收数据请求的情况下,若采集到发送至所述第三参考子模型对应的第三子模块的时序控制信号,则确定所述待测设计运行出错。

20、可选地,所述对所述子模块的输出信息与所述参考子模型的输出信息进行比对,得到验证结果,包括:

21、在所述待测设计运行过程中,采集各个子模块的第一输出信息和所述待测设计的第二输出信息;

22、将所述子模块的第一输出信息与所述子模块对应的参考子模型的第三输出信息进行比对,将所述待测设计的第二输出信息与所述参考模型的第四输出信息进行比对;

23、在各个所述子模块的第一输出信息与所述子模块对应的参考子模型的第三输出信息相匹配,且所述待测设计的第二输出信息与所述参考模型的第四输出信息相匹配的情况下,确定所述待测设计通过验证。

24、另一方面,本发明实施例公开了一种验证装置,所述装置包括:

25、拆分模块,用于将待测设计拆分为至少两个子模块;每个子模块无需使用时序特征进行建模;

26、构建模块,用于针对每个子模块进行建模,得到参考模型;所述参考模型包含所述待测设计中每个子模块对应的参考子模型;

27、时序对齐模块,用于在每个时钟周期内对所述待测设计中的时序控制信号进行采样,并利用采样得到的时序控制信号对所述子模块和所述子模块对应的参考子模型进行时序对齐;

28、验证模块,用于对所述子模块的输出信息与所述参考子模型的输出信息进行比对,得到验证结果。

29、可选地,所述时序对齐模块,包括:

30、采样子模块,用于在每个时钟周期内对所述待测设计中的时序控制信号进行采样;

31、确定子模块,用于根据采样得到的时序控制信号确定第一参考子模型;所述第一参考子模型为所述待测设计中接收所述时序控制信号的第一子模块对应的参考子模型;

32、驱动子模块,用于基于所述时序控制信号驱动所述第一参考子模型进行数据处理。

33、可选地,所述驱动子模块,包括:

34、查询单元,用于根据所述时序控制信号在请求列表中查询第二参考子模型中当前处理的目标请求;所述请求列表用于记录各个参考子模型内部待处理的请求;所述第二参考子模型为所述待测设计中发送所述时序控制信号的第二子模块对应的参考子模型;

35、获取单元,用于获取所述第二参考子模型对所述目标请求的处理结果,并基于所述处理结果更新所述目标请求的状态信息;

36、发送单元,用于将所述目标请求发送至所述第一参考子模型,以使所述第一参考子模型处理所述目标请求。

37、可选地,所述确定子模块,包括:

38、验证单元,用于利用断言对采样得到的时序控制信号进行验证;

39、确定单元,用于在所述时序控制信号通过断言验证的情况下,根据所述时序控制信号确定第一参考子模型。

40、可选地,所述参考模型中还包括请求控制模块,所述请求控制模块用于记录所述参考子模型的配置信息;所述装置还包括:

41、确定模块,用于在所述配置信息指示第三参考子模型拒绝接收数据请求的情况下,若采集到发送至所述第三参考子模型对应的第三子模块的时序控制信号,则确定所述待测设计运行出错。

42、可选地,所述验证模块,包括:

43、信息采集子模块,用于在所述待测设计运行过程中,采集各个子模块的第一输出信息和所述待测设计的第二输出信息;

44、信息比对子模块,用于将所述子模块的第一输出信息与所述子模块对应的参考子模型的第三输出信息进行比对,将所述待测设计的第二输出信息与所述参考模型的第四输出信息进行比对;

45、验证子模块,用于在各个所述子模块的第一输出信息与所述子模块对应的参考子模型的第三输出信息相匹配,且所述待测设计的第二输出信息与所述参考模型的第四输出信息相匹配的情况下,确定所述待测设计通过验证。

46、再一方面,本发明实施例还公开了一种电子设备,所述电子设备包括处理器、存储器、通信接口和通信总线,所述处理器、所述存储器和所述通信接口通过所述通信总线完成相互间的通信;所述存储器用于存放可执行指令,所述可执行指令使所述处理器执行前述的验证方法。

47、本发明实施例还公开了一种可读存储介质,当所述可读存储介质中的指令由电子设备的处理器执行时,使得电子设备能够执行前述的验证方法。

48、本发明实施例包括以下优点:

49、本发明实施例提供的验证方法,通过将待测设计拆分为至少两个子模块,针对每个子模块进行建模,并利用每个时钟周期内采集到的时序控制信号驱动子模块对应的参考子模型,就可以保证子模块与参考子模型的时序对齐,保证在各个参考子模型的运行顺序与待测设计中各个子模块之间的运行顺序相同,从而避免了未对齐的时序信号对计算结果的影响。并且,由于本发明实施例提供的验证方法对待测设计中的子模块与参考子模型进行了时序对齐,可以避免待测设计与参考模型的时序未对齐对验证完备性造成的负面影响。

- 还没有人留言评论。精彩留言会获得点赞!