芯片设计方法、芯片、主板及电子设备与流程

本发明涉及芯片封装,特别是涉及一种芯片设计方法、芯片、主板及电子设备。

背景技术:

1、随着大算力使用需求的出现,芯片产品也趋向朝着低电压大电流的方向发展,相应地,芯片的供电电源网络设计难度也随之增加。

2、为了保证高频的瞬态电流需求,在这种应用于大算力场景的芯片产品中,当采用bga(ball grid array,球状引脚栅格阵列)封装结构时,通常会在封装结构底层正对着裸芯处放置电容,从而使得裸芯正下方没有焊球,使得焊球在封装结构底层均围绕裸芯的四周分布,由于电流具备易于通过低电阻路径的特性,距离裸芯越近的路径电阻值越低,因而电流往往会积聚于离裸芯更近的焊球上,而与裸芯距离相对更远的焊球上电流很低。在具体应用中,靠近裸芯的焊球电流过大,可能会导致电迁移、熔球等一系列问题。

3、因此,采用上述方式封装的芯片中存在距离裸芯远近不同位置的焊球电流大小不均衡的现象,而芯片内部电流不均衡的情况会使得芯片的工作稳定可靠性较差。

技术实现思路

1、有鉴于此,本发明提供一种芯片设计方法、芯片、主板及电子设备,以至少解决芯片中存在距离裸芯远近不同位置的焊球电流大小不均衡的现象,芯片的工作稳定可靠性较差的问题。

2、为达到上述目的,本发明的技术方案是这样实现的:

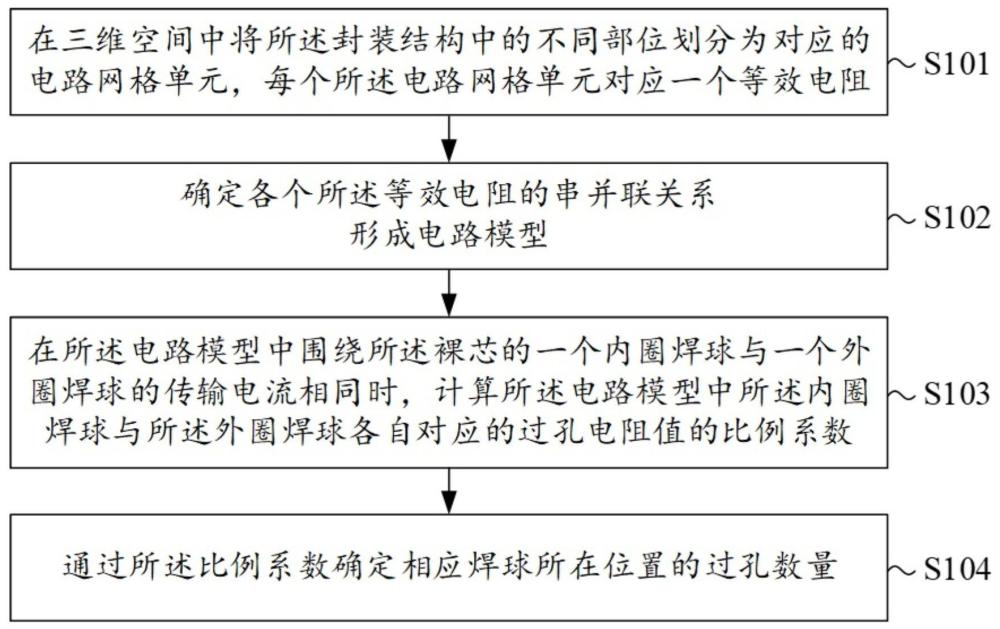

3、第一方面,本发明公开了一种芯片设计方法,所述芯片的封装结构包括封装基板上围绕裸芯设置的多圈焊球,每个焊球所在位置对应至少一个过孔,所述方法包括:

4、在三维空间中将所述封装结构中的不同部位划分为对应的电路网格单元,每个所述电路网格单元对应一个等效电阻;

5、确定各个所述等效电阻的串并联关系形成所述电路模型;

6、在所述电路模型中围绕所述裸芯的一个内圈焊球与一个外圈焊球的传输电流相同时,计算所述电路模型中所述内圈焊球与所述外圈焊球各自对应的过孔电阻值的比例系数;

7、通过所述比例系数确定相应焊球所在位置的过孔数量。

8、可选地,所述在三维空间中将所述封装结构中的不同部位划分为对应的电路网格单元,包括:

9、当所述封装结构的x方向和y方向结构相同时,在所述x方向或所述y方向与所述封装结构的z方向形成的一个二维平面内划分电路网格单元;

10、当所述封装结构的x方向和y方向结构不同时,在所述x方向和所述y方向与所述封装结构的z方向形成的两个二维平面内分别划分电路网格单元;

11、其中,所述z方向为所述封装结构的厚度方向,且x、y和z相互垂直。

12、可选地,所述电路网格单元至少包括第一网格单元、第二网格单元和第三网格单元,所述第一网格单元为所述封装结构裸芯的一个内圈焊球所在位置的过孔对应的网格单元,所述第二网格单元为与所述内圈焊球相邻的一个外圈焊球所在位置的过孔对应的网格单元,所述第三网格单元为所述内圈焊球和所述外圈焊球之间的网格单元。

13、可选地,所述确定各个所述等效电阻的串并联关系形成所述电路模型,包括:

14、确定所述第一网格单元对应的第一电阻、所述第二网格单元对应的第二电阻以及所述第三网格单元对应的第三电阻;

15、所述第二电阻与所述第三电阻串联形成第一串联支路,所述第一串联支路与所述第一电阻并联形成所述电路模型。

16、可选地,所述计算所述电路模型中所述内圈焊球与所述外圈焊球各自对应的过孔电阻值的比例系数,包括:

17、确定所述第一串联支路与所述第一电阻的阻值相同时的第一关系式;

18、根据所述第一关系式计算得到所述第一电阻和所述第二电阻的比例系数。

19、可选地,所述电路网格单元还包括第四网格单元、第五网格单元和第六网格单元,其中,所述第四网格单元为所述封装结构裸芯的一个内圈焊球所在位置的过孔对应的网格单元,所述第五网格单元为与所述内圈焊球相邻的一个外圈焊球所在位置的过孔对应的网格单元,所述第六网格单元为所述内圈焊球和所述外圈焊球之间的网格单元;

20、所述第一网格单元对应的内圈焊球和所述第二网格单元对应的外圈焊球的连线位于所述x方向,所述第四网格单元对应的内圈焊球和所述第五网格单元对应的外圈焊球的连线位于所述y方向。

21、可选地,所述确定各个所述等效电阻的串并联关系形成所述电路模型,还包括:

22、确定所述第四网格单元对应的第四电阻、所述第五网格单元对应的第五电阻以及所述第六网格单元对应的第六电阻;

23、所述第五电阻与所述第六电阻串联形成第二串联支路,所述第二串联支路与所述第四电阻并联,所述第一串联支路、所述第一电阻、所述第二串联支路以及所述第四电阻共同形成所述电路模型。

24、可选地,所述计算所述电路模型中所述内圈焊球与所述外圈焊球各自对应的过孔电阻值的比例系数,还包括:

25、确定所述第二串联支路与所述第四电阻的阻值相同时的第二关系式;

26、根据所述第二关系式计算得到所述第四电阻和所述第五电阻的比例系数。

27、第二方面,本发明公开了一种芯片,所述芯片根据前述第一方面的任一项芯片设计方法制备得到。

28、第三方面,本发明公开了一种主板,所述主板包括前述第二方面所述的芯片。

29、第四方面,本发明公开了一种电子设备,所述电子设备包括前述第二方面所述的芯片。

30、相对于现有技术,本发明实施例所述的芯片设计方法、芯片、主板及电子设备具有以下优势:

31、本发明实施例中,通过将芯片的封装结构的不同部位划分为对应的电路网格单元,根据每个电路网格单元对应的等效电阻的串并联关系建立电路模型,可利用电路模型计算得到距离封装结构中裸芯远近不同位置的内圈焊球和外圈焊球各自对应的过孔电阻值的比例系数,从而计算确定出相应焊球所在位置的过孔数量,实现距离裸芯远近不同位置的过孔数量的合理分布,有助于改善距离裸芯远近不同位置的焊球电流大小不均衡的现象,可以提升芯片的工作稳定可靠性。

技术特征:

1.一种芯片设计方法,其特征在于,所述芯片的封装结构包括封装基板上围绕裸芯设置的多圈焊球,每个焊球所在位置对应至少一个过孔,所述方法包括:

2.根据权利要求1所述的芯片设计方法,其特征在于,所述在三维空间中将所述封装结构中的不同部位划分为对应的电路网格单元,包括:

3.根据权利要求2所述的芯片设计方法,其特征在于,所述电路网格单元至少包括第一网格单元、第二网格单元和第三网格单元,所述第一网格单元为所述封装结构裸芯的一个内圈焊球所在位置的过孔对应的网格单元,所述第二网格单元为与所述内圈焊球相邻的一个外圈焊球所在位置的过孔对应的网格单元,所述第三网格单元为所述内圈焊球和所述外圈焊球之间的网格单元。

4.根据权利要求3所述的芯片设计方法,其特征在于,所述确定各个所述等效电阻的串并联关系形成所述电路模型,包括:

5.根据权利要求4所述的芯片设计方法,其特征在于,所述计算所述电路模型中所述内圈焊球与所述外圈焊球各自对应的过孔电阻值的比例系数,包括:

6.根据权利要求4-5任一项所述的芯片设计方法,其特征在于,所述电路网格单元还包括第四网格单元、第五网格单元和第六网格单元,其中,所述第四网格单元为所述封装结构裸芯的一个内圈焊球所在位置的过孔对应的网格单元,所述第五网格单元为与所述内圈焊球相邻的一个外圈焊球所在位置的过孔对应的网格单元,所述第六网格单元为所述内圈焊球和所述外圈焊球之间的网格单元;

7.根据权利要求6所述的芯片设计方法,其特征在于,所述确定各个所述等效电阻的串并联关系形成所述电路模型,还包括:

8.根据权利要求7所述的芯片设计方法,其特征在于,所述计算所述电路模型中所述内圈焊球与所述外圈焊球各自对应的过孔电阻值的比例系数,还包括:

9.一种芯片,其特征在于,所述芯片根据权利要求1至8任一项所述的芯片设计方法制备得到。

10.一种主板,其特征在于,所述主板包括权利要求9所述的芯片。

11.一种电子设备,其特征在于,所述电子设备包括权利要求9所述的芯片。

技术总结

本发明提供了一种芯片设计方法、芯片、主板及电子设备,属于芯片封装技术领域。封装结构包括封装基板上围绕裸芯设置的多圈焊球,每个焊球所在位置至少对应一个过孔。芯片设计方法包括:在三维空间中将封装结构中的不同部位划分为对应的电路网格单元,每个电路网格单元对应一个等效电阻;确定各个等效电阻的串并联关系形成电路模型;在电路模型中围绕裸芯的一个内圈焊球与一个外圈焊球的传输电流相同时,计算电路模型中内圈焊球与外圈焊球各自对应的过孔电阻值的比例系数;通过比例系数确定相应焊球所在位置的过孔数量。本发明实施例的芯片设计方法,有助于改善距离裸芯远近不同位置的焊球电流大小不均衡的现象,可以提升芯片的工作稳定可靠性。

技术研发人员:门扬,符兴建

受保护的技术使用者:龙芯中科(北京)信息技术有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!