一种高速串行数据收发系统及时序自适应方法与流程

本发明高速串行数据的收发,特别是涉及一种高速串行数据收发系统及时序自适应方法。

背景技术:

1、随着电子技术的发展,数字电路逐渐成为整个电子信息系统的重要组成部分,在系统级设备工作过程当中,芯片与芯片之间以及模块与模块之间需要进行数据收发,数据收发的正确性及稳定性直接决定了设备是否能正常运行。数字电路向集成化和高速化飞速发展,数据传输速率越来越高,数据接口的稳定采样窗口不断缩短,数据接收的难度也就越来越高。

2、在高速数据收发过程中为了保证信号传输质量,一般采用差分信号进行传输,在大多应用环境下为了减少数据线的数量通常采用串行传输,并行数据串行化以后数据传输速率进一步提高,数据正确收发的难度进一步增加,同时高速串行数据的串并转换的稳定性和可靠性,也直接影响了系统的稳定工作。

3、因为fpga内串并转换的逻辑电路布局布线以及数字板卡布局走线的影响,高速串行数据收发过程中数据信号和时钟信号通常会经历不同的延迟,这导致接收端的时钟数据之间的保持时间和建立时间余量很难得到保证,导致接收数据存在毛刺甚至全部错误。此外,串并转换过程在可编程芯片内实现,同样的逻辑代码经过多次编译的结果可能出现不同的逻辑布局和布线,进一步增加了数据可靠传输的难度。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供一种高速串行数据收发系统及时序自适应方法,避免高速数字电路中的现场可编程逻辑阵列芯片fpga与外部设备(外部设备也可以是fpga)进行高速串行数据收发时,接收数据出现毛刺或完全错误的问题。

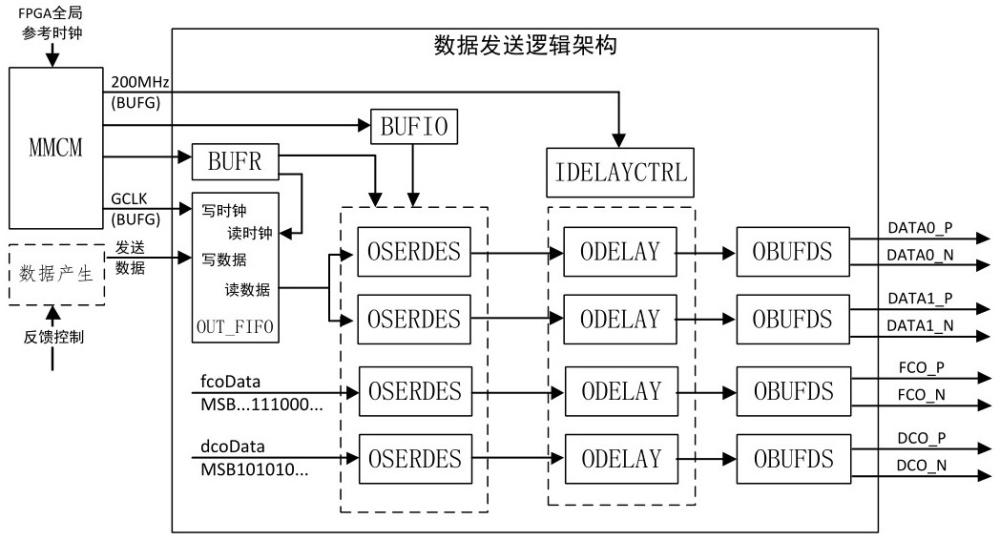

2、本发明的目的是通过以下技术方案来实现的:一种高速串行数据收发系统,包括发送端和接收端;

3、所述发送端包括:

4、发送端时钟网络,包括发送端区域时钟网络bufr1和发送端io专用时钟网络bufio1;

5、发送端时钟管理器,用于接收来自时钟源的时钟信号,并产生两个时钟分别接入区域时钟网络bufr1和io专用时钟网络bufio1,分别作为收发逻辑的并行数据和串行数据的同步时钟;

6、数据产生模块,用于产生发送数据,并传输给输出fifo缓存out_fifo;发送数据是测试数据或用户需要发送的业务数据;

7、输出fifo缓存模块out_fifo,用于完成发送数据缓存,以及全局时钟域到区域时钟域的转换;

8、输出并行转串行逻辑资源模块oserdes,用于{101010…}数据、{111…000…}数据以及在bufr1读取out_fifo中缓存的数据送至oserdes时,完成并行数据到串行数据的转换,串行数据同步时钟使用bufio提供的时钟,采用双边沿同步方式;

9、输出延迟器odelay,用于接收oserdes输出的串行数据信号, 并调用idelayctrl逻辑配合odelay来实现延迟自动校准后传输给差分输出缓冲器obufds;

10、差分输出缓冲器obufds,用于将输出延迟器odelay输出的信号转化为差分信号{datax_p,datax_n}、{fco_p,fco_n}、{dco_p,dco_n},并传输给接收端;其中,{datax_p,datax_n}是由fifo中读出来的数据经过并行转串行而来,对应的是发送的数据;{fco_p,fco_n}是由{111…000…}数据经过并行转串行而来用于作为接收端的帧同步时钟fco,{dco_p,dco_n}是由{101010…}数据经过并行转串行而来用于作为接收端的比特同步时钟dco;

11、数据发送过程为:数据产生模块产生测试数据或选择需要发送的业务数据(发送数据可由接收端到发送端的低速控制口进行控制),通过全局时钟(或用户使用的时钟)写入out_fifo对数据进行缓存,bufr1从out_fifo中读取数据送入oserdes,同时将{1010…}并行序列和 {11…00…}并行序列也送入oserdes(用于产生帧同步和比特同步时钟信号),所有oserdes将其输入的并行数据转化为串行数据,并将串行数据信号接入odelay对各个信号进行延迟(延迟值可由接收端到发送端的低速控制口进行控制),最后利用obufds将延迟后的信号转化为差分信号通过发送端的io口管脚{datax_p,datax_n}、{fco_p,fco_n}、{dco_p,dco_n}输出。

12、所述接收端包括:

13、接收端时钟网络,包括接收端区域时钟网络bufr2和接收端io专用时钟网络bufio2;

14、接收端时钟管理器,用于接收来自接收端的时钟管脚{fco_p,fco_n}、{dco_p,dco_n}的时钟信号,并产生两个时钟分别接入区域时钟网络bufr2和io专用时钟网络bufio2,分别作为收发逻辑的并行数据和串行数据的同步时钟;

15、差分输入缓冲器ibufds,用于将接收到的时钟和数据差分信号{datax_p,datax_n}、{fco_p,fco_n}、{dco_p,dco_n}转换为单端信号;

16、输入延迟器idelay,用于对来自差分输入缓冲器ibufds的信号进行延时处理,并调用idelayctrl逻辑配合idelay来实现延迟自动校准;idelay输出的fco和dco信后分别接入区域时钟网络bufr和io专用时钟网络bufio,bufr作为串并转换的起始标志和并行数据同步时钟,bufio则作为串并转换的串行数据同步时钟;

17、所述输入串并转换器iserdes,用于将经过idelay后的串行数据datax转换为并行数据,串并转换器的串行数据帧起始控制时钟及并行数据同步时钟为bufr;

18、输入专用缓存in_fifo,用于缓存同bank内iserdes输出的并行数据;

19、数据接收模块,用于读取in_fifo的数据,得到接收数据,读取时钟速率大于或等于并行数据率。

20、数据接收过程为:接收端的io口管脚信号{datax_p,datax_n}、{fco_p,fco_n}、{dco_p,dco_n}通过ibufds转化为单端信号,单端信号通过idelay进行延迟得到延时后的信号datax、fco、dco,fco和dco分别接入bufr和bufio作为后续逻辑的驱动时钟,接收数据信号dco进入iserdes进行串并后输出并行数据,通过bufr区域时钟将并行数据写入到in_fifo进行缓存,最后利用全局时钟(用户业务使用的处理时钟)从in_fifo钟读取出接收数据,至此数据接收完成。

21、一种高速串行数据收发系统的时序自适应方法,包括以下步骤:

22、s1.上电等待时钟及各个逻辑初始化完成后,初始化dco的延迟值delay=0,连续收发l个数据的测试实验成功次数t=0;

23、s2.将delay值载入接收端dco的idelay,接收端通过反馈支路通知发送端发送测试数据序列;

24、s3.接收端连续判断接收数据是否为发送端发送的测试数据,如果接收到的数据不等于发送端发送的测试数据,则delay值自增1,测试成功计算t清0,返回步骤s2;如果连续l个数据都收发成功,则进入步骤s4;

25、s4.测试成功次数t自增1,然后更新第t个记录寄存器delayreg(t)的值为当前的delay值;

26、s5. 如果t大于等于预设门限m,则进入步骤s6,否则delay值自增1进入步骤s2;

27、s6. 取第m/2+1个delayreg的值载入接收端dco的idelay,反馈支路通知发送端进入正常数据收发,自适应过程完成。

28、本发明的有益效果是: 1)收发数据的所有逻辑资源及缓存均使用fpga的iob资源实现,并且利用位置约束方法将逻辑资源的位置进行指定和固定,实现最优布局和最短走线,多次编译的布局和走线位置不变,可以解决同一个fpga逻辑代码工程进行多次编译,某次编译结果的数据传输异常问题。

29、2)数据收发的所有对外时钟和数据信号均有输入或输出延迟器idelay或odelay,可对各信号线进行单独延迟控制,且延迟控制精度为皮秒级别,通过延迟控制可以有效解决数据信号和时钟信号在数字板卡上先天走线不等长而导致的数据传输异常的问题;

30、3)设计时钟和数据之间时序的自适应逻辑,对并行时钟的延迟器的延迟值进行遍历式重载,寻找时钟信号与数据信号之际的最优捕获时序,克服时钟信号与数据信号时序余量不足而导致数据传输在不同温度下出现异常的问题,实现数据传输的全温可靠性。

- 还没有人留言评论。精彩留言会获得点赞!