MCU高位数整型除法器的加速方法及装置与流程

本技术涉及mcu运算,特别是涉及一种mcu高位数整型除法器的加速方法及装置。

背景技术:

1、随着mcu性能不断提高,mcu计算整型数除法已越来越快,原因是一般内置与mcu位数相同位的硬件除法器,mcu均能在少于10个指令周期完成计算,对于如某些arm 或ti dsp内核甚至能实现单周期除法性能。例如,位数为32位的arm-m4内核mcu,对于低于32位整型数的除法计算,能通过硬件除法器实现极快的除法运算。

2、但对于更高位的64位整型除法计算,mcu一般由纯软件来实现,耗时特别长。也就是说,对于这种高于mcu位数的除法计算,mcu除法存在计算周期不固定的问题,如arm-m4内核32位mcu计算64位整型除法耗时约为1700~2800个指令周期,并且除法计算周期长,会制约更低主频mcu应用于实时性要求高的高位数除法应用场合,诸如高性能伺服、变频器等环路计算。

技术实现思路

1、基于此,有必要针对mcu高位数整型除法器计算周期长且不稳定的问题,提供一种mcu高位数整型除法器的加速方法及装置。

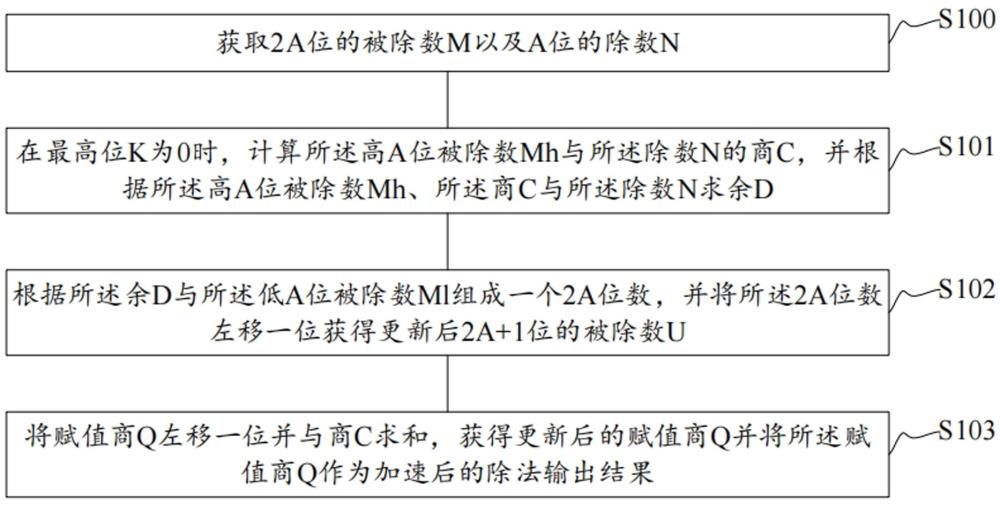

2、本公开实施例提供了一种mcu高位数整型除法器的加速方法,包括步骤:

3、获取2a位的被除数m以及a位的除数n;其中,a为正整数;所述被除数m包括高a位被除数mh和低a位被除数ml;

4、在最高位k为0时,计算所述高a位被除数mh与所述除数n的商c,并根据所述高a位被除数mh、所述商c与所述除数n求余d;其中,初始的最高位k赋值为0;

5、根据所述余d与所述低a位被除数ml组成一个2a位数,并将所述2a位数左移一位获得更新后2a+1位的被除数u;其中,所述被除数u包括更新后的最高位k、更新后的高a位被除数mh和更新后的低a位被除数ml;所述被除数u用于更新替换所述被除数m;

6、将赋值商q左移一位并与商c求和,获得更新后的赋值商q并将所述赋值商q作为加速后的除法输出结果。

7、本公开实施例的mcu高位数整型除法器的加速方法,获取2a位的被除数m以及a位的除数n;其中,a为正整数;被除数m包括高a位被除数mh和低a位被除数ml;在最高位k为0时,计算高a位被除数mh与除数n的商c,并根据高a位被除数mh、商c与除数n求余d;其中,初始的最高位k赋值为0;根据余d与低a位被除数ml组成一个2a位数,并将2a位数左移一位获得更新后2a+1位的被除数u;其中,被除数u包括更新后的最高位k、更新后的高a位被除数mh和更新后的低a位被除数ml;被除数u用于更新替换被除数m;将赋值商q左移一位并与商c求和,获得更新后的赋值商q并将赋值商q作为加速后的除法输出结果。由此,降低除法计算周期并提高稳定性。

8、作为其中一个可选的实施例,所述获取2a位的被除数m以及a位的除数n的过程,包括步骤:

9、在检测到除法符号时,获取原始被除数与原始除数,并求所述原始被除数的绝对值和所述原始除数的绝对值;

10、将所述绝对值以a位mcu存储方式存储,以分别获得2a位的被除数m以及a位的除数n。

11、作为其中一个可选的实施例,所述获取2a位的被除数m以及a位的除数n的过程,包括步骤:

12、在未检测到除法符号时,获取以a位mcu存储方式存储的2a位的被除数m以及a位的除数n。

13、作为其中一个可选的实施例,还包括步骤:

14、在最高位k为0时,所述商c为1,所述余d为所述高a位被除数mh与所述除数n的差值。

15、作为其中一个可选的实施例,所述将赋值商q左移一位并与商c求和,获得更新后的赋值商q并将所述赋值商q作为加速后的除法输出结果的过程,包括步骤:

16、检测所述被除数m的更新次数;

17、在所述更新次数为a+1次时,将所述赋值商q作为加速后的除法输出结果。

18、作为其中一个可选的实施例,所述将赋值商q左移一位并与商c求和,获得更新后的赋值商q并将所述赋值商q作为加速后的除法输出结果的过程,包括步骤:

19、检测商符号性,根据商符号性调整更新后的赋值商q;

20、将调整后的赋值商q作为加速后的除法输出结果。

21、作为其中一个可选的实施例,所述a为32。

22、本公开实施例提供了一种mcu高位数整型除法器的加速装置,包括:

23、数据获取模块,用于获取2a位的被除数m以及a位的除数n;其中,a为正整数;所述被除数m包括高a位被除数mh和低a位被除数ml;

24、一次计算模块,用于在最高位k为0时,计算所述高a位被除数mh与所述除数n的商c,并根据所述高a位被除数mh、所述商c与所述除数n求余d;其中,初始的最高位k赋值为0;

25、二次计算模块,用于根据所述余d与所述低a位被除数ml组成一个2a位数,并将所述2a位数左移一位获得更新后2a+1位的被除数u;其中,所述被除数u包括更新后的最高位k、更新后的高a位被除数mh和更新后的低a位被除数ml;所述被除数u用于更新替换所述被除数m;

26、商值输出模块,用于将赋值商q左移一位并与商c求和,获得更新后的赋值商q并将所述赋值商q作为加速后的除法输出结果。

27、上述的mcu高位数整型除法器的加速装置,获取2a位的被除数m以及a位的除数n;其中,a为正整数;被除数m包括高a位被除数mh和低a位被除数ml;在最高位k为0时,计算高a位被除数mh与除数n的商c,并根据高a位被除数mh、商c与除数n求余d;其中,初始的最高位k赋值为0;根据余d与低a位被除数ml组成一个2a位数,并将2a位数左移一位获得更新后2a+1位的被除数u;其中,被除数u包括更新后的最高位k、更新后的高a位被除数mh和更新后的低a位被除数ml;被除数u用于更新替换被除数m;将赋值商q左移一位并与商c求和,获得更新后的赋值商q并将赋值商q作为加速后的除法输出结果。由此,降低除法计算周期并提高稳定性。

28、本公开至少一个实施例还提供一种数据控制装置,包括:

29、一个或多个存储器,非瞬时性地存储有计算机可执行指令;

30、一个或多个处理器,配置为运行计算机可执行指令,其中,计算机可执行指令被一个或多个处理器运行时实现根据本公开任一实施例的mcu高位数整型除法器的加速方法。

31、上述的数据控制装置,获取2a位的被除数m以及a位的除数n;其中,a为正整数;被除数m包括高a位被除数mh和低a位被除数ml;在最高位k为0时,计算高a位被除数mh与除数n的商c,并根据高a位被除数mh、商c与除数n求余d;其中,初始的最高位k赋值为0;根据余d与低a位被除数ml组成一个2a位数,并将2a位数左移一位获得更新后2a+1位的被除数u;其中,被除数u包括更新后的最高位k、更新后的高a位被除数mh和更新后的低a位被除数ml;被除数u用于更新替换被除数m;将赋值商q左移一位并与商c求和,获得更新后的赋值商q并将赋值商q作为加速后的除法输出结果。由此,降低除法计算周期并提高稳定性。

32、本公开至少一个实施例还提供一种非瞬时性计算机可读存储介质,其中,非瞬时性计算机可读存储介质存储有计算机可执行指令,计算机可执行指令被处理器执行时实现根据本公开任一实施例的mcu高位数整型除法器的加速方法。

33、上述的非瞬时性计算机可读存储介质,获取2a位的被除数m以及a位的除数n;其中,a为正整数;被除数m包括高a位被除数mh和低a位被除数ml;在最高位k为0时,计算高a位被除数mh与除数n的商c,并根据高a位被除数mh、商c与除数n求余d;其中,初始的最高位k赋值为0;根据余d与低a位被除数ml组成一个2a位数,并将2a位数左移一位获得更新后2a+1位的被除数u;其中,被除数u包括更新后的最高位k、更新后的高a位被除数mh和更新后的低a位被除数ml;被除数u用于更新替换被除数m;将赋值商q左移一位并与商c求和,获得更新后的赋值商q并将赋值商q作为加速后的除法输出结果。由此,降低除法计算周期并提高稳定性。

- 还没有人留言评论。精彩留言会获得点赞!