一种SFGT存储阵列和存储芯片的制作方法

本申请涉及存储,尤其涉及一种sfgt存储阵列和存储芯片。

背景技术:

1、半浮栅晶体管(semi-floating gate transistor,sfgt)是介于金属-氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)和浮栅晶体管(floating gate transistor)之间的晶体管。sfgt可以用来存储数据,其主要在字线(word line)、位线(bit line)加不同的电压来工作。可以将sfgt集成为存储阵列,进而可以实现大量的数据存储。

2、现有技术中,在读取sfgt存储阵列中的存储单元内所存储的数据时,由于sfgt存储阵列的位线较长,导致从存储单元读取出的信号比较微弱,使得读取数据的过程耗时较长,读取数据的效率较低。

技术实现思路

1、本发明提供了一种sfgt存储阵列和存储芯片,以解决现有技术中存在的在读取sfgt存储阵列中的存储单元内所存储的数据时,由于sfgt存储阵列的位线较长,导致从存储单元读取出的信号比较微弱,使得读取数据的过程耗时较长,读取数据的效率较低的技术问题。

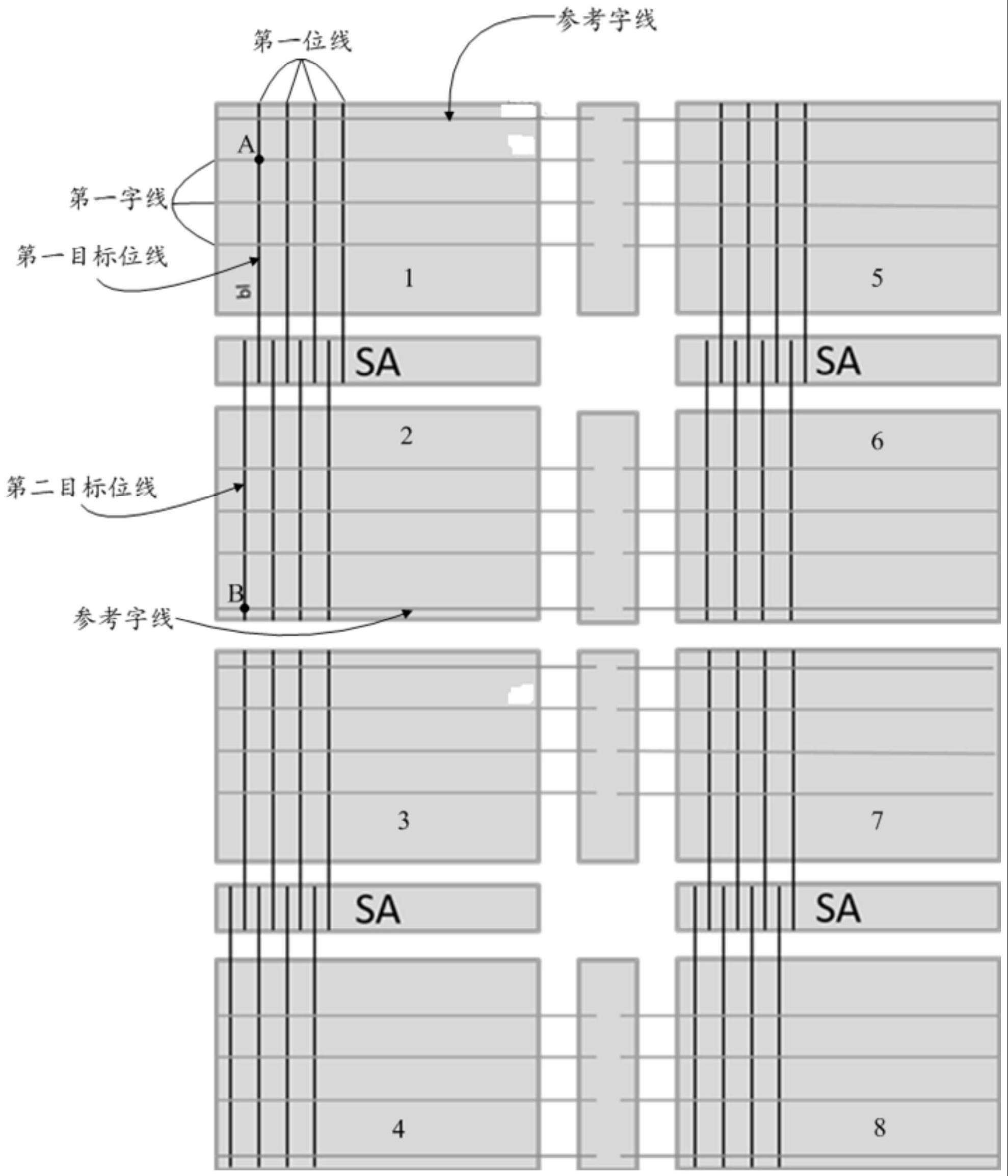

2、第一方面,本发明提供了一种sfgt存储阵列,所述sfgt存储阵列包含真实半浮栅阵列、参考半浮栅阵列和灵敏放大器;

3、所述真实半浮栅阵列包含多个真实半浮栅存储单元、多条第一位线和多条第一字线,所述多条第一位线中的每条第一位线和所述多条第一字线中的每条第一字线相交设置,用于对所述真实半浮栅存储单元进行操作,所述多条第一位线中的每条第一位线与所述灵敏放大器的第一输入端连接,所述真实半浮栅存储单元设置在所述第一位线和所述第一字线相交的位置;

4、所述参考半浮栅阵列包含多条第二位线,所述多条第二位线中的每条第二位线与所述灵敏放大器的第二输入端连接。

5、可选的,所述参考半浮栅阵列包含多个参考半浮栅存储单元和参考字线,所述多条第二位线中的每条第二位线与所述参考字线相交设置,用于对所述参考半浮栅存储单元进行操作,所述参考半浮栅存储单元设置在所述第二位线和所述参考字线相交的位置。

6、可选的,所述真实半浮栅阵列、所述参考半浮栅阵列和所述灵敏放大器一一对应。

7、可选的,所述真实半浮栅阵列对应第一参考半浮栅阵列和第二参考半浮栅阵列;

8、所述真实半浮栅阵列所包含的多条第一位线中的奇数序号第一位线与第一灵敏放大器的第一输入端连接,所述真实半浮栅阵列所包含的多条第一位线中的偶数序号第一位线与第二灵敏放大器的第一输入端连接;

9、所述第一参考半浮栅阵列所包含的多条第二位线中的每条第二位线与所述第一灵敏放大器的第二输入端连接;

10、所述第二参考半浮栅阵列所包含的多条第二位线中的每条第二位线与所述第二灵敏放大器的第二输入端连接。

11、第二方面,本发明提供了一种存储芯片,包括:sfgt存储阵列、列译码模块、行译码模块和逻辑控制模块;

12、所述逻辑控制模块分别通过所述列译码模块和所述行译码模块与所述sfgt存储阵列连接,用于根据访问指令对所述sfgt存储阵列进行以页为单位的写入和读取;

13、所述sfgt存储阵列包含真实半浮栅阵列、参考半浮栅阵列和灵敏放大器;

14、所述真实半浮栅阵列包含多个真实半浮栅存储单元、多条第一位线和多条第一字线,所述多条第一位线中的每条第一位线和所述多条第一字线中的每条第一字线相交设置,用于对所述真实半浮栅存储单元进行操作,所述多条第一位线中的每条第一位线与所述灵敏放大器的第一输入端连接,所述真实半浮栅存储单元设置在所述第一位线和所述第一字线相交的位置;

15、所述参考半浮栅阵列包含多条第二位线,所述多条第二位线中的每条第二位线与所述灵敏放大器的第二输入端连接。

16、可选的,所述存储芯片还包括电路模块,所述电路模块与所述列译码模块、所述行译码模块和所述逻辑控制模块连接,所述电路模块用于为所述列译码模块、所述行译码模块和所述逻辑控制模块提供电压。

17、可选的,所述存储芯片还包括数据传输路径,所述数据传输路径与所述列译码模块和所述逻辑控制模块连接。

18、可选的,所述存储芯片还包括地址输入接口,所述地址输入接口与所述行译码模块和所述逻辑控制模块连接。

19、可选的,所述存储芯片还包括外部接口命令译码电路,所述外部接口命令译码电路与所述逻辑控制模块连接。

20、可选的,所述存储芯片还包括输入输出接口,所述输入输出接口与所述数据传输路径连接。

21、由以上技术方案可知,本发明实施例提供的一种sfgt存储阵列和存储芯片,所述sfgt存储阵列包含真实半浮栅阵列、参考半浮栅阵列和灵敏放大器;所述真实半浮栅阵列包含多个真实半浮栅存储单元、多条第一位线和多条第一字线,所述多条第一位线中的每条第一位线和所述多条第一字线中的每条第一字线相交设置,用于对所述真实半浮栅存储单元进行操作,所述多条第一位线中的每条第一位线与所述灵敏放大器的第一输入端连接,所述真实半浮栅存储单元设置在所述第一位线和所述第一字线相交的位置;所述参考半浮栅阵列包含多条第二位线,所述多条第二位线中的每条第二位线与所述灵敏放大器的第二输入端连接。这样,真实半浮栅阵列所包含的多条第一位线中的每条第一位线与灵敏放大器的第一输入端连接,且参考半浮栅阵列所包含的多条第二位线中的每条第二位线与灵敏放大器的第二输入端连接。即在读取sfgt存储阵列中的存储单元内所存储的数据时,可以通过灵敏放大器对从存储单元读取出的信号进行放大。可以减少读取数据的过程的耗时,提高读取数据的效率。

技术特征:

1.一种sfgt存储阵列,其特征在于,所述sfgt存储阵列包含真实半浮栅阵列、参考半浮栅阵列和灵敏放大器;

2.根据权利要求1所述的sfgt存储阵列,其特征在于,所述参考半浮栅阵列包含多个参考半浮栅存储单元和参考字线,所述多条第二位线中的每条第二位线与所述参考字线相交设置,用于对所述参考半浮栅存储单元进行操作,所述参考半浮栅存储单元设置在所述第二位线和所述参考字线相交的位置。

3.根据权利要求2所述的sfgt存储阵列,其特征在于,所述真实半浮栅阵列、所述参考半浮栅阵列和所述灵敏放大器一一对应。

4.根据权利要求2所述的sfgt存储阵列,其特征在于,所述真实半浮栅阵列对应第一参考半浮栅阵列和第二参考半浮栅阵列;

5.一种存储芯片,其特征在于,包括:

6.根据权利要求5所述的存储芯片,其特征在于,所述存储芯片还包括电路模块,所述电路模块与所述列译码模块、所述行译码模块和所述逻辑控制模块连接,所述电路模块用于为所述列译码模块、所述行译码模块和所述逻辑控制模块提供电压。

7.根据权利要求6所述的存储芯片,其特征在于,所述存储芯片还包括数据传输路径,所述数据传输路径与所述列译码模块和所述逻辑控制模块连接。

8.根据权利要求7所述的存储芯片,其特征在于,所述存储芯片还包括地址输入接口,所述地址输入接口与所述行译码模块和所述逻辑控制模块连接。

9.根据权利要求8所述的存储芯片,其特征在于,所述存储芯片还包括外部接口命令译码电路,所述外部接口命令译码电路与所述逻辑控制模块连接。

10.根据权利要求9所述的存储芯片,其特征在于,所述存储芯片还包括输入输出接口,所述输入输出接口与所述数据传输路径连接。

技术总结

本申请公开了一种SFGT存储阵列和存储芯片,SFGT存储阵列包含真实半浮栅阵列、参考半浮栅阵列和灵敏放大器;真实半浮栅阵列包含多个真实半浮栅存储单元、多条第一位线和多条第一字线,多条第一位线中的每条第一位线和多条第一字线中的每条第一字线相交设置,用于对真实半浮栅存储单元进行操作,多条第一位线中的每条第一位线与灵敏放大器的第一输入端连接,真实半浮栅存储单元设置在第一位线和第一字线相交的位置;参考半浮栅阵列包含多条第二位线,多条第二位线中的每条第二位线与灵敏放大器的第二输入端连接。在读取SFGT存储阵列中的存储单元内所存储的数据时,可以通过灵敏放大器对从存储单元读取出的信号进行放大,可以提高读取数据的效率。

技术研发人员:拜福君,俞冰,赵善真

受保护的技术使用者:西安紫光国芯半导体有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!