存储器的制作方法

本公开实施例涉及半导体,特别涉及一种存储器。

背景技术:

1、半导体存储器由许多重复的存储单元组成,每个存储单元通常包括电容器和晶体管,晶体管的栅极与字线相连、漏极与位线相连、源极与电容器相连,字线上的电压信号能够控制晶体管的打开或关闭,进而通过位线读取存储在电容器中的数据信息,或者通过位线将数据信息写入到电容器中进行存储。

2、半导体存储器可以分为非易失性存储和易失性存储。动态随机存取存储器(dynamic random access memory,dram)作为易失性存储,具备存储密度高、读写速度快等优点,广泛用于各种电子系统中。dram可以分为双倍速率同步(double data rate,ddr)动态随机存储器、gddr(graphics double data rate)动态随机存储器、低功耗双倍速率同步(low power double data rate,lpddr)动态随机存储器。

技术实现思路

1、本公开实施例提供一种存储器,至少有利于改善存储器的存储性能。

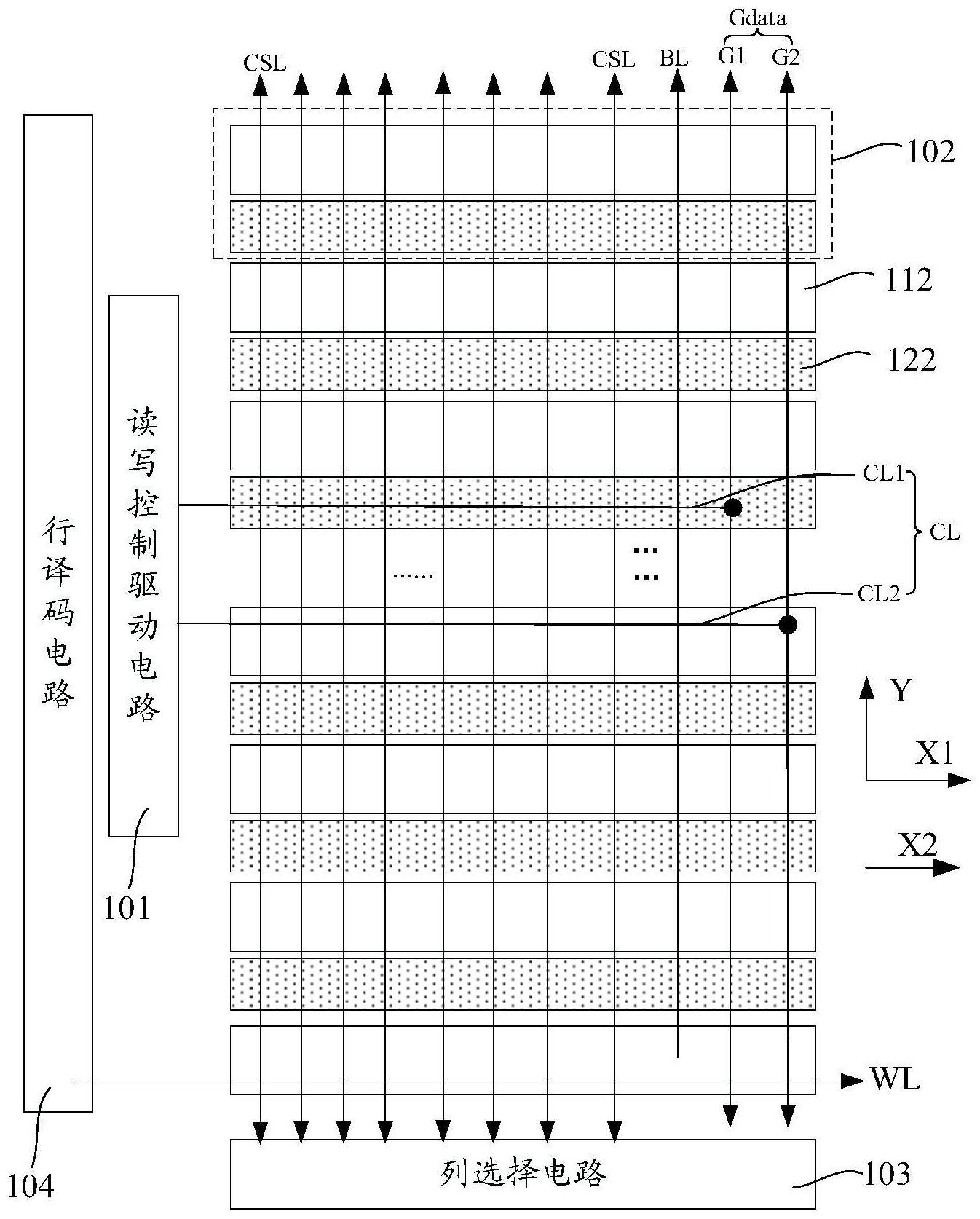

2、根据本公开的一些实施例,本公开一些实施例提供一种存储器,包括:沿第一方向延伸的位线以及沿第二方向延伸的字线;沿所述第一方向排布的列选择电路以及多个存储模块,所述存储模块包括:沿所述第一方向排布的存储阵列以及放大器阵列,所述存储阵列包括至少一个存储单元,所述放大器阵列包括至少一个放大单元,每一所述位线与相应的所述放大单元的一端电连接,每一所述字线与相应的所述存储单元电连接;沿所述第一方向延伸的列选择线,所述列选择线电连接所述列选择电路,所述列选择电路经由所述列选择线驱动相应的所述放大单元;读写控制驱动电路,所述读写控制驱动电路与所述列选择电路分别位于所述多个存储模块的相邻侧;沿所述第二方向延伸的全局数据线以及沿第三方向延伸的电连接线,所述全局数据线经由所述电连接线电连接所述读写控制驱动电路,所述读写控制驱动电路用于驱动与所述全局数据线相对应的所述存储模块,以使数据经由所述全局数据线写入至所述存储单元内,或者,以从所述存储单元内读出数据并将所述数据传输至所述全局数据线。

3、在一些实施例中,在沿所述第一方向上,多个所述存储模块按照自然数递增顺序排序,处于奇数位置的所述存储模块定义为第一存储模块,处于偶数位置的所述存储模块定义为第二存储模块;所述全局数据线包括:第一全局数据线,所述第一全局数据线与所述第一存储模块相对应;第二全局数据线,所述第二全局数据线与所述第二存储模块相对应;所述电连接线包括:第一电连接线,所述第一电连接线电连接所述第一全局数据线与所述读写控制驱动电路;第二电连接线,所述第二电连接线电连接所述第二全局数据线与所述读写控制驱动电路。

4、在一些实施例中,每一条所述第一全局数据线与所有所述第一存储模块相对应;每一条所述第二全局数据线与所有所述第二存储模块相对应。

5、在一些实施例中,所述第一全局数据线以及所述第二全局数据线的数量均为多条,其中每条所述第一全局数据线与部分数量的所述第一存储模块相对应,每条所述第二全局数据线与部分数量的所述第二存储模块相对应。

6、在一些实施例中,所述读写控制驱动电路包括:沿所述第一方向排布的多个读写控制驱动单元,每一所述读写控制驱动单元电连接至少一条所述第一全局数据线以及至少一条所述第二全局数据线。

7、在一些实施例中,与不同的所述读写控制驱动单元电连接的所述全局数据线之间间隔分布。

8、在一些实施例中,所述全局数据线为多条,且所有所述全局数据线均分布于多个所述存储模块的边缘。

9、在一些实施例中,多个所述存储模块划分为沿所述第一方向排布的至少两个模块区域,每一所述模块区域包括至少两个所述存储模块,且不同的所述模块区域具有的所述全局数据线相互独立;所述读写控制驱动电路包括:沿所述第一方向排布的至少两个读写控制驱动模块,每一所述读写控制驱动模块位于相应的所述模块区域的一侧,所述读写控制驱动模块经由所述电连接线与相应的所述全局数据线电连接。

10、在一些实施例中,所述读写控制驱动电路被配置为,当所述模块区域对应的所述字线被使能时,则与所述模块区域对应的所述读写控制驱动模块经由所述全局数据线驱动所述模块区域内的所述存储模块。

11、在一些实施例中,同一所述模块区域具有多条所述全局数据线,且多条所述全局数据线分为至少两组,每一组所述全局数据线与至少两个相邻的所述存储模块相对应。

12、在一些实施例中,对于同一所述模块区域,所有所述全局数据线相邻排布,或者,不同组的所述全局数据线间隔排布。

13、在一些实施例中,对于同一所述模块区域,所述读写控制驱动模块包括沿所述第一方向排布的多个读写控制驱动单元,且每一所述读写控制驱动单元电连接至少一组所述全局数据线。

14、在一些实施例中,每一所述模块区域包含的所述存储模块的数量相同。

15、在一些实施例中,所述第三方向与所述第二方向相同。

16、在一些实施例中,所述第一方向与所述第二方向相垂直。

17、在一些实施例中,还包括:行译码电路,所述行译码电路用于通过所述字线选中与所述字线电连接的所述存储单元;所述行译码电路位于所述读写控制驱动电路远离多个所述存储模块的一侧。

18、本公开实施例提供的技术方案具有以下优点:

19、本公开实施例提供一种结构性能优越的存储器,列选择电路以及多个存储模块沿第一方向品牌部,读写控制驱动电路与列选择电路分别位于多个存储模块的相邻侧,全局数据线沿第二方向延伸,电连接线沿第三方向延伸,且全局数据线经由电连接线电连接读写控制驱动电路,读写控制驱动电路用于驱动与全局数据线相对应的存储模块。由于读写控制驱动电路与列选择电路位于多个存储模块的相邻侧,使得存储器对应的芯片布局更为灵活;此外,全局数据线与电连接线构成t型(t shape)结构,读写控制驱动电路驱动处于首尾的存储模块所需的信号传输路径差异较小,改善了读写控制驱动电路驱动的rc延迟特性,有利于提升存储器的读写速度。

技术特征:

1.一种存储器,其特征在于,包括:

2.如权利要求1所述的存储器,其特征在于,在沿所述第一方向上,多个所述存储模块按照自然数递增顺序排序,处于奇数位置的所述存储模块定义为第一存储模块,处于偶数位置的所述存储模块定义为第二存储模块;

3.如权利要求2所述的存储器,其特征在于,每一条所述第一全局数据线与所有所述第一存储模块相对应;每一条所述第二全局数据线与所有所述第二存储模块相对应。

4.如权利要求2所述的存储器,其特征在于,所述第一全局数据线以及所述第二全局数据线的数量均为多条,其中每条所述第一全局数据线与部分数量的所述第一存储模块相对应,每条所述第二全局数据线与部分数量的所述第二存储模块相对应。

5.如权利要求4所述的存储器,其特征在于,所述读写控制驱动电路包括:

6.如权利要求4所述的存储器,其特征在于,与不同的所述读写控制驱动单元电连接的所述全局数据线之间间隔分布。

7.如权利要求1所述的存储器,其特征在于,所述全局数据线为多条,且所有所述全局数据线均分布于多个所述存储模块的边缘。

8.如权利要求1所述的存储器,其特征在于,多个所述存储模块划分为沿所述第一方向排布的至少两个模块区域,每一所述模块区域包括至少两个所述存储模块,且不同的所述模块区域具有的所述全局数据线相互独立;

9.如权利要求8所述的存储器,其特征在于,所述读写控制驱动电路被配置为,当所述模块区域对应的所述字线被使能时,则与所述模块区域对应的所述读写控制驱动模块经由所述全局数据线驱动所述模块区域内的所述存储模块。

10.如权利要求8所述的存储器,其特征在于,同一所述模块区域具有多条所述全局数据线,且多条所述全局数据线分为至少两组,每一组所述全局数据线与至少两个相邻的所述存储模块相对应。

11.如权利要求10所述的存储器,其特征在于,对于同一所述模块区域,所有所述全局数据线相邻排布,或者,不同组的所述全局数据线间隔排布。

12.如权利要求10所述的存储器,其特征在于,对于同一所述模块区域,所述读写控制驱动模块包括沿所述第一方向排布的多个读写控制驱动单元,且每一所述读写控制驱动单元电连接至少一组所述全局数据线。

13.如权利要求8所述的存储器,其特征在于,每一所述模块区域包含的所述存储模块的数量相同。

14.如权利要求1所述的存储器,其特征在于,所述第三方向与所述第二方向相同。

15.如权利要求1或14所述的存储器,其特征在于,所述第一方向与所述第二方向相垂直。

16.如权利要求1所述的存储器,其特征在于,还包括:行译码电路,所述行译码电路用于通过所述字线选中与所述字线电连接的所述存储单元;所述行译码电路位于所述读写控制驱动电路远离多个所述存储模块的一侧。

技术总结

本公开实施例提供一种存储器,包括:沿第一方向延伸的位线以及沿第二方向延伸的字线;沿第一方向排布的列选择电路以及多个存储模块;沿第一方向延伸的列选择线,列选择线电连接列选择电路,列选择电路经由列选择线驱动相应的所述放大单元;读写控制驱动电路,读写控制驱动电路与列选择电路分别位于多个存储模块的相邻侧;沿第二方向延伸的全局数据线以及沿第三方向延伸的电连接线,全局数据线经由电连接线电连接读写控制驱动电路,读写控制驱动电路用于驱动与全局数据线相对应的存储模块,以使数据经由全局数据线写入至存储单元内,或者,以从存储单元内读出数据并将数据传输至全局数据线。本公开实施例能够改善存储器的存储性能。

技术研发人员:李红文,尚为兵,张良

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!