MRAM芯片的制作方法

本发明涉及存储器,尤其涉及一种mram芯片。

背景技术:

1、磁性随机存储器(magnetic random access memory,mram)是一种极具潜力的新型存储器,该存储器具有电路设计简单,读写速度快,无限次擦写、掉电不丢失等优点。

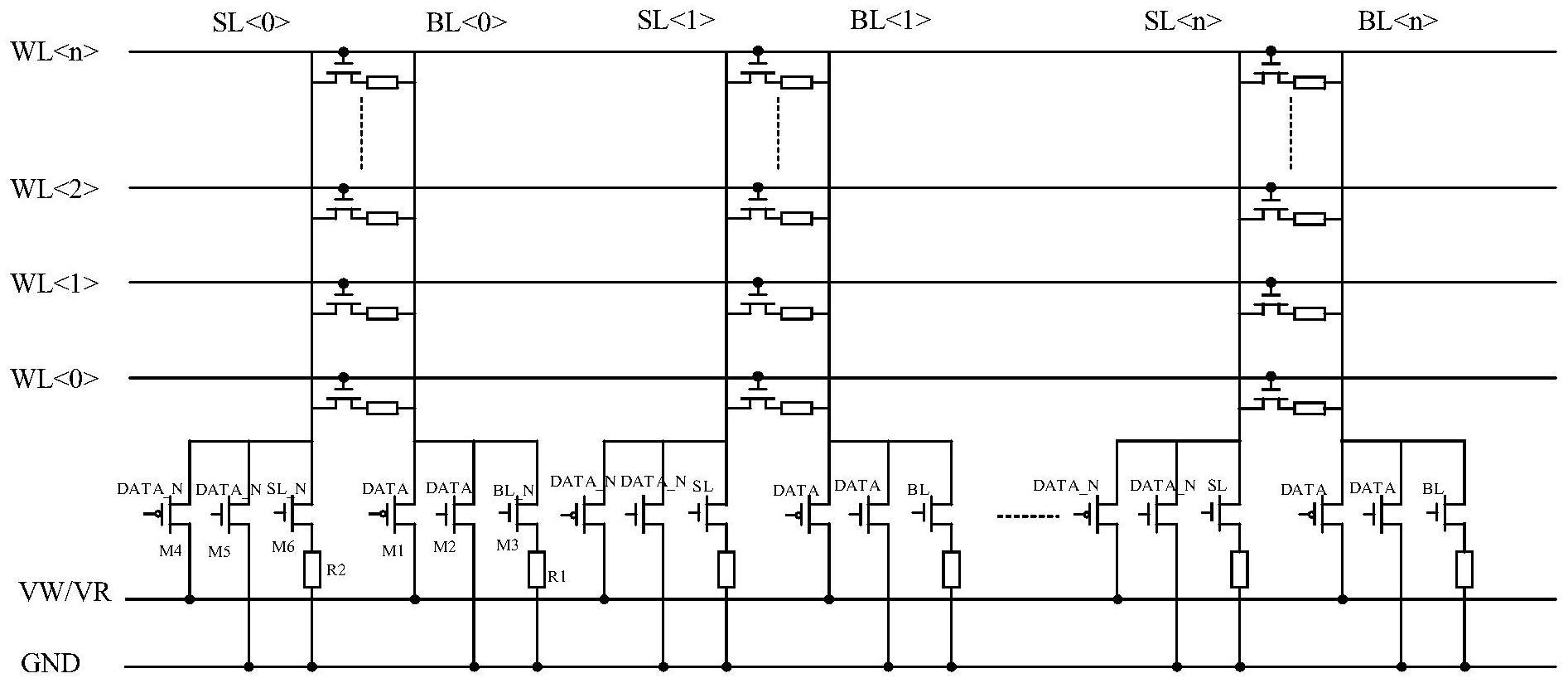

2、mram的核心存储单元包括1个磁性隧道结(mtj)、1个场效应管(cmos)。其中,mtj的相关制造工艺可能出现部分相邻位置的接触短路现象,称为底部短路(bottom short),则短路的两mtj所在的bl上的所有mtj(短路的两mtj除外)发生误读,同时短路的mtj则会存在误写问题,导致测试结果不准确,影响良率判断。例如,图1示出了mram的阵列结构,通过sl、bl、wl的关断来控制对mtj的读、写操作。图中①、②、③、④表示四个mtj,①、②号mtj之间发生bottom short,此时会出现误写或误读的问题。

3、为便于理解,图2a示出了对③号mtj写0时,改写的等效电路图。对③号mtj写0时,bl<1>接写电压vw,sl<1>接gnd,wl<2>选通,未选中的sl、bl接地,则①、②号mtj可能会被误写。图2b示出了对①号mtj写1时,改写的等效电路图。对①号mtj写1时,bl<1>接gnd,sl<1>接写电压vw,wl<1>选通,未选中的sl、bl接地,则②号mtj可能会被误写。图2c示出了对③号mtj读0或1时,误读的等效电路图。对③号mtj进行读操作时,bl<1>接读电压vr,sl<1>接gnd,wl<2>选通,未选中的sl、bl接地,则读到的电阻为③//①+②,①、②的状态影响③读出结果,存在读错的可能性。支路a为正常写入mtj的通路,支路b为由于bottom short多出来的通路引起的改写通路。

4、由此可以看出,如果两个mtj之间发生底部短路,会直接影响芯片的正常工作。但是,仅仅由于底部短路失效,就将整个mram芯片报废,又会造成很大浪费。

技术实现思路

1、为解决上述问题,本发明提供了一种mram芯片,能够容忍部分mtj之间发生底部短路失效,避免出现相关mtj被误写、误读的问题,使存储芯片可正常工作。

2、本发明提供一种mram芯片,包括一个或多个阵列,每个阵列进一步包括:

3、行列分布的存储单元,每个存储单元包括串联的磁性隧道结和mos晶体管;

4、多条字线;

5、成对的多条位线和多条源线;以及,

6、多个供电端控制电路,连接于每条位线以及每条源线的供电端,所述供电端控制电路具有三条不同的通路,对任一存储单元写0、写1或读操作时,用于改变各条位线和源线的供电方式。

7、可选地,连接于其中一条位线的所述供电端控制电路包括:

8、第一选通晶体管,连接于该条位线与电源线之间,所述电源线用于输入写电压或者读电压;

9、第二选通晶体管,连接于该条位线与地线之间;

10、串联的第三选通晶体管和第一阻性器件,连接于该条位线与地线之间;

11、连接于该条位线对应源线的所述供电端控制电路具有相同的电路结构,包括:

12、第四选通晶体管,连接于该条源线与电源线之间,所述电源线用于输入写电压或者读电压;

13、第五选通晶体管,连接于该条源线与地线之间;

14、串联的第六选通晶体管和第二阻性器件,连接于该条源线与地线之间。

15、可选地,所述第一选通晶体管和所述第四选通晶体管为pmos晶体管;

16、所述第二选通晶体管、所述第三选通晶体管、所述第五选通晶体管、所述第六选通晶体管为nmos晶体管。

17、可选地,所述第一阻性器件和所述第二阻性器件由多晶硅电阻或者磁性隧道结实现。

18、可选地,所述第一阻性器件和所述第二阻性器件的阻值为n*rap,n≥2,rap表示存储单元的磁性隧道结为反平行态时的电阻值。

19、可选地,还包括:列地址选择器和列地址译码器,用于在写操作和读操作时,根据列地址选中目标存储单元的位线和源线。

20、可选地,还包括:行地址选择器和行地址译码器,用于在写操作和读操作时,根据行地址选中目标存储单元的字线。

21、本发明提供的一种mram芯片,其在阵列结构每条位线和每条源线的供电端设置供电端控制电路,当对阵列的任意一个存储单元写0时,选中的位线接写电压,选中的源线接地,其余未选中的位线和源线通过阻性器件接地;当对阵列的任意一个存储单元写1时,选中的位线接地,选中的源线接写电压,其余未选中的位线和源线通过阻性器件接地;当对阵列的任意一个存储单元进行读操作时,选中的位线接读电压,选中的源线接地,其余未选中的位线和源线通过阻性器件接地。与现有技术相比,本发明阵列结构可以容忍部分mtj之间发生底部短路失效,避免出现相关mtj误写、误读的问题,使存储芯片可正常工作。

技术特征:

1.一种mram芯片,其特征在于,包括一个或多个阵列,每个阵列进一步包括:

2.根据权利要求1所述的mram芯片,其特征在于,

3.根据权利要求2所述的mram芯片,其特征在于,所述第一选通晶体管和所述第四选通晶体管为pmos晶体管;

4.根据权利要求2所述的mram芯片,其特征在于,所述第一阻性器件和所述第二阻性器件由多晶硅电阻或者磁性隧道结实现。

5.根据权利要求2所述的mram芯片,其特征在于,所述第一阻性器件和所述第二阻性器件的阻值为n*rap,n≥2,rap表示存储单元的磁性隧道结为反平行态时的电阻值。

6.根据权利要求1所述的mram芯片,其特征在于,还包括:列地址选择器和列地址译码器,用于在写操作和读操作时,根据列地址选中目标存储单元的位线和源线。

7.根据权利要求1所述的mram芯片,其特征在于,还包括:行地址选择器和行地址译码器,用于在写操作和读操作时,根据行地址选中目标存储单元的字线。

技术总结

本发明提供一种MRAM芯片,包括一个或多个阵列,该阵列包括行列分布的存储单元以及与存储单元相连接的多条字线、多条位线和多条源线,在阵列结构每条位线和每条源线的供电端设置供电端控制电路,供电端控制电路具有三条不同的通路,对任一存储单元写0、写1或读操作时,用于改变各条位线和源线的供电方式。

技术研发人员:侯嘉,方伟,熊保玉,王明

受保护的技术使用者:浙江驰拓科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!