存储器的电平转换电路及存储器的控制方法与流程

本发明涉及存储器,特别涉及一种存储器的电平转换电路及存储器的控制方法。

背景技术:

1、固态硬盘(ssd,solid state drive)是由控制器和存储芯片阵列组成的非挥发性数据存储装置。固态硬盘的存储介质包括闪存芯片或dram芯片。固态硬盘的接口可以兼容以磁盘作为存储介质的传统硬盘,与传统硬盘相比具有体积小、质量轻、功耗低、无机械噪声、读写速度快等优点,因此,已经广泛地用于替代传统硬盘,例如应用于笔记本电脑、工控、视频监控、网络监控、网络终端、导航设备等诸多领域。

2、固态硬盘和主机有着各自的逻辑电平,固态硬盘接口的逻辑电平例如为1.8v,主机的逻辑电平例如为1.8v、3.3v,部分控制管脚主机还可能处于浮置(floating)状态。普通的电平转换电路,可以满足不同逻辑电平之间的转换,但若是一端处于floating状态,则会出现问题,会导致对端一直处于高电平状态,无法下拉,如时钟请求信号clkreq#。

3、时钟请求信号clkreq#是pcie控制信号中很重要的一个信号。它用来控制主板上参考时钟(reference clock)开关的控制信号,是一个双向开漏(open-drain)信号,低电平有效。同时时钟请求信号clkreq#用来控制低功耗(low power)状态的进出(低功耗状态例如包括l1cpm、l1.1以及l1.2)。而固态硬盘在上电时无法确定主机状态,若主机逻辑电平为3.3v,则有可能因电压过高造成固态硬盘控制系统损坏。若主机处于浮置状态,又可能导致固态硬盘无法接收到有效状态的逻辑电平信号,从而无法正常上电工作,如当固态硬盘处于low power状态时,需要依靠主机拉低时钟请求信号clkreq#来唤醒固态硬盘,但若是主机为floating状态,则固态硬盘就无法收到有效状态的时钟请求信号clkreq#,导致一直在low power状态无法退出,导致工作异常。

4、因此,期待一种存储器的电平转换电路及存储器的控制方法,能够解决上述问题。

技术实现思路

1、鉴于上述问题,本发明的目的在于提供一种存储器的电平转换电路及存储器的控制方法,能够判断主机状态,以及实现电平转换的功能。

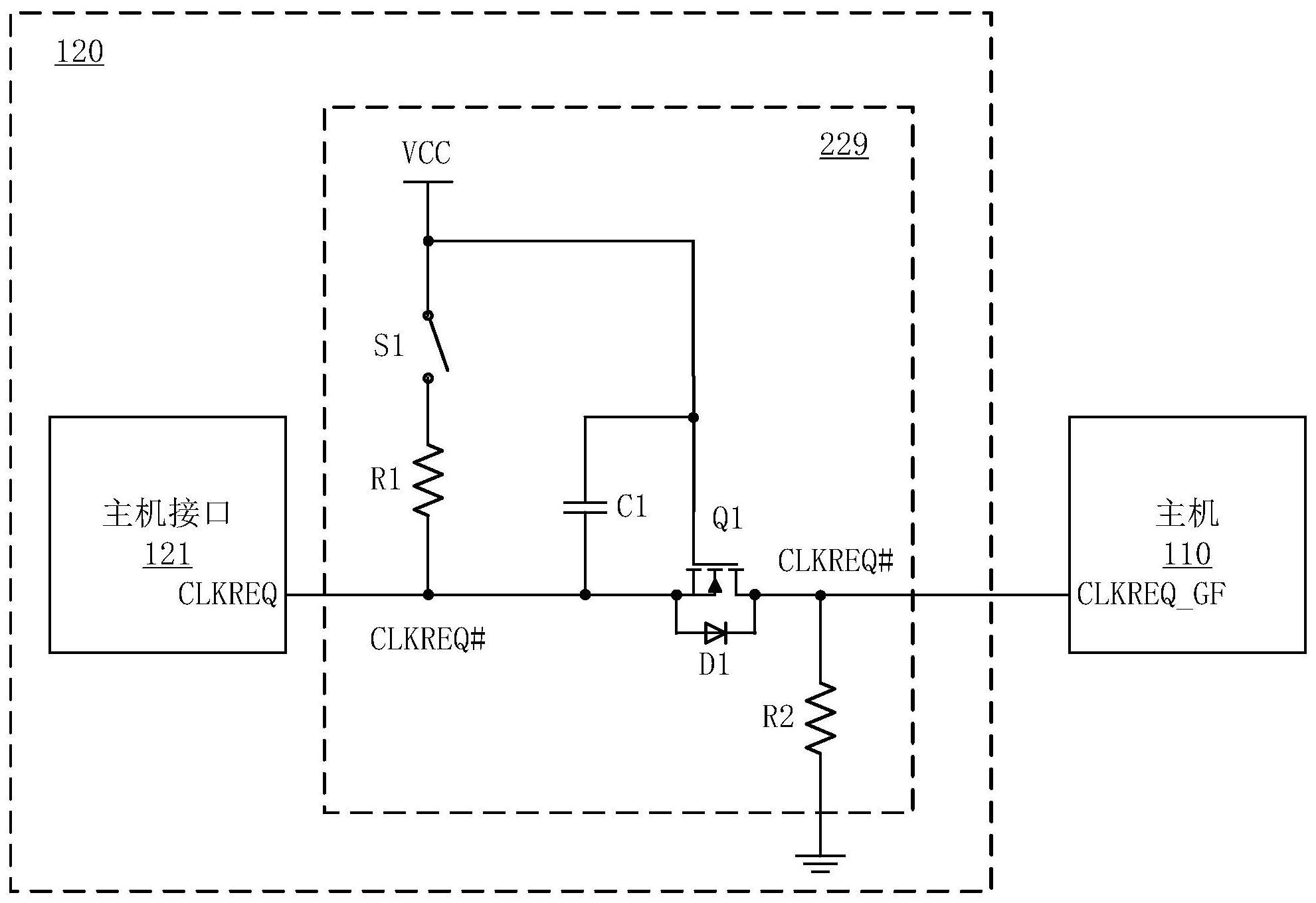

2、根据本发明的一方面,提供一种存储器的电平转换电路,所述存储器包括处理器以及耦接至主机以传输指令的主机接口,所述电平转换电路包括:第一晶体管,控制端耦接至工作电压,第一端耦接至所述主机,第二端耦接至所述主机接口,所述第一晶体管还包括体二极管,所述体二极管的正极耦接至所述第一晶体管的第二端,负极耦接至所述第一晶体管的第一端依次串联耦接在工作电压和所述第一晶体管的第二端之间的开关和第一电阻;以及,耦接于所述第一晶体管的第一端和地之间的第二电阻;其中,所述开关被配置为在所述存储器上电后的第一阶段间歇导通和关断,以向所述处理器提供所述主机接口处的不同状态的逻辑信号,所述处理器根据所述不同状态的逻辑信号判断所述主机的状态。

3、可选地,当所述开关受控导通时,所述主机接口向所述处理器提供第一状态的逻辑信号,当所述开关受控关断时,所述主机接口向所述处理器提供第二状态的逻辑信号,若所述第一状态和所述第二状态相同,则判定所述主机为非浮置状态;若所述第一状态和所述第二状态不相同,则判定所述主机为浮置状态。

4、可选地,在所述存储器上电后的第二阶段根据所述主机的状态控制所述开关导通或关断。

5、可选地:若所述主机为非浮置状态,控制所述开关导通;若所述主机为浮置状态,控制所述开关关断。

6、可选地,所述电平转换电路,还包括:电容,所述电容的第一端耦接至所述第一晶体管的控制端,第二端耦接至所述第一晶体管的第二端。

7、可选地,所述开关选自第二晶体管,所述第二晶体管的第一端耦接至所述工作电压,所述第二晶体管的第二端耦接至所述第一电阻的第一端,控制端受控于所述处理器。

8、可选地,所述第二电阻的阻值大于所述第一电阻的阻值。

9、可选地,所述工作电压的值为1.8v。

10、可选地,所述第一晶体管选自n型场效应管。

11、根据本发明的另一方面,提供一种存储器的控制方法,所述存储器包括耦接至主机以传输指令的主机接口以及上任一项所述的电平转换电路,所述控制方法包括:导通开关,读取所述主机接口的第一状态的逻辑信号;经过预定时间后关断所述开关,读取所述主机接口的第二状态的逻辑信号;根据所述第一状态的逻辑信号和所述第二状态的逻辑信号判断所述主机的状态。

12、可选地,所述根据所述第一状态的逻辑信号和所述第二状态的逻辑信号判断所述主机的状态包括:若所述第一状态与所述第二状态相同,则判断所述主机为非浮置状态;若所述第一状态与所述第二状态不同,则判断所述主机为浮置状态。

13、可选地,所述控制方法,还包括:若所述主机为非浮置状态,控制所述开关导通;若所述主机为浮置状态,控制所述开关关断,以将所述主机接口的时钟请求信号下拉至低电平状态。

14、可选地,通过改变所述第二电阻的阻值和/或所述第一晶体管的控制端和第二端之间电容的容值以改变所述预定时间。

15、可选地,所述逻辑信号选自时钟请求信号。

16、可选地,在所述根据所述第一状态的逻辑信号和所述第二状态的逻辑信号判断所述主机的状态的步骤之后,还包括:所述主机接口输出低电平状态的时钟请求信号;所述存储器进入链路电源状态。

17、本发明提供的存储器的电平转换电路及存储器的控制方法,在存储器上电时配合存储器处理器或固件,间隔预定时间前后各读取一次时钟请求信号,根据两次时钟请求信号的状态是否一致可以准确判断主机逻辑电平的状态,同时实现电平转换功能,并在主机处于浮置状态时,关断开关,令存储器退出低功耗状态,有效避免存储器无法退出或者错误进入低功耗状态,提高存储器的可靠性。

18、可选地,在电平转换电路晶体管的控制端和第二端之间耦接电容,能够加快晶体管的体二极管和电阻r2作为放电回路时的放电速度,减小预定时间,从而提高存储器的上电速度。

19、可选地,本发明实施例的电平转换电路在存储器和主机进行通信时,能够根据两端的逻辑电平进行适配,实现较宽范围的电平转换,并且电平转换功能的实现电路结构简单、易于实现,还能有效降低生产成本。

技术特征:

1.一种存储器的电平转换电路,所述存储器包括处理器以及耦接至主机以传输指令的主机接口,所述电平转换电路包括:

2.根据权利要求1所述的电平转换电路,其中,还包括:当所述开关受控导通时,所述主机接口向所述处理器提供第一状态的逻辑信号,当所述开关受控关断时,所述主机接口向所述处理器提供第二状态的逻辑信号,

3.根据权利要求2所述的电平转换电路,其中,还包括:在所述存储器上电后的第二阶段根据所述主机的状态控制所述开关导通或关断。

4.根据权利要求3所述的电平转换电路,其中,还包括:若所述主机为非浮置状态,控制所述开关导通;若所述主机为浮置状态,控制所述开关关断。

5.根据权利要求1所述的电平转换电路,还包括:

6.根据权利要求2所述的电平转换电路,其中,

7.根据权利要求1所述的电平转换电路,其中,

8.根据权利要求1所述的电平转换电路,其中,所述工作电压的值为1.8v。

9.根据权利要求1所述的电平转换电路,其中,所述第一晶体管选自n型场效应管。

10.一种存储器的控制方法,所述存储器包括耦接至主机以传输指令的主机接口以及如权利要求1-9任一项所述的电平转换电路,所述控制方法包括:

11.根据权利要求10所述的控制方法,其中,所述根据所述第一状态的逻辑信号和所述第二状态的逻辑信号判断所述主机的状态包括:

12.根据权利要求11所述的控制方法,还包括:

13.根据权利要求10所述的控制方法,通过改变所述第二电阻的阻值和/或所述第一晶体管的控制端和第二端之间电容的容值以改变所述预定时间。

14.根据权利要求10所述的控制方法,其中,所述逻辑信号选自时钟请求信号。

15.根据权利要求14所述的控制方法,在所述根据所述第一状态的逻辑信号和所述第二状态的逻辑信号判断所述主机的状态的步骤之后,还包括:

技术总结

本发明公开了一种存储器的电平转换电路及存储器的控制方法,存储器包括处理器以及耦接至主机以传输指令的主机接口,电平转换电路包括:第一晶体管,控制端耦接至工作电压,第一端耦接至所述主机,第二端耦接至所述主机接口,第一晶体管还包括体二极管,体二极管的正极耦接至第一晶体管的第二端,负极耦接至第一晶体管的第一端;依次串联耦接在工作电压和第一晶体管的第二端之间的开关和第一电阻;以及,耦接于第一晶体管的第一端和地之间的第二电阻;其中,开关被配置为在存储器上电后的第一阶段间歇导通和关断,以向处理器提供主机接口处的不同状态的逻辑信号,处理器根据不同状态的逻辑信号判断所述主机的状态。

技术研发人员:叶彦斌,张军芳,娄海鑫

受保护的技术使用者:联芸科技(杭州)股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!