存储芯片的测试方法、装置、设备及存储介质与流程

本公开涉及半导体,本公开涉及但不限于一种存储芯片的测试方法、装置、设备及存储介质。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)是一种广泛应用多计算机系统的半导体存储器。dram包括晶体管、字元线(row address)、位元线(columnaddress)、电容、金属互连和外缘区域等。

2、dram需要经过一系列测试对其可靠性进行评估,可靠性满足条件后才能出厂应用,例如,对dram中的存储单元进行测试,确定dram的存储和读写数据功能是否正常,在测试过程中存在存储芯片受损的风险且影响测试稳定性。

技术实现思路

1、本公开实施例提供一种存储芯片的测试方法、装置、设备及存储介质。

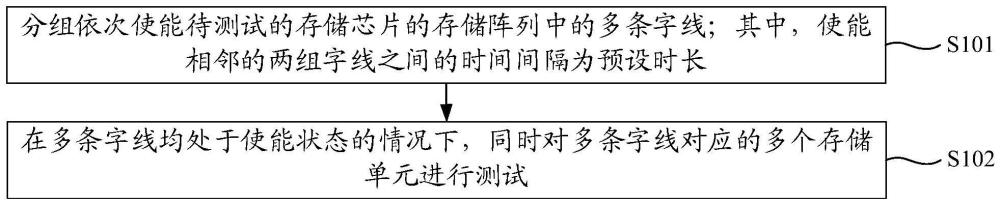

2、一方面,本公开实施例提供一种存储芯片的测试方法,所述方法包括:分组依次使能待测试的存储芯片的存储阵列中的多条字线;其中,使能相邻的两组字线之间的时间间隔为预设时长;在所述多条字线均处于使能状态的情况下,同时对所述多条字线对应的多个存储单元进行测试。

3、在一些实施例中,所述方法还包括:开启所述待测试的存储芯片的延迟测试模式,得到所述存储阵列中的字线分组信息和所述预设时长;开启所述待测试的存储芯片的多字线测试模式;所述分组依次使能待测试的存储芯片的存储阵列中的多条字线,包括:在所述延迟测试模式和所述多字线测试模式均开启的情况下,基于所述字线分组信息和所述预设时长,依次使能所述存储芯片中每一组字线。

4、在一些实施例中,所述存储阵列包括至少一个存储块,每一所述存储块中包括多个存储单元和多条字线;所述分组依次使能待测试的存储芯片的存储阵列中的多条字线,包括:分组依次使能每一所述存储块中的多条字线;其中,所述每一所述存储块中相同位置的字线同时被使能;在所述多条字线均处于使能状态的情况下,同时对所述多条字线对应的多个存储单元进行测试,包括:在每一所述存储块中的多条字线均处于使能状态的情况下,同时对每一所述存储块中所述多条字线对应的多个存储单元进行测试。

5、在一些实施例中,每一所述存储块包括分为r组的m条字线,所述r为大于1且小于m的整数;所述分组依次使能每一所述存储块中的多条字线,包括:使能每一所述存储块的第i组字线;在使能每一所述存储块的第i组字线之后间隔所述预设时长使能每一所述存储块的第i+1组字线;其中,所述i为大于0且小于r的整数。

6、在一些实施例中,在每一所述存储块中,第j组字线包括第j+nr条字线,其中,所述j为大于0且小于r+1的整数,所述n为大于0的整数,且所述j+nr不超过m。

7、在一些实施例中,所述预设时长小于等于tck/(4r),所述tck为一个时钟周期内使能信号持续的时间。

8、在一些实施例中,在所述多条字线均处于使能状态的情况下,同时对所述多条字线对应的多个存储单元进行测试,包括:在所述多条字线均处于使能状态的情况下,同时向所述多条字线对应的多个存储单元中写入测试数据;同时从所述多个存储单元中读出目标数据;基于所述测试数据,对所述目标数据进行校验,得到所述存储阵列的测试结果。

9、在一些实施例中,对每一所述目标数据进行校验,得到所述存储阵列的测试结果,包括:对所述测试数据进行压缩处理,得到第一压缩数据;对所述目标数据进行所述压缩处理,得到第二压缩数据;基于所述第一压缩数据和所述第二压缩数据的一致性,确定所述存储阵列的测试结果。

10、另一方面,本公开实施例提供一种存储芯片的测试装置,所述装置包括:使能组件,用于分组依次使能待测试的存储芯片的存储阵列中的多条字线;其中,使能相邻的两组字线之间的时间间隔为预设时长;测试组件,用于在所述多条字线均处于使能状态的情况下,同时对所述多条字线对应的多个存储单元进行测试。

11、在一些实施例中,所述装置还包括:模式开启组件,用于:开启所述待测试的存储芯片的延迟测试模式,得到所述存储阵列中的字线分组信息和所述预设时长;开启所述待测试的存储芯片的多字线测试模式;所述使能组件包括:第一使能单元,用于在所述延迟测试模式和所述多字线测试模式均开启的情况下,基于所述字线分组信息和所述预设时长,依次使能所述存储芯片中每一组字线。

12、在一些实施例中,所述存储阵列包括至少一个存储块,每一所述存储块中包括多个存储单元和多条字线;所述使能组件包括:第二使能单元,用于分组依次使能每一所述存储块中的多条字线;其中,所述每一所述存储块中相同位置的字线同时被使能;所述测试组件包括:测试单元,用于在每一所述存储块中的多条字线均处于使能状态的情况下,同时对每一所述存储块中所述多条字线对应的多个存储单元进行测试。

13、在一些实施例中,每一所述存储块包括分为r组的m条字线,所述r为大于1且小于m的整数;所述第二使能单元还用于:使能每一所述存储块的第i组字线;在使能每一所述存储块的第i组字线之后间隔所述预设时长使能每一所述存储块的第i+1组字线;其中,所述i为大于0且小于r的整数。

14、在一些实施例中,所述测试组件包括写入单元、读出单元和校验单元,其中,所述写入单元用于:在所述多条字线均处于使能状态的情况下,同时向所述多条字线对应的多个存储单元中写入测试数据;所述读出单元用于:同时从所述多个存储单元中读出目标数据;所述校验单元用于:基于所述测试数据,对所述目标数据进行校验,得到所述存储阵列的测试结果。

15、在一些实施例中,所述校验单元包括第一压缩子单元、第二压缩子单元和确定子单元;其中,所述第一压缩子单元,用于对所述测试数据进行压缩处理,得到第一压缩数据;所述第二压缩子单元,用于对所述目标数据进行所述压缩处理,得到第二压缩数据;所述确定子单元,用于基于所述第一压缩数据和所述第二压缩数据的一致性,确定所述存储阵列的测试结果。

16、再一方面,本公开实施例提供一种存储芯片的测试设备,所述设备包括:处理器,用于执行上述任一实施例中所述的方法;用于存储所述处理器可执行指令的存储器。

17、又一方面,本公开实施例提供一种计算机可读存储介质,当所述存储介质中的指令由处理器执行时,使得处理器能够执行上述任一实施例中所述的方法。

18、本公开实施例中,一方面,分组依次使能待测试的存储芯片的存储阵列中的多条字线;其中,使能相邻的两组字线之间的时间间隔为预设时长,这样可以按照一定的时延延迟字线开关的顺序,可以减少同一时间存储芯片内部电路工作的数量,从而可以减小峰值电流,进而可以减少存储芯片受损的情况并且提高测试稳定性;另一方面,在多条字线均处于使能状态的情况下,同时对多条字线对应的多个存储单元进行测试,无需先对一条字线对应的存储单元进行测试,再对另一条字线对应的存储单元进行测试,这样,可以节省大量的时间,从而节省测试成本。

技术特征:

1.一种存储芯片的测试方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述方法还包括:

3.根据权利要求1所述的方法,其特征在于,所述存储阵列包括至少一个存储块,每一所述存储块中包括多个存储单元和多条字线;

4.根据权利要求3所述的方法,其特征在于,每一所述存储块包括分为r组的m条字线,所述r为大于1且小于m的整数;

5.根据权利要求4所述的方法,其特征在于,在每一所述存储块中,第j组字线包括第j+nr条字线,其中,所述j为大于0且小于r+1的整数,所述n为大于0的整数,且所述j+nr不超过m。

6.根据权利要求4或5所述的方法,其特征在于,所述预设时长小于等于tck/(4r),所述tck为一个时钟周期内使能信号持续的时间。

7.根据权利要求1至5任一项所述的方法,其特征在于,在所述多条字线均处于使能状态的情况下,同时对所述多条字线对应的多个存储单元进行测试,包括:

8.根据权利要求7所述的方法,其特征在于,对每一所述目标数据进行校验,得到所述存储阵列的测试结果,包括:

9.一种存储芯片的测试装置,其特征在于,所述装置包括:

10.根据权利要求9所述的装置,其特征在于,所述装置还包括:模式开启组件,用于:开启所述待测试的存储芯片的延迟测试模式,得到所述存储阵列中的字线分组信息和所述预设时长;开启所述待测试的存储芯片的多字线测试模式;

11.根据权利要求9所述的装置,其特征在于,所述存储阵列包括至少一个存储块,每一所述存储块中包括多个存储单元和多条字线;

12.根据权利要求11所述的装置,其特征在于,每一所述存储块包括分为r组的m条字线,所述r为大于1且小于m的整数;所述第二使能单元还用于:使能每一所述存储块的第i组字线;在使能每一所述存储块的第i组字线之后间隔所述预设时长使能每一所述存储块的第i+1组字线;其中,所述i为大于0且小于r的整数。

13.根据权利要求9所述的装置,其特征在于,所述测试组件包括写入单元、读出单元和校验单元,其中,所述写入单元用于:在所述多条字线均处于使能状态的情况下,同时向所述多条字线对应的多个存储单元中写入测试数据;所述读出单元用于:同时从所述多个存储单元中读出目标数据;所述校验单元用于:基于所述测试数据,对所述目标数据进行校验,得到所述存储阵列的测试结果。

14.根据权利要求13所述的装置,其特征在于,所述校验单元包括第一压缩子单元、第二压缩子单元和确定子单元;其中,所述第一压缩子单元,用于对所述测试数据进行压缩处理,得到第一压缩数据;所述第二压缩子单元,用于对所述目标数据进行所述压缩处理,得到第二压缩数据;所述确定子单元,用于基于所述第一压缩数据和所述第二压缩数据的一致性,确定所述存储阵列的测试结果。

15.一种存储芯片的测试设备,其特征在于,所述设备包括:

16.一种计算机可读存储介质,其特征在于,当所述存储介质中的指令由处理器执行时,使得处理器能够执行如权利要求1至8任一项所述的方法。

技术总结

本公开实施例提供一种存储芯片的测试方法、装置、设备及存储介质。其中,所述方法包括:分组依次使能待测试的存储芯片的存储阵列中的多条字线;其中,使能相邻的两组字线之间的时间间隔为预设时长;在所述多条字线均处于使能状态的情况下,同时对所述多条字线对应的多个存储单元进行测试。

技术研发人员:许兰平,黄建钦

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!