半导体装置及存储电路测试方法与流程

背景技术:

1、本公开涉及一种半导体装置和sram电路测试方法,例如,涉及一种用于预测静态随机存取存储器(sram)的寿命的技术。

2、例如,日本专利申请公开no.2017-173242(专利文献1)已经被公知为用于在半导体装置发生故障之前通知用户半导体装置可能发生故障的技术。

3、具体地,本文献中公开的半导体装置包括功能单元和寿命预测电路。多个功能单元中的一个功能单元为中央处理电路。寿命预测电路通过降低半导体装置的电源电压并执行关于功能单元的测试来获取该功能单元的劣化程度。当劣化程度超过预定阈值时,寿命预测电路通知用户正接近半导体装置的寿命。

技术实现思路

1、就日本专利申请公开no.2017-173242(专利文献1)中公开的技术而言,在执行劣化预测测试时需要降低整个半导体装置的电源电压。因此,仅当半导体装置通电时才能执行劣化预测测试,并且当用户使用半导体装置时不能测试该半导体装置的劣化程度。

2、从本说明书和附图的描述中,其他问题和新颖特征将是显而易见的。

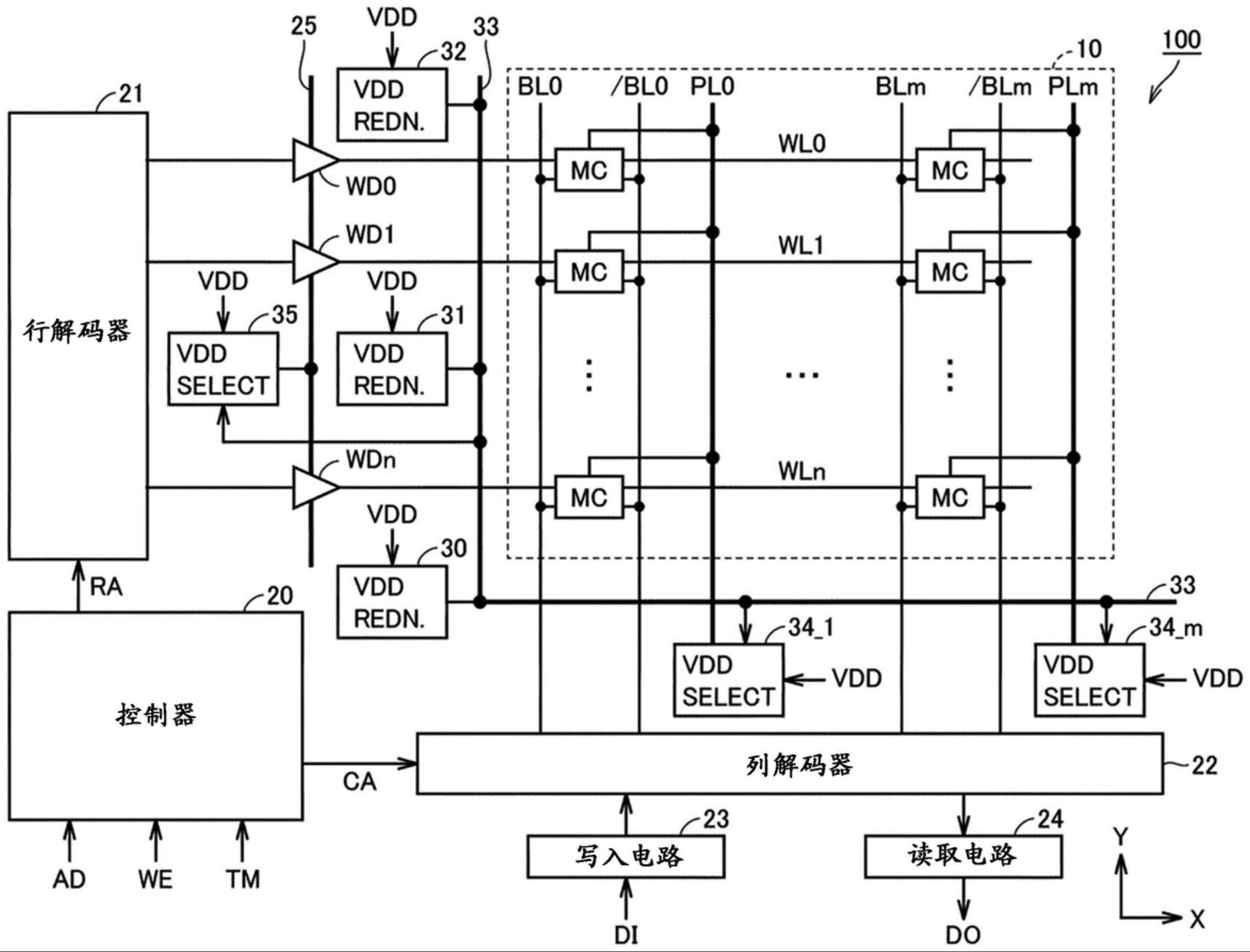

3、根据一个实施例,一种被安装在半导体装置中的sram电路包括电源电压降低电路、第一电源电压选择电路、第二电源电压选择电路。电源电压降低电路生成通过降低外部电源电压而获得的降低电压。第一电源电压选择电路选择外部电源电压和降低电压中的一个电压作为被供应给字线驱动器的驱动电压。第二电源电压选择电路选择外部电源电压和降低电压中的一个电压作为电源线的电压,该电源线向存储单元供应操作电压。

4、根据上述实施例,可以在用户使用被安装在半导体装置中的sram电路时执行其劣化程度测试。

技术特征:

1.一种半导体装置,包括基于外部电源电压操作的静态随机存取存储器sram电路,

2.根据权利要求1所述的半导体装置,

3.根据权利要求2所述的半导体装置,

4.根据权利要求2所述的半导体装置,

5.根据权利要求4所述的半导体装置,还包括内置自测试bist电路,

6.根据权利要求5所述的半导体装置,还包括从所述bist电路接收所述确定结果的主控制器,

7.根据权利要求6所述的半导体装置,

8.根据权利要求7所述的半导体装置,

9.根据权利要求1所述的半导体装置,

10.根据权利要求4所述的半导体装置,

11.一种sram电路的测试方法,所述测试方法包括:

12.根据权利要求11所述的sram电路的测试方法,还包括:

技术总结

本公开涉及半导体装置及存储电路测试方法。在安装在半导体装置中的SRAM电路中,电源电压降低电路生成通过降低外部电源电压而获得的降低电压。第一电源电压选择电路选择所述外部电源电压和所述降低电压中的一个电压作为供应给字线驱动器的驱动电压。第二电源电压选择电路选择所述外部电源电压和所述降低电压中的一个电压作为向存储单元供应操作电压的电源线的电压。

技术研发人员:长田俊哉,松嶋润

受保护的技术使用者:瑞萨电子株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!