用于经由协同方法保护存储器设备的方法和装置与流程

各种实施方案整体涉及减轻存储器设备中的串扰,并且更具体地涉及一种用于减小具有动态随机存取存储器的系统中的串扰效应的方法和装置。

背景技术:

1、在所有计算系统(从台式计算机和移动设备到服务器和云平台)中,主存储器都是关键部件。动态随机存取存储器(dram)的低成本和相对低的时延使其成为用于构建主存储器的主要数据存储技术。dram技术过程缩放已使得能够减小dram单元大小,以增加存储器容量和性能。随着dram单元的大小缩小,dram中的电容器和存取晶体管变得不太可靠并且通常更容易受到电气噪声和干扰(更通常称为串扰)的影响。

2、由dram技术过程缩放引起的串扰可靠性问题会导致安全漏洞。例如,重复地读取或访问dram中的同一行可破坏物理上相邻的行中的数据。更具体地,当在单个dram刷新间隔内重复地访问dram行(这一过程也称为行锤击)时,物理上相邻的行中的一个或多个位可被翻转为错误值。行锤击攻击可能导致对存储在主存储器中的数据的损害和控制。

3、存在各种解决方案来减轻串扰。这些解决方案中的许多解决方案是昂贵的,因为它们牺牲了芯片面积来增强性能和可靠性。期望一种不会为了性能而牺牲容量的改进解决方案。

技术实现思路

1、装置和相关联的方法涉及概率性和确定性ram访问监测器(padram),该padram通过减少对dram存储器的访问次数来减轻串扰。padram通过以下方式来跟踪dram的被频繁访问的行(称为热行):使用dram的现有故障隔离特征的一部分作为计数器并且通过使用随机数生成器使该计数器以概率性方式递增。计数器值基于热度阈值(hotness threshold)或热阈值参数(hot threshold parameter)来确定dram行是否被访问。热度阈值被设定为保证对某一词语的总dram访问次数不超过行锤击阈值。该行锤击阈值可被定义为在错误发生之前能够对dram进行的最小字线访问次数。在本公开中,dram与双倍数据速率(ddr)存储器同义,其也可称为ddr同步dram或ddr sdram。

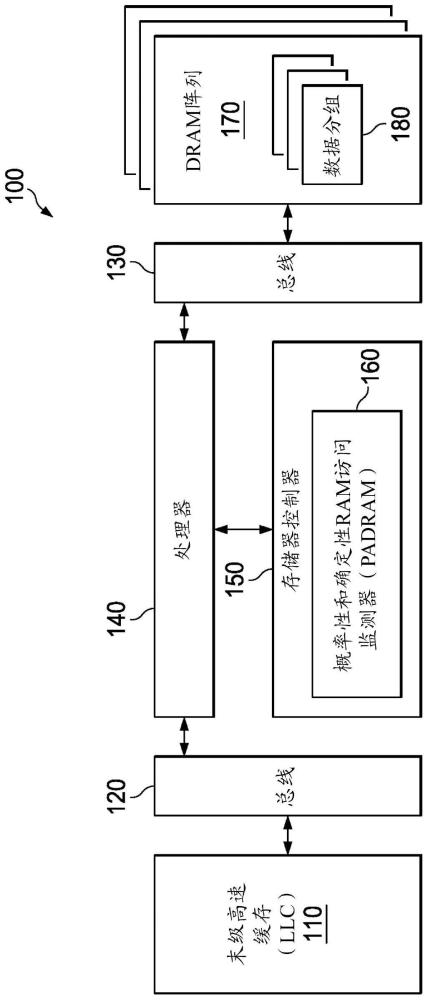

2、在一个实施方案中,一种计算机系统包括至少一个处理器和可操作地耦合到该处理器的dram。该计算机系统还包括可操作地耦合到处理器的存储器控制器。该存储器控制器包括被配置为减轻dram阵列中的串扰的装置。该计算机系统还包括多个数据分组。每个数据分组表示存储器线并且被配置为包括计数器,该计数器跟踪对dram阵列中的每个行的访问。

3、在另一实施方案中,一种处于存储器控制器中的装置包括计数器,该计数器被嵌入在数据分组结构中,对于主存储器的访问次数进行计数。随机数生成器基于概率参数使计数器以概率性方式递增。该装置包括静态随机存取(sram)寄存器,该sram寄存器被配置用于对行地址匹配进行访问响应。逻辑控制器控制是否对sram寄存器或主存储器进行访问。

4、在又一实施方案中,一种在存储器控制器处实施的方法包括:接收行地址;以及基于该行地址来确定是访问片上存储器还是dram阵列;在片上存储器中是否存在行地址匹配。如果在片上存储器中存在行地址匹配,则将对应于该行地址的数据分组的高速缓存线写入到该片上存储器,并以及绕过对dram阵列的所有访问。如果发生行地址未命中,则基于第一条件和第二条件利用数据分组的高速缓存线来访问dram阵列。

5、各种实施方案可实现一个或多个优点。在一个示例性方面中,存储器的性能开销可通过以下方式来降低:使用随机数生成器来使计数器以概率性方式递增,而不是随着对dram的每次读取或写入访问而以确定性方式递增。使计数器以概率性方式递增降低了性能开销的成本,因为不必使计数器随着每次读取和写入访问而递增。另外,攻击者不太能够预测或计算dram访问的频率。

6、在另一示例性方面中,ddr故障隔离特征的经回收位被用作计数器以跟踪对每个dram行的读取和写入访问。从数据分组的纠错部分(ecc)回收的4字节或32位可由随机数生成器基于某些条件提取并递增。将经回收位用作计数器会节省芯片容量,因为芯片面积不会被在芯片上实施以跟踪对每个行存储器的访问的硬件计数器所消耗。

7、在又一示例性方面中,一种逻辑控制器可检查是否设定了指示片上存储器中存在数据的标志。如果设定了该标志,则存储器控制器可执行对sram寄存器的读取和写入访问。例如,如果设定了该标志,则存储器控制器首先检查所请求的行地址在sram中是否可用。如果可用,则可将高速缓存线数据从sram读取到请求部件,或可将高速缓存线数据写入到sram。对sram的访问会减少对dram的访问次数,并且由此减轻串扰。

8、附图和以下描述中阐述了各种实施方案的细节。在结合附图和权利要求来看以下具体实施方式时,其他特征和优点将变得显而易见。

技术特征:

1.一种计算机系统,所述计算机系统包括:

2.根据权利要求1所述的计算机系统,其中所述多个数据分组中的每个数据分组包括元数据部分,所述元数据部分包括纠错码部分和由从所述纠错码部分回收的字节形成的计数器部分。

3.根据权利要求2所述的计算机系统,其中所述计数器部分是跟踪对所述dram阵列进行访问的次数的计数器。

4.根据权利要求3所述的计算机系统,其中所述存储器控制器还包括存储器参数寄存器,所述存储器参数寄存器存储由所述装置使用的设备参数。

5.根据权利要求4所述的计算机系统,其中当随机数生成器值小于存储于所述存储器参数寄存器中的概率设备参数时,所述计数器递增。

6.根据权利要求5所述的计算机系统,其中被配置为减轻串扰的所述装置包括:

7.根据权利要求6所述的计算机系统,其中所述逻辑控制器包括指示所述sram寄存器是否为空的标志。

8.根据权利要求7所述的计算机系统,所述计算机系统还包括:

9.根据权利要求8所述的计算机系统,其中响应于行地址匹配以及来自所述存储器控制器的读取请求,所述sram寄存器向所述末级高速缓存发送数据分组并且绕过对所述dram阵列的任何访问。

10.根据权利要求8所述的计算机系统,其中响应于行地址匹配以及来自所述存储器控制器的写入请求,所述sram寄存器将数据分组写入到所述sram寄存器的存储器位置中并且绕过对所述dram阵列的任何访问。

11.一种处于存储器控制器中的装置,所述装置包括:

12.根据权利要求11所述的装置,所述装置还包括参数寄存器,所述参数寄存器存储所述概率参数,所述概率参数确定主存储器中的行的刷新间隔。

13.根据权利要求12所述的装置,其中所述参数寄存器还包括热度阈值。

14.根据权利要求11所述的装置,其中所述计数器包括从所述主存储器的纠错码特征的一部分回收的多个字节位。

15.一种在存储器控制器处实施的方法,所述方法包括:

16.根据权利要求15所述的方法,其中所述确定包括:响应于所述片上存储器中的行地址匹配,利用对应于所述行地址的数据分组的高速缓存线来访问所述片上存储器,以及绕过对dram阵列的所有访问。

17.根据权利要求16所述的方法,其中所述确定还包括:

18.根据权利要求17所述的方法,其中所述第一条件包括响应于所述随机数生成器的所述输出小于所述预定概率参数,并且所述数据分组的计数器值大于热阈值参数,访问所述dram阵列以及所述片上存储器和末级高速缓存中的至少一者或多者。

19.根据权利要求17所述的方法,其中所述预定概率参数是通过比率n除以r来确定的,其中n是能够对具有r行的所述dram阵列进行的激活或访问次数,并且所述预定概率参数大于n除以r的倒数,其中n和r为正整数。

20.根据权利要求18所述的方法,其中所述热阈值参数基于行锤击阈值以及所述dram阵列的字线中的高速缓存线的数目,并且被选择为小于所述行锤击阈值除以所述dram阵列中的每个字线的所述高速缓存线数目。

技术总结

一种用于减轻动态随机存取存储器(DRAM)中的串扰的协同方法,该协同方法实现了使用随机数生成器来使计数器以概率性方式递增。该计数器是通过回收双倍数据速率(DDR)故障隔离特征的字节来形成的。可将随机数生成器值与预定参数值进行比较,并且可基于该比较的结果来确定是否提取计数器并使该计数器递增。逻辑控制器将计数器值与预定热度阈值参数进行比较,并且基于本地存储器中存在地址匹配来设定标志。基于比较的结果,减少对DRAM的访问。

技术研发人员:塞耶德穆罕默德·塞耶扎德德尔切,瓦姆西·雷迪·科马雷迪

受保护的技术使用者:超威半导体公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!