一种单比特存内计算装置的制作方法

本发明涉及存内计算领域,特别是涉及一种单比特存内计算装置。

背景技术:

1、深度卷积神经网络(dcnns)继续证明了推理精度的提高,深度学习正在向边缘计算转移。这一发展推动了低资源机器学习算法及其加速硬件的工作。dcnns中最常见的运算是乘法和累加(mac),它控制着功率和延迟。mac操作具有很高的规则性和并行性,因此非常适合硬件加速。然而,内存访问量严重限制了传统数字加速器的能源效率。因此,存内计算(cim)对dcnn加速越来越有吸引力。

2、目前存内计算的设计中,按存储介质来划分可分为基于sram的设计和基于新型非易失性存储器的设计。基于sram的设计技术成熟,但也存在一定问题。在外部输入进来驱动字线时,如果字线上挂载存储单元的列数过多,则会引起信号在长距离传输过程中脉冲宽度的衰减。在存内计算阵列里,计算的过程中需要字线信号有固定宽度的脉冲,若发生脉冲宽度的衰减则会导致不同列计算结果的不一致。

3、为了完成大吞吐量的计算,现有存内计算阵列的大小基本在256行乘以64列,在列计算的读取中,需要完成每列256个输入与256个权重的乘加,最后的结果难以量化的很细致,需要降低一定的输出结果精度。

4、因此,亟需提供一种能够提高单比特存内计算读出精度的单比特存内计算装置。

技术实现思路

1、本发明的目的是提供一种新的单比特存内计算装置,能够提高单比特存内计算读出精度。

2、为实现上述目的,本发明提供了如下方案:

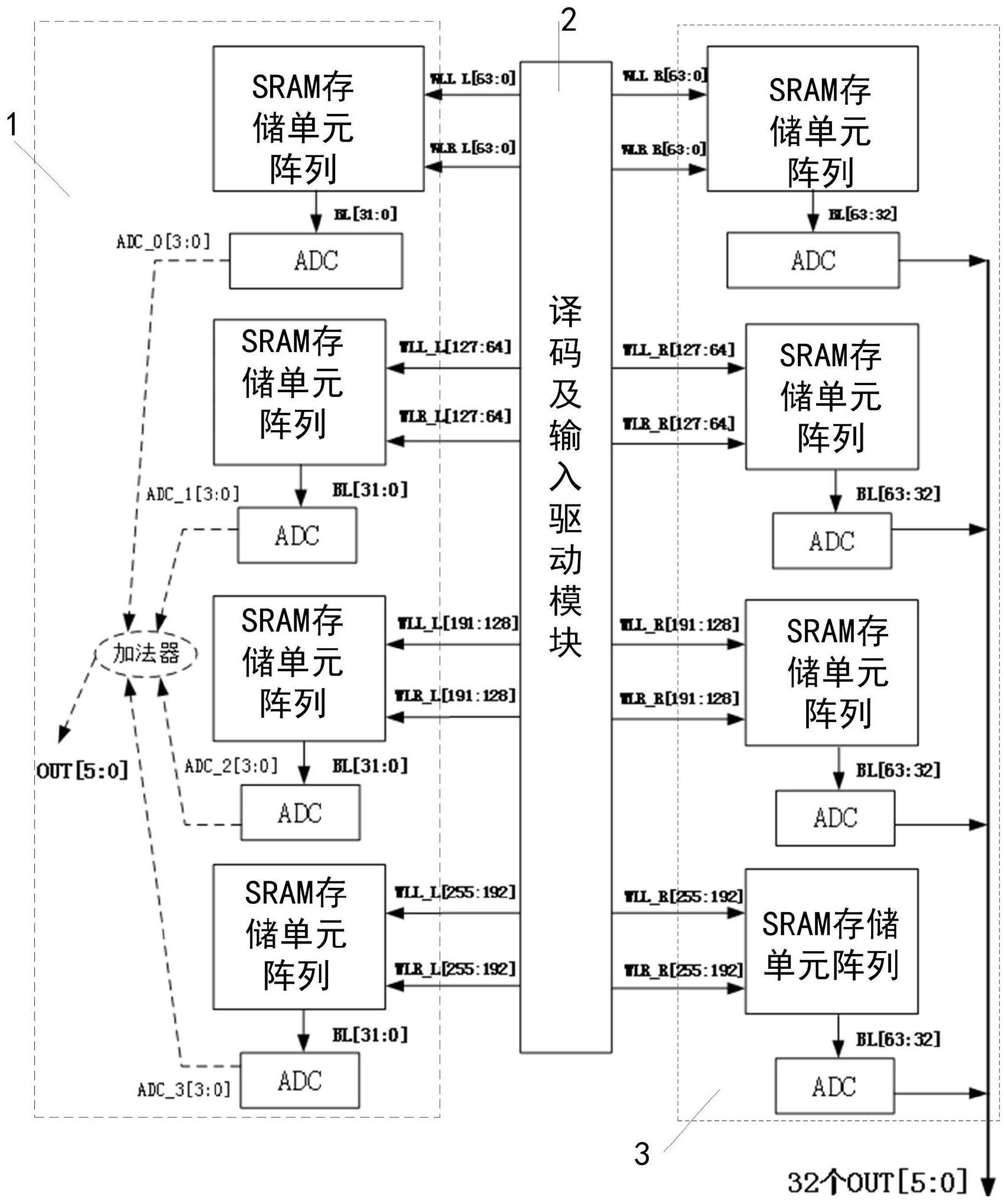

3、一种单比特存内计算装置,包括:第一阵列模块、译码及输入驱动模块以及第二阵列模块;

4、所述第一阵列模块和所述第二阵列模块均包括:4个sram存储单元阵列、4个模拟数字转换器adc模块以及1个加法器模块;所述sram存储单元阵列为64行乘以32列;

5、每个所述sram存储单元阵列与对应的所述模拟数字转换器adc模块连接;所述模拟数字转换器adc模块用于将对应的所述sram存储单元阵列中每列64行的计算结果进行量化,确定量化结果;

6、4个所述模拟数字转换器adc模块均与所述加法器模块连接;所述加法器模块用于将4个所述模拟数字转换器adc模块的量化结果进行加和;

7、所述译码及输入驱动模块包括:字线wll_l、字线wlr_l、字线wll_r以及字线wlr_r;所述字线wll_l和所述字线wlr_l用于驱动所述第一阵列模块的每一列sram存储单元阵列;所述字线wll_r和所述字线wlr_r用于驱动所述第二阵列模块的每一列sram存储单元阵列。

8、可选地,所述量化结果的位数为4位。

9、可选地,所述加法器模块的加和结果的位数为6位。

10、可选地,所述加法器模块的加和结果的个数为32个。

11、可选地,所述字线wll_l和字线wlr_l不同时工作;所述字线wll_r和字线wlr_r不同时工作。

12、可选地,所述sram存储单元阵列包括:64×32个6tsram存储单元。

13、根据本发明提供的具体实施例,本发明公开了以下技术效果:

14、本发明所提供的一种单比特存内计算装置,其中第一阵列模块和第二阵列模块均包括:4个sram存储单元阵列,即用4×2个64行×32列的小阵列来实现单比特存内计算的256行×64列大阵列的功能;每个阵列模块中每部分量化出一个结果,最后四个结果加起来,用于减轻对每列256行权重与256个输入的乘法计算结果的量化困难,而且可以提高输出结果的精度。每行字线脉冲分别驱动32列,减轻了字线的驱动难度,减轻了字线驱动过程中的脉宽衰减。

技术特征:

1.一种单比特存内计算装置,其特征在于,包括:第一阵列模块、译码及输入驱动模块以及第二阵列模块;

2.根据权利要求1所述的一种单比特存内计算装置,其特征在于,所述量化结果的位数为4位。

3.根据权利要求1所述的一种单比特存内计算装置,其特征在于,所述加法器模块的加和结果的位数为6位。

4.根据权利要求1所述的一种单比特存内计算装置,其特征在于,所述加法器模块的加和结果的个数为32个。

5.根据权利要求1所述的一种单比特存内计算装置,其特征在于,所述字线wll_l和字线wlr_l不同时工作;所述字线wll_r和字线wlr_r不同时工作。

6.根据权利要求1所述的一种单比特存内计算装置,其特征在于,所述sram存储单元阵列包括:64×32个6tsram存储单元。

技术总结

本发明涉及一种单比特存内计算装置。该装置中第一阵列模块和第二阵列模块均包括:4个SRAM存储单元阵列、4个ADC模块及1个加法器模块;SRAM存储单元阵列为64行乘以32列;每个SRAM存储单元阵列与一个ADC模块连接;ADC模块将对应的SRAM存储单元阵列中每列64行的计算结果进行量化;4个ADC模块均与加法器模块连接;加法器模块将4个ADC模块的量化结果进行加和;字线WLL_L和字线WLR_L驱动第一阵列模块的每一列SRAM存储单元阵列;字线WLL_R和字线WLR_R驱动第二阵列模块的每一列SRAM存储单元阵列。本发明能够提高单比特存内计算读出精度。

技术研发人员:乔树山,黄茂森,游恒,尚德龙,周玉梅

受保护的技术使用者:中科南京智能技术研究院

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!