存储器控制器和控制方法、芯片、存储介质及电子设备与流程

本公开属于存储器,涉及控制器,特别是涉及存储器控制器和控制方法、芯片、存储介质及电子设备。

背景技术:

1、伪静态随机存储器(pseudo static random access memory,psram)是一种集成随机存储器和闪存存储器优点的新型存储器芯片。psram具有快速的读写速度、高可靠性、小封装、高密度存储等特点,目前已经广泛应用于各种移动设备和便携式电子设备中,例如智能手机、平板电脑、数码相机等。伪静态随机存储器控制器(pseudo static randomaccess memory controller,psram controller)是一种控制psram的电路,它可以实现对psram的读写控制、数据传输控制、时序控制等功能。

技术实现思路

1、本公开提供存储器控制器和控制方法、芯片、存储介质及电子设备,用于改善存储器接口数据的采样时序。

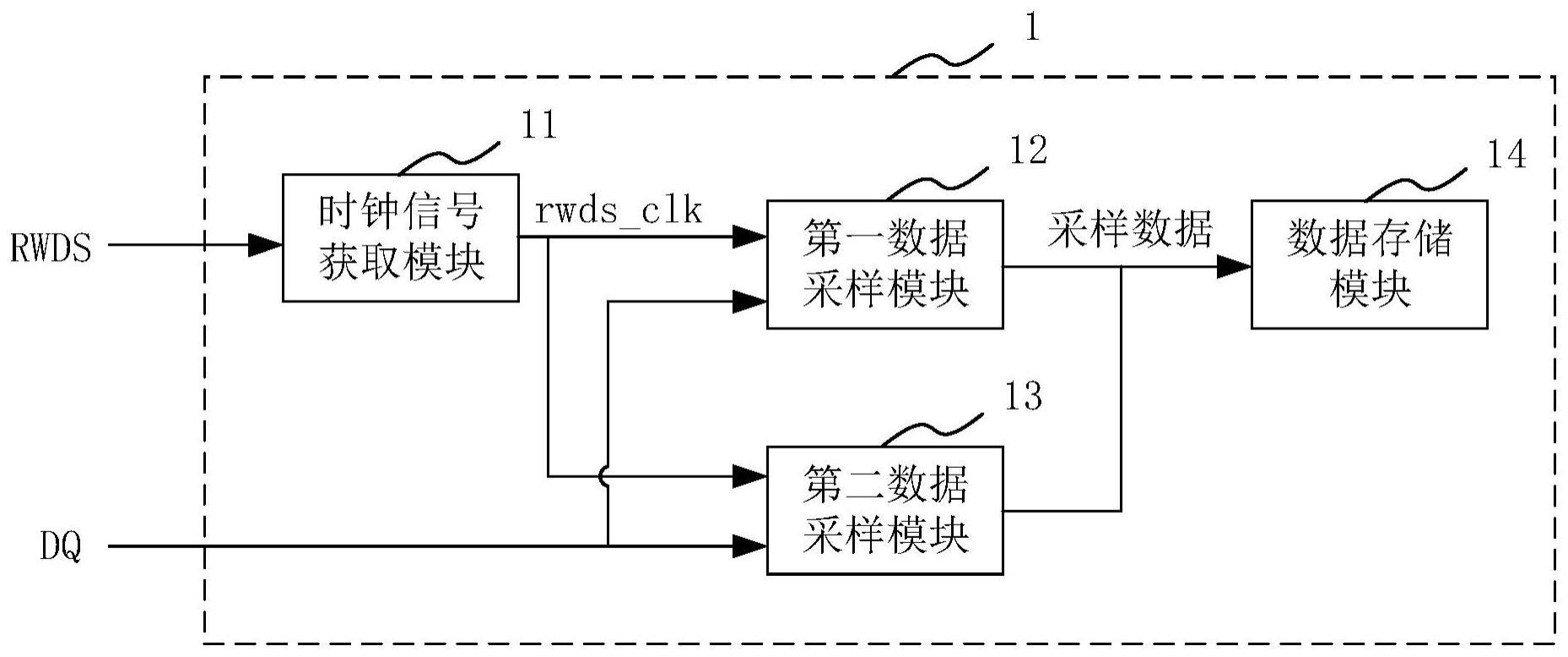

2、第一方面,本公开实施例提供存储器控制器。所述存储器控制器包括:时钟信号获取模块,被配置为对读写数据选通rwds信号进行处理以获取读写数据选通时钟信号,所述读写数据选通时钟信号的上升沿和下降沿对于数据信号有效;第一数据采样模块,被配置为响应于所述读写数据选通时钟信号的第一时钟周期的上升沿,对所述数据信号进行采样以得到第一采样数据;第二数据采样模块,被配置为响应于所述第一时钟周期的下降沿,对所述数据信号进行采样以得到第二采样数据;以及数据存储模块,被配置为根据所述读写数据选通时钟信号的第二时钟周期,写入所述第一采样数据和所述第二采样数据,所述第二时钟周期为所述第一时钟周期的下一时钟周期。

3、在第一方面的一种实现方式中,所述数据存储模块为跨异步存储器。

4、在第一方面的一种实现方式中,所述存储器控制器还包括写数据控制模块,所述写数据控制模块被配置为根据所述读写数据选通时钟信号控制所述数据存储模块在所述第二时钟周期内处于写数据状态。

5、在第一方面的一种实现方式中,所述写数据控制模块包括第一触发器,所述第一触发器被配置为:在数据输入端接收来自控制器时钟域的写使能信号;在时钟输入端接收所述读写数据选通时钟信号;以及在数据输出端输出读写数据选通时钟域的写使能控制信号,所述写使能控制信号用于控制所述数据存储模块在所述第二时钟周期内处于写数据状态。

6、在第一方面的一种实现方式中,所述数据存储模块进一步被配置为:当所述数据存储模块存储有采样数据时,在控制时钟域的时钟信号的触发沿将所述采样数据依次输出。

7、在第一方面的一种实现方式中,在所述数据存储模块中的目标采样数据均输出完成后,所述数据存储模块、所述写入控制模块、所述第一数据采样模块和所述第二数据采样模块分别进一步被配置为根据接收到的复位信号进行异步复位。

8、在第一方面的一种实现方式中,所述数据存储模块进一步被配置为:在所述数据存储模块中写入的采样数据达到终止条件时,根据接收到的高电平片选信号停止写入采样数据。

9、在第一方面的一种实现方式中,所述时钟信号获取模块包括延迟线单元,所述延迟线单元被配置为对所述读写数据选通rwds信号进行延迟处理以得到所述读写数据选通时钟信号。

10、在第一方面的一种实现方式中,所述第一数据采样模块包括第二触发器,所述第二触发器被配置为在数据输入端接收所述数据信号,在时钟输入端接收所述读写数据选通时钟信号,以及在输出端输出所述第一采样数据;所述第二数据采样模块包括第三触发器,所述第三触发器被配置为在数据输入端接收所述数据信号,在时钟输入端接收所述读写数据选通时钟信号的反相信号,以及在输出端输出所述第二采样数据。

11、第二方面,本公开实施例提供芯片,所述芯片包括本公开第一方面任一项所述的存储器控制器。

12、第三方面,本公开实施例提供存储器控制方法。所述存储器控制方法包括:对读写数据选通rwds信号进行处理以获取读写数据选通时钟信号,所述读写数据选通时钟信号的上升沿和下降沿对于数据信号有效;响应于所述读写数据选通时钟信号的第一时钟周期的上升沿,对所述数据信号进行采样以得到第一采样数据;响应于所述第一时钟周期的下降沿,对所述数据信号进行采样以得到第二采样数据;根据所述读写数据选通时钟信号的第二时钟周期,写入所述第一采样数据和所述第二采样数据,所述第二时钟周期为所述第一时钟周期的下一时钟周期。

13、第四方面,本公开实施例提供计算机可读存储介质,其上存储有计算机程序,所述计算机程序被执行以实现根据本公开第三方面所述的存储器控制方法。

14、第五方面,本公开实施例提供电子设备。所述电子设备包括:存储器,被配置为存储计算机程序;以及处理器,被配置为调用所述计算机程序以执行根据本公开第三方面所述的存储器控制方法。

15、本公开实施例提供的存储器控制器从存储器中读数据时通过读写数据选通时钟信号进行计数,在读写数据选通时钟信号的上升沿和下降沿分别对数据信号进行采样,并在下一个时钟周期的上升沿将两个采样数据合并写入数据存储模块。此种方式能够减少传输错误,并可以提高传输带宽。

16、此外,本公开实施例提供的存储器控制器将采样得到的信号延迟一个时钟周期再发送给后续电路,能够有效改善信号由于各种延时导致不能满足时序要求的情况,有利于改善数据采样时序。

技术特征:

1.一种存储器控制器,其特征在于,包括:

2.根据权利要求1所述的存储器控制器,其特征在于,所述数据存储模块为跨异步存储器。

3.根据权利要求1所述的存储器控制器,其特征在于,还包括写数据控制模块,所述写数据控制模块被配置为根据所述读写数据选通时钟信号控制所述数据存储模块在所述第二时钟周期内处于写数据状态。

4.根据权利要求3所述的存储器控制器,其特征在于,所述写数据控制模块包括第一触发器,所述第一触发器被配置为:

5.根据权利要求3所述的存储器控制器,其特征在于,所述数据存储模块进一步被配置为:

6.根据权利要求5所述的存储器控制器,其特征在于,在所述数据存储模块中的目标采样数据均输出完成后,所述数据存储模块、所述写入控制模块、所述第一数据采样模块和所述第二数据采样模块分别进一步被配置为根据接收到的复位信号进行异步复位。

7.根据权利要求1所述的存储器控制器,其特征在于,所述数据存储模块进一步被配置为:

8.根据权利要求1所述的存储器控制器,其特征在于,所述时钟信号获取模块包括延迟线单元,所述延迟线单元被配置为对所述读写数据选通rwds信号进行延迟处理以得到所述读写数据选通时钟信号。

9.根据权利要求1所述的存储器控制器,其特征在于,所述第一数据采样模块包括第二触发器,所述第二触发器被配置为在数据输入端接收所述数据信号,在时钟输入端接收所述读写数据选通时钟信号,以及在输出端输出所述第一采样数据;

10.一种芯片,其特征在于,包括权利要求1至9中任一项所述的存储器控制器。

11.一种存储器控制方法,其特征在于,包括:

12.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被执行以实现根据权利要求11所述的存储器控制方法。

13.一种电子设备,其特征在于,包括:

技术总结

本公开提供存储器控制器和控制方法、芯片、存储介质及电子设备。所述存储器控制器包括:时钟信号获取模块,被配置为对读写数据选通RWDS信号进行处理以获取读写数据选通时钟信号;第一数据采样模块,被配置为响应于所述读写数据选通时钟信号的第一时钟周期的上升沿,对所述数据信号进行采样以得到第一采样数据;第二数据采样模块,被配置为响应于所述第一时钟周期的下降沿,对所述数据信号进行采样以得到第二采样数据;数据存储模块,被配置为根据所述读写数据选通时钟信号的第二时钟周期,写入所述第一采样数据和所述第二采样数据。所述存储器控制器能够提高传输带宽,并可以改善数据采样时序。

技术研发人员:湛厚超,黄杨国,魏天博

受保护的技术使用者:瑞芯微电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!