一种铪基铁电场效应晶体管实现的冯诺依曼架构

本发明涉及存储器,尤其涉及一种铪基铁电场效应晶体管实现的冯诺依曼架构。

背景技术:

1、冯诺依曼架构是现代计算机的基础,冯诺依曼架构基于三条主要思想而设立,且其主要特点在于实现存储和计算分离。其中,第一主要思想为计算机硬件分为五个基本组成部分,包括:运算器、控制器、存储器、输入设备和输出设备;第二主要思想为计算机内部的指令和数据都利用二进制编码;第三主要思想为编好的程序送入存储器中能自动逐条取出指令和执行指令。

2、但是由于冯诺依曼架构集中、顺序的控制特点,其在控制过程中需要多步调用,且其内部的ssd、dram和cache三种存储器在速度和体积上有很大的差异,所以形成了严重的存储墙问题,如此成为了阻碍冯诺依曼架构进一步微缩的重要因素。

3、因此,如何解决冯诺依曼架构中的存储墙问题,以实现冯诺依曼架构进一步微缩,成为亟需解决的难题。

技术实现思路

1、为解决上述问题,本发明提供的一种铪基铁电场效应晶体管实现的冯诺依曼架构,通过将氧化铪基铁电场效应晶体管设置为主存储器和存储级内存的存储元,解决了冯诺依曼架构中主存储器和存储级内存之间存储墙的问题,并可实现冯诺依曼架构进一步的微缩。

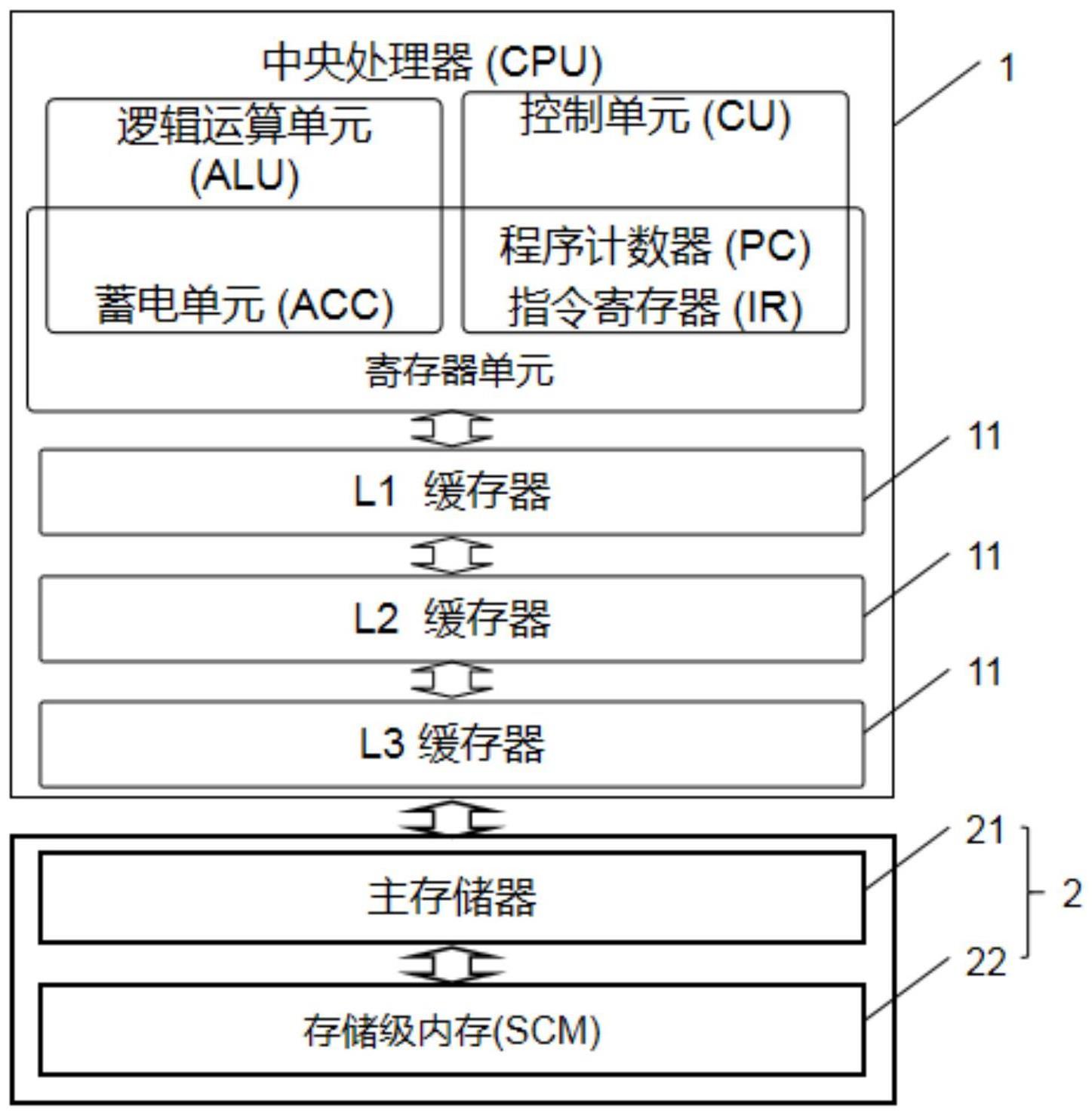

2、本发明提供一种铪基铁电场效应晶体管实现的冯诺依曼架构,包括:中央处理器和存储器;

3、存储器包括:主存储器和存储级内存;

4、存储级内存与主存储器通信连接,主存储器与中央处理器通信连接;

5、存储级内存包含有多个第一晶体管,主存储器包含有多个第二晶体管,第一晶体管用于实现存储级内存的存储功能,第二晶体管用于实现主存储器的存储功能;

6、第一晶体管和第二晶体管均为氧化铪基铁电场效应晶体管。

7、可选地,中央处理器包括:缓存器;

8、缓存器与主存储器通信连接;

9、缓存器包含有多个第三晶体管,第三晶体管用于实现缓存器的存储功能,第三晶体管为氧化铪基铁电场效应晶体管。

10、可选地,存储级内存还包含有至少一条第一源极线、多条第一字线和多条第一位线;

11、每条第一字线分别与多个第一晶体管电连接,每条第一字线上的第一晶体管与相邻的第一字线上的一第一晶体管串联,每一组串联的第一晶体管的首尾两端分别与第一源极线和一条第一位线电连接;

12、或,每条所述第一字线分别与多个所述第一晶体管电连接,每条所述第一字线上的所述第一晶体管分别与相邻的所述第一字线上的一所述第一晶体管共接一条所述第一位线,共接所述第一位线的所述第一晶体管共接一条所述第一源极线。

13、可选地,主存储器还包含至少一条第二源极线、有多条第二字线和多条第二位线;

14、每条所述第二字线分别与多个所述第二晶体管电连接,每条所述第二字线上的所述第二晶体管与相邻的所述第二字线上的一所述第二晶体管串联,每一组串联的第二晶体管的首尾两端分别与所述第二源极线和一条所述第二位线电连接;

15、或,每条第二字线分别与多个第二晶体管电连接,每条第二字线上的第二晶体管分别与相邻的第二字线上的一第二晶体管共接一条第二位线,共接所述第二位线的所述第二晶体管共接一条所述第二源极线。

16、可选地,主存储器和存储级内存集成在同一芯片上。

17、可选地,缓存器还包含有至少一条第三源极线、多条第三字线和多条第三位线;

18、每条所述第三字线分别与多个所述第三晶体管电连接,每条所述第三字线上的所述第三晶体管与相邻的所述第三字线上的一所述第三晶体管串联,每一组串联的第三晶体管的首尾两端分别与所述第三源极线和一条所述第三位线电连接;

19、或,每条第三字线分别与多个第三晶体管电连接,每条第三字线上的第三晶体管分别与相邻的第三字线上的一第三晶体管共接一条第三位线,共接所述第三位线的所述第三晶体管共接一条所述第三源极线。

20、可选地,缓存器、主存储器和存储级内存集成在同一芯片上。

21、可选地,氧化铪基铁电场效应晶体管的铁电层材料包括:hfo2、hzo、hfsio、hfalo和hflao中的至少一种。

22、可选地,氧化铪基铁电场效应晶体管的沟道材料包括:si、iwo和igzo中的至少一种。

23、可选地,氧化铪基铁电场效应晶体管的衬底包括:si衬底或fdsoi衬底。

24、本发明实施例提供的一种铪基铁电场效应晶体管实现的冯诺依曼架构,通过将氧化铪基铁电场效应晶体管设置为主存储器和存储级内存的存储元,氧化铪基铁电场效应晶体管通过电场诱导铁电铪基氧化物极化方向发生改变,产生高低阈值电压态,实现了二进制信息的存储,并具有功耗低、读写速度快、可进行非破坏读取、微缩性好以及与cmos工艺兼容等优点,从而解决了冯诺依曼架构中主存储器和存储级内存之间存储墙的问题,并可实现冯诺依曼架构进一步的微缩。

技术特征:

1.一种铪基铁电场效应晶体管实现的冯诺依曼架构,其特征在于,包括:中央处理器和存储器;

2.根据权利要求1所述的冯诺依曼架构,其特征在于,所述中央处理器包括:缓存器;

3.根据权利要求1所述的冯诺依曼架构,其特征在于,所述存储级内存还包含有至少一条第一源极线、多条第一字线和多条第一位线;

4.根据权利要求1所述的冯诺依曼架构,其特征在于,所述主存储器还包含有至少一条第二源极线、多条第二字线和多条第二位线;

5.根据权利要求1所述的冯诺依曼架构,其特征在于,所述主存储器和所述存储级内存集成在同一芯片上。

6.根据权利要求2所述的冯诺依曼架构,其特征在于,所述缓存器还包含有至少一条第三源极线、多条第三字线和多条第三位线;

7.根据权利要求2所述的冯诺依曼架构,其特征在于,所述缓存器、所述主存储器和所述存储级内存集成在同一芯片上。

8.根据权利要求1至7任一项所述的冯诺依曼架构,其特征在于,所述氧化铪基铁电场效应晶体管的铁电层材料包括:hfo2、hzo、hfsio、hfalo和hflao中的至少一种。

9.根据权利要求1至7任一项所述的冯诺依曼架构,其特征在于,所述氧化铪基铁电场效应晶体管的沟道材料包括:si、iwo和igzo中的至少一种。

10.根据权利要求1至7任一项所述的冯诺依曼架构,其特征在于,所述氧化铪基铁电场效应晶体管的衬底包括:si衬底或fdsoi衬底。

技术总结

本发明提供一种铪基铁电场效应晶体管实现的冯诺依曼架构,包括:中央处理器和存储器;存储器包括:主存储器和存储级内存;存储级内存与主存储器通信连接,主存储器与中央处理器通信连接;存储级内存包含有多个第一晶体管,主存储器包含有多个第二晶体管,第一晶体管用于实现存储级内存的存储功能,第二晶体管用于实现主存储器的存储功能;第一晶体管和第二晶体管均为氧化铪基铁电场效应晶体管。本发明能够解决冯诺依曼架构中的存储墙问题。

技术研发人员:王晓磊,丁雅静,张骥,胡涛,柴俊帅,徐昊,王文武

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!