布置读取数据以用于输出的设备及方法与流程

本公开涉及布置读取数据以用于输出的设备及方法。

背景技术:

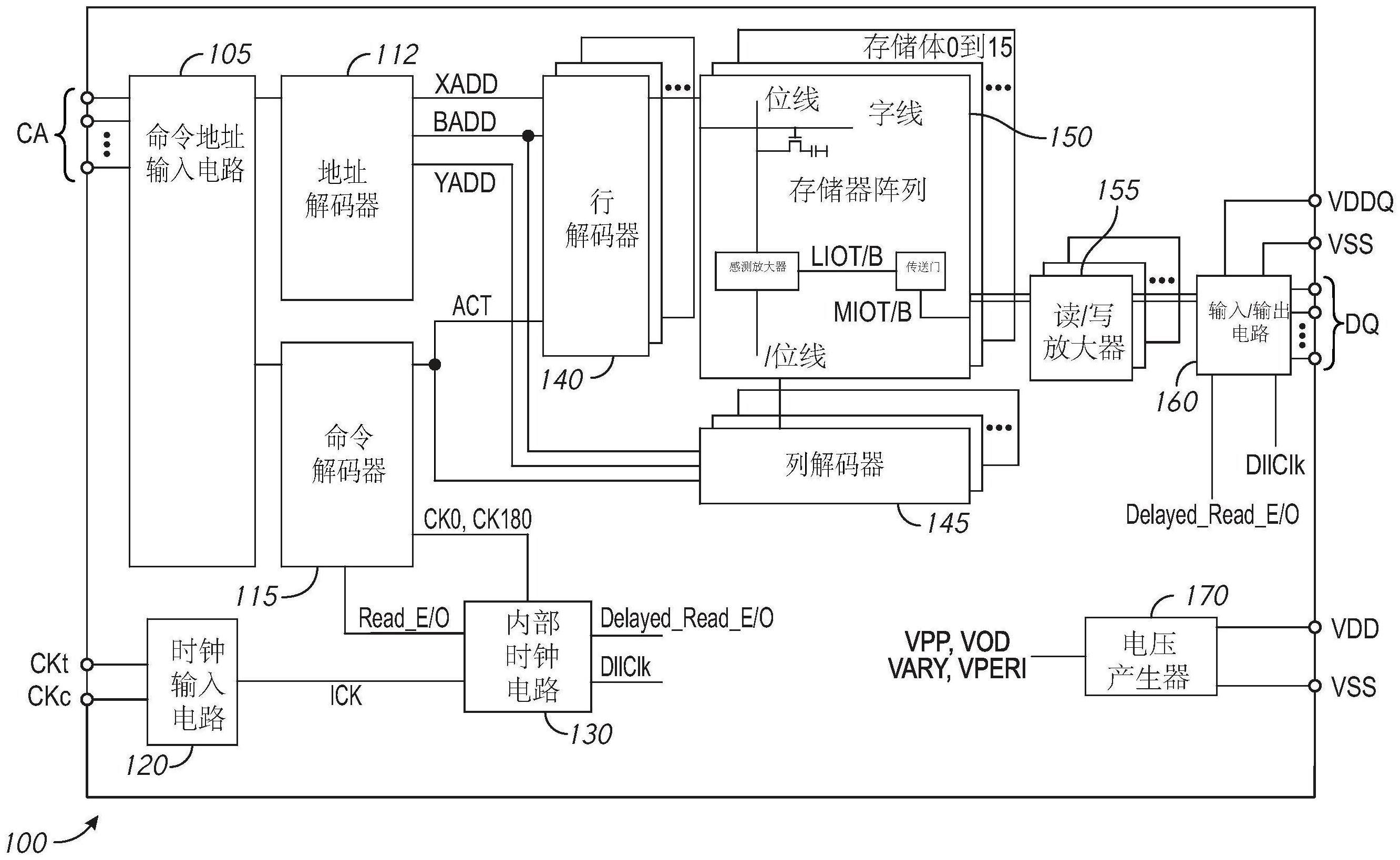

1、半导体存储器在许多电子系统中用于存储可在稍后检索的数据。半导体存储器通常通过向存储器提供命令信号、地址信号及时钟来控制。命令信号可控制半导体存储器执行各种存储器操作,例如,从存储器检索数据的读取操作及将数据存储到存储器的写入操作。对由地址信号标识的存储器位置执行存储器操作。

2、包含在半导体存储器中的时钟电路可使用外部时钟来产生内部时钟,所述内部时钟又在执行各种操作时被使用。所产生的内部时钟可具有比外部时钟更低的时钟频率,这可导致内部时钟与外部时钟具有同相关系(偶数时钟)或与外部时钟具有异相关系(奇数时钟)。

3、一些时钟电路可使用内部时钟来提供多相时钟,例如,多相时钟可用于对存储器提供及/或接收数据进行定时。在提供多相时钟时,时钟电路可锁定同相内部时钟或异相内部时钟。因此,依赖于内部时钟及/或多相时钟的存取操作可同相时控或异相时控。

4、异相时控存储器操作可导致半导体存储器无序地提供读取数据。当存储器操作异相时控时,用异相时钟交换同相时钟可解决读取数据无序的问题。然而,为了保持外部时钟与内部时钟的同步,应同步交换时钟,这是具有挑战性的,并且可导致延迟的存取时间或时序不准确。

技术实现思路

1、在一个方面中,本公开提供一种设备,其包括:时钟电路,其经配置以基于时钟信号提供具有彼此不同的相位的多相时钟信号;数据输出电路,其经配置以响应于读取命令接收多个读取数据位,并与所述多相时钟信号中的对应一者同步地串行输出所述多个读取数据位中的每一者;以及控制电路,其经配置以基于关于所述多相时钟信号中的哪一个捕获所述读取命令的信息来确定所述多个读取数据位与所述多相时钟信号之间的对应关系。

2、在另一方面中,本公开提供一种设备,其包括:数据输出电路,其经配置以基于多相时钟接收用于读取命令的读取数据,所述数据输出电路经配置以在时控同相时将所述读取数据布置为同相,并且所述数据输出电路进一步经配置以在时控异相时将所述读取数据布置为异相,所述数据输出电路进一步经配置以至少部分地基于所述读取数据的所述布置以位顺序串行地提供所述读取数据;以及数据输出缓冲器,其经配置以从所述数据输出电路接收所述读取数据并串行地提供所述读取数据。

3、在另一方面中,本公开提供一种设备,其包括:数据寄存器,其经配置以接收多相时钟并进一步并行地接收用于读取命令的读取数据且并行地提供所述读取数据,并且具有分别基于对操作的同相或异相时控的同相或异相布置;串行器电路,其经配置以从所述数据寄存器并行地接收所述读取数据,并将所述读取数据转换成串行位流;以及数据输出缓冲器,其经配置以接收所述串行位流读取数据并串行地提供所述读取数据。

4、在另一方面中,本公开提供一种方法,其包括:确定操作是根据偶数时钟还是奇数时钟来时控;并行接收读取数据;如果所述对操作的时控是基于所述奇数时钟,那么重新布置所述读取数据;以及将所述经重新布置的读取数据转换成串行位流。

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其中所述控制电路进一步经配置以另外基于关于所述时钟电路被锁定到以提供所述多相时钟信号的时钟沿的信息来确定所述多个读取数据位与所述多相时钟信号之间的所述对应关系。

3.根据权利要求2所述的设备,其中所述控制电路进一步经配置以另外基于关于所述读取命令的读取延时的偶数或奇数信息来确定所述多个读取数据位与所述多相时钟信号之间的所述对应关系。

4.根据权利要求3所述的设备,其中如果关于多相时钟信号中的哪一个捕获所述读取命令的信息、关于所述时钟电路锁定到的时钟沿的信息、或者关于所述读取命令的读取延时的偶数或奇数信息中的任一者指示奇数状态,那么所述控制电路提供具有第一逻辑电平的控制信号,以及如果关于多相时钟信号中的哪一个捕获所述读取命令的信息、关于所述时钟电路锁定到的时钟沿的信息及关于所述读取命令的读取延时的所述偶数或奇数信息全部指示奇数状态,那么所述控制电路提供具有所述第一逻辑电平的所述控制信号。

5.根据权利要求4所述的设备,其中所述控制电路针对关于多相时钟信号中的哪一个捕获所述读取命令的信息、关于所述时钟电路锁定到的所述时钟沿的信息及关于所述读取命令的读取延时的所述偶数或奇数信息的所有其它组合提供具有第二逻辑电平的所述控制信号。

6.一种设备,其包括:

7.根据权利要求6所述的设备,其中所述数据输出电路包括:

8.根据权利要求6所述的设备,其进一步包括时钟分频器电路,所述时钟分频器电路经配置以接收内部时钟以提供具有小于所述内部时钟的时钟频率的偶数时钟及奇数时钟,所述偶数时钟具有与所述内部时钟的偶数周期对准的上升时钟沿,并且所述奇数时钟具有与所述内部时钟的奇数周期对准的上升时钟沿。

9.根据权利要求6所述的设备,其中所述数据输出电路进一步经配置以基于至少一个命令信号根据读取突发顺序来提供所述读取数据。

10.根据权利要求6所述的设备,其中所述数据输出电路经配置以基于所述读取命令的偶数/奇数状态及提供所述多相时钟的时钟电路被锁定到的偶数/奇数沿来确定对操作的偶数或奇数时控。

11.根据权利要求6所述的设备,其中所述多相时钟包含相位0时钟、相位90时钟、相位180时钟及相位270时钟,并且所述数据输出电路经配置以通过交换对应于所述相位0及相位180时钟的所述读取数据的位并交换对应于所述相位90及相位270时钟的所述读取数据的所述位来异相提供所述读取数据。

12.一种设备,其包括:

13.根据权利要求12所述的设备,其中所述数据寄存器包括:

14.根据权利要求13所述的设备,其中所述数据寄存器进一步包括第二多路复用器及第三多路复用器,所述第二多路复用器及第三多路复用器经配置以基于提供给所述第二多路复用器的第二多路复用器控制信号及提供给所述第三多路复用器的第三多路复用器控制信号以读取突发顺序从所述多路复用器提供读取数据,其中所述多路复用器控制电路基于第一命令信号提供所述第二多路复用器控制信号,并且基于第二命令信号提供所述第三多路复用器控制信号。

15.根据权利要求13所述的设备,其中所述多路复用器包括多个多路复用器电路,所述多路复用器电路中的每两个多路复用器电路经配置以接收所述读取数据的相同的两个位,并且在所述多路复用器控制信号具有第一逻辑电平时交换所述两个位的数据,并且在所述多路复用器控制信号具有第二逻辑电平时不交换所述两个位的数据。

16.根据权利要求13所述的设备,其中所述多路复用器控制电路包括:

17.根据权利要求12所述的设备,其中所述读取数据包括位dr[0:15],并且所述数据输出电路经配置以通过交换所述读取数据的位来提供具有异相布置的所述读取数据,其中位dr[4m]及数据dr[4m+2]被交换,并且数据dr[4m+1]及数据dr[4m+3]被所述数据输出电路交换,其中m是0、1、2或3。

18.根据权利要求12所述的设备,其中所述对操作的同相时控是基于同相时钟,并且所述对操作的异相时控是基于与所述同相时钟异相180度的时钟。

19.一种方法,其包括:

20.根据权利要求19所述的方法,其中确定操作是根据所述偶数时钟还是所述奇数时钟来时控是基于所述读取命令的偶数/奇数状态及提供多相时钟的时钟电路被锁定到的偶数/奇数沿。

21.根据权利要求20所述的方法,其中确定操作是根据所述偶数时钟还是所述奇数时钟来时控是进一步基于偶数/奇数读取延时模式。

22.根据权利要求21所述的方法,其中如果所述读取命令的所述偶数/奇数状态、提供所述多相时钟的时钟电路被锁定到的所述偶数/奇数沿或所述偶数/奇数读取延时模式中的任一者是奇数,以及如果所述读取命令的所述偶数/奇数状态、提供所述多相时钟的时钟电路被锁定到的所述偶数/奇数沿及所述偶数/奇数读取延时模式全部是奇数,那么根据所述奇数时钟对操作进行时控。

23.根据权利要求19所述的方法,其中基于包含相位0时钟、相位90时钟、相位180时钟及相位270时钟的多相时钟来接收所述读取数据,并且其中在所述对操作的时控是基于所述奇数时钟时重新布置所述读取数据包括交换对应于所述相位0及相位180时钟的所述读取数据的位以及交换对应于所述相位90及相位270时钟的所述读取数据的所述位。

24.根据权利要求19所述的方法,其进一步包括在将所述重新布置的读取数据转换成串行位流之前,将所述读取数据布置成读取突发顺序,所述读取突发顺序由至少一个命令信号设置。

技术总结

描述用于布置读取数据以用于输出的设备及方法。实例设备包含时钟电路、数据输出电路及控制电路。所述时钟电路经配置以基于时钟信号提供具有彼此不同的相位的多相时钟信号。所述数据输出电路经配置以响应于读取命令接收多个读取数据位,并与所述多相时钟信号中的对应一者同步地串行输出所述多个读取数据位中的每一者。所述控制电路经配置以基于关于所述多相时钟信号中的哪一个捕获所述读取命令的信息来确定所述多个读取数据位与所述多相时钟信号之间的对应关系。

技术研发人员:藤巻亮

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!