灵敏放大器及存储芯片的制作方法

本申请涉及存储,具体涉及一种灵敏放大器及存储芯片。

背景技术:

1、存储芯片的存储阵列除了用来存储用户数据的主存储阵列外,还有许多存储不同数据的小存储阵列。

2、由于与主存储阵列连接的位线的负载、小存储阵列连接的位线的负载不同,与主存储阵列连接的灵敏放大器的架构、与小存储阵列连接的灵敏放大器的架构也不一致,从而导致小存储阵列中存储单元的特性与主存储阵列中存储单元的特性存在不一致,进而对存储器的性能产生影响。

技术实现思路

1、本申请提供一种灵敏放大器及存储芯片,以缓解不同存储阵列难以共用同一灵敏放大器架构的技术问题。

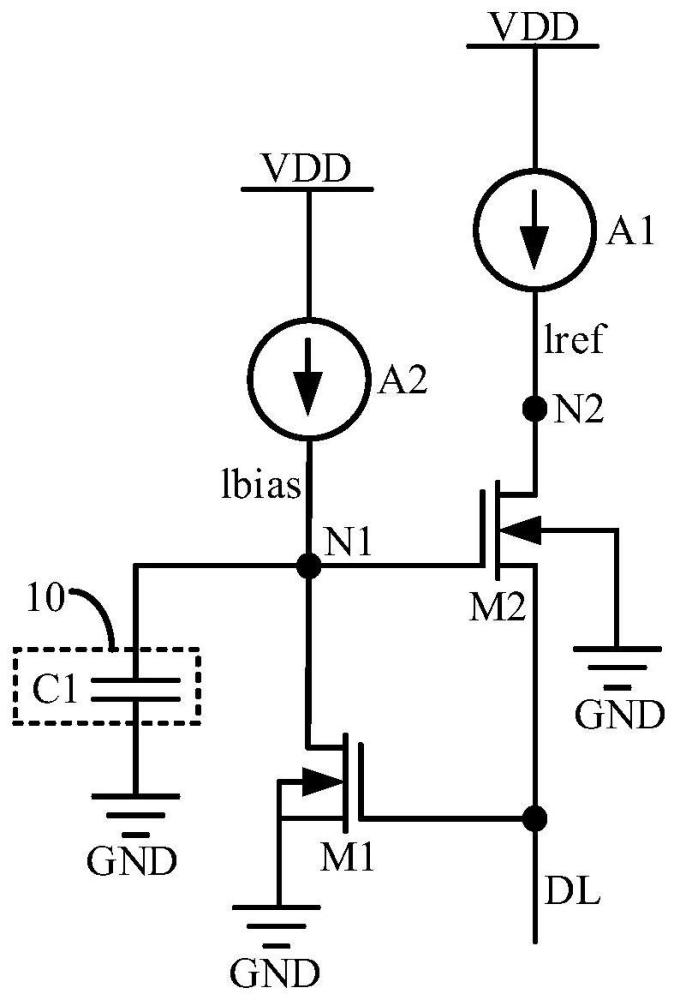

2、第一方面,本申请提供一种灵敏放大器,该灵敏放大器包括数据线、第一电流源、第二电流源、第一晶体管、第二晶体管、以及容性模块,第一电流源的一端与电源端连接;第二电流源的一端与电源端连接;第一晶体管的第一极与第一电流源的另一端连接,第一晶体管的第二极与数据线连接;第二晶体管的第一极与第二电流源的另一端、第一晶体管的栅极连接,第二晶体管的第二极与接地端连接,第二晶体管的栅极与数据线连接;容性模块串联于第一晶体管的栅极与接地端之间。

3、在其中一些实施方式中,容性模块包括一第一电容,第一电容的一端与第一晶体管的栅极连接,第一电容的另一端与接地端连接。

4、在其中一些实施方式中,容性模块包括多个并联的第二电容,多个并联的第二电容的一端与第二晶体管的第一极连接,多个并联的第二电容的另一端与接地端连接。

5、在其中一些实施方式中,容性模块用于降低第一晶体管的栅极的电位的上升速度。

6、在其中一些实施方式中,容性模块还用于在数据线的电位控制第二晶体管导通的情况下限制第一晶体管的栅极的过冲电位。

7、在其中一些实施方式中,容性模块还用于减小数据线的电压过冲幅值,电压过冲幅值大于在灵敏放大器的读取过程中数据线的电位。

8、在其中一些实施方式中,第一晶体管、第二晶体管均为n沟道型的场效应晶体管;且第一晶体管的衬底、第二晶体管的衬底均连接接地端。

9、第二方面,本申请提供一种存储芯片,该存储芯片包括上述至少一实施方式中的灵敏放大器。

10、在其中一些实施方式中,存储芯片还包括存储阵列,存储阵列包括主存储阵列和小存储阵列,小存储阵列与灵敏放大器连接,主存储阵列与灵敏放大器或者与不具有容性模块的所述灵敏放大器连接。

11、在其中一些实施方式中,存储芯片还包括解码电路和位线,解码电路与数据线连接;多条位线与解码电路连接。

12、本申请提供的灵敏放大器及存储芯片,通过数据线、第一电流源、第二电流源、第一晶体管、第二晶体管、以及容性模块搭建起来的架构,在应用于小存储阵列的情况下,可以在灵敏放大器刚开始读取时通过容性模块控制第一晶体管的栅极的电位上升速度以及上升高度,从而缓解对第一晶体管的电压冲击,使得与小存储阵列连接的数据线或者位线的电位不会过度冲高,从而使得小存储阵列中存储单元的特性趋向于主存储阵列中存储单元的特性,而容性模块在充满电后不会影响到小存储阵列、主存储阵列中存储单元的特性,进而使得不同的存储阵列能够共用同一灵敏放大器架构。

13、又,相较于容性模块连接数据线来达到相同效果而需要容性模块具有更大的电容量,容性模块连接第一晶体管的栅极,可以减小容性模块的电容量,进而减小了灵敏放大器或者存储芯片的面积。

技术特征:

1.一种灵敏放大器,其特征在于,所述灵敏放大器包括:

2.根据权利要求1所述的灵敏放大器,其特征在于,所述容性模块包括一第一电容,所述第一电容的一端与所述第一晶体管的栅极连接,所述第一电容的另一端与所述接地端连接。

3.根据权利要求1所述的灵敏放大器,其特征在于,所述容性模块包括多个并联的第二电容,所述多个并联的第二电容的一端与所述第二晶体管的第一极连接,所述多个并联的第二电容的另一端与所述接地端连接。

4.根据权利要求1所述的灵敏放大器,其特征在于,所述容性模块用于降低所述第一晶体管的栅极的电位的上升速度。

5.根据权利要求4所述的灵敏放大器,其特征在于,所述容性模块还用于在所述数据线的电位控制所述第二晶体管导通的情况下限制所述第一晶体管的栅极的过冲电位。

6.根据权利要求5所述的灵敏放大器,其特征在于,所述容性模块还用于减小所述数据线的电压过冲幅值,所述电压过冲幅值大于在所述灵敏放大器的读取过程中所述数据线的电位。

7.根据权利要求1-6任一项所述的灵敏放大器,其特征在于,所述第一晶体管、所述第二晶体管均为n沟道型的场效应晶体管;且所述第一晶体管的衬底、所述第二晶体管的衬底均连接接地端。

8.一种存储芯片,其特征在于,所述存储芯片包括如权利要求1-7任一项所述的灵敏放大器。

9.根据权利要求8所述的存储芯片,其特征在于,所述存储芯片还包括存储阵列,所述存储阵列包括主存储阵列和小存储阵列,所述小存储阵列与所述灵敏放大器连接,所述主存储阵列与所述灵敏放大器或者与不具有所述容性模块的所述灵敏放大器连接。

10.根据权利要求8所述的存储芯片,其特征在于,所述存储芯片还包括:

技术总结

本申请公开了一种灵敏放大器及存储芯片,该灵敏放大器包括数据线、第一电流源、第二电流源、第一晶体管、第二晶体管、以及容性模块,通过数据线、第一电流源、第二电流源、第一晶体管、第二晶体管、以及容性模块搭建起来的架构,在应用于小存储阵列的情况下,可以在灵敏放大器刚开始读取时通过容性模块控制第一晶体管的栅极的电位上升速度以及上升高度,从而缓解对第一晶体管的电压冲击,使得与小存储阵列连接的数据线或者位线的电位不会过度冲高,从而使得小存储阵列中存储单元的特性趋向于主存储阵列中存储单元的特性,而容性模块在充满电后不会影响到小存储阵列、主存储阵列中存储单元的特性,进而使得不同的存储阵列能够共用同一灵敏放大器架构。

技术研发人员:杜艳强

受保护的技术使用者:武汉新芯集成电路制造有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!