应用于存算一体电路的10晶体管SRAM存储单元结构的制作方法

本发明涉及半导体,特别是涉及一种应用于存算一体电路的10晶体管sram存储单元结构。

背景技术:

1、随着云计算、人工智能等技术的发展,我们已步入大数据时代。在过去的几十年中,存储器与处理器的发展严重失衡,存储器读取速率的提升远远跟不上处理器性能的增长。传统的冯诺依曼计算架构在数据密集型计算中表现出的性能瓶颈越发明显。冯诺依曼瓶颈的概念最早由john backus在1977年提出:由于cpu和存储器之间共享同一个系统总线,并且cpu和存储器之间存在巨大的速度差,导致cpu需要不断地被迫等待数据读取或写入到存储器,因此遏制了cpu的吞吐量。

2、近年来,存算一体计算架构越来越受到关注,有望成为突破冯诺依曼瓶颈的新架构。存算一体是将部分或全部的计算移到存储中,让存储单元具备计算功能。这样的架构消除了数据访存延迟和功耗,突破了冯诺依曼瓶颈,被工业界和学术界一致认为是未来的发展趋势。

3、存算一体可分为近存计算及存内计算,其中存内计算又分为“只改外围电路的存内计算”以及“存储单元和外围电路同时修改的存内计算”。

4、sram是目前唯一一种跟先进cmos工艺完全兼容且能大规模量产的存储介质。sram具有更快的操作速度和耐久性,可以实时在存算单元中刷新计算数据。

5、目前存算一体电路中使用的sram存储单元有很多种,根据不同的应用、不同的运算需求使用不同的sram结构。

6、现有技术中的一种双6晶体管双字线sram存储单元的结构如图1所示,其工作原理图如图2所示,设计要求读取端口的电流id远大于ic,因此双6晶体管双字线sram存储单元的版图并非传统的对称结构,再加上双字线走线的要求,单个存储单元的面积显著增加,大约是常规6t sram的2倍。

7、使用双6t双字线sram cell的话,面积就是常规6t sram的4倍,存储单元面积较大。

8、为解决上述问题,需要提出一种新型的应用于存算一体电路的10晶体管sram存储单元结构。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种应用于存算一体电路的10晶体管sram存储单元结构,用于解决现有技术中双6晶体管双字线sram存储单元的版图并非传统的对称结构,再加上双字线走线的要求,单个存储单元的面积显著增加,大约是常规6t sram的2倍,需要减少存储单元的面积的问题。

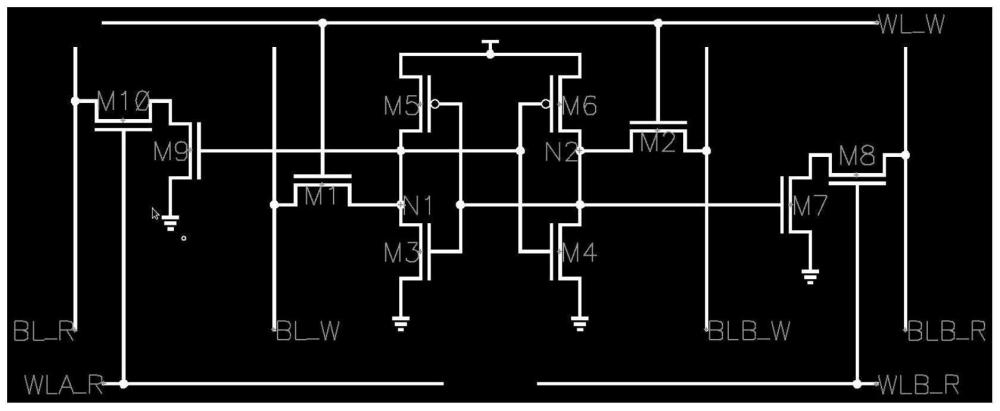

2、为实现上述目的及其他相关目的,本发明提供一种应用于存算一体电路的10晶体管sram存储单元结构,包括:

3、4个pmos晶体管m1、m2、m5、m6和6个nmos晶体管m3、m4、m7、m8、m9、m10;其中,其中m3、m4、m7、m9为下拉管,m5、m6为上升管,m1、和m2为传输管,m8和m10为选通管;

4、m5、m6的源极连接存储单元工作电源,m5、m6的漏极分别连接m3、m4的漏极;

5、m5的栅极连接m3的栅极形成第一存储节点n1,m6的栅极连接m4的栅极形成第二存储节点n2;

6、m3、m4的源极连接地线;

7、m1的源极连接信号bl_w,漏极连接第一存储节点n1,栅极连接信号wl_w;

8、m2的源极连接信号blb_w,漏极连接第二存储节点n2,栅极连接信号wl_w;

9、m7的源极连接地线,栅极连接第一存储节点n1,漏极连接m8的源极;

10、m8的漏极连接信号blb_r,栅极连接信号wlb_r;

11、m9的源极连接地线,栅极连接第二存储节点n2,漏极连接m10的源极;

12、m10的漏极连接信号bl_r,栅极连接信号wla_r;其中,

13、m1至m6组成6晶体管sram结构,其由信号wl_w控制;

14、m7、m8与m9、m10作为两个读取端口,分别由信号wlb_r及信号wla_r控制;

15、在10晶体管sram存储单元工作时,两个读取端口的电流存在差异。

16、优选地,所述m7、m8一侧的电流为m9、m10一侧的电流的目标倍数。

17、优选地,所述m7、m8一侧的电流为m9、m10一侧的电流的2至3倍。

18、优选地,所述m7、m8栅极宽度为m9、m10栅极宽度的2至3倍。

19、优选地,所述m5和m3组成第一反相器,m6和m4组成第二反相器,第一反相器与第二反相器交叉耦接形成锁存电路。

20、如上所述,本发明的应用于存算一体电路的10晶体管sram存储单元结构,具有以下

21、有益效果:

22、相对于现有技术中的双6晶体管双字线sram存储单元的结构,本发明的10晶体管三字线sram存储单元,在同等功能下可节约20%的面积。

技术特征:

1.一种应用于存算一体电路的10晶体管sram存储单元结构,其特征在于,包括:

2.根据权利要求1所述的应用于存算一体电路的10晶体管sram存储单元结构,其特征在于:所述m7、m8一侧的电流为m9、m10一侧的电流的目标倍数。

3.根据权利要求2所述的应用于存算一体电路的10晶体管sram存储单元结构,其特征在于:所述m7、m8一侧的电流为m9、m10一侧的电流的2至3倍。

4.根据权利要求3所述的应用于存算一体电路的10晶体管sram存储单元结构,其特征在于:所述m7、m8栅极宽度为m9、m10栅极宽度的2至3倍。

5.根据权利要求1所述的应用于存算一体电路的10晶体管sram存储单元结构,其特征在于:所述m5和m3组成第一反相器,m6和m4组成第二反相器,第一反相器与第二反相器交叉耦接形成锁存电路。

技术总结

本发明提供一种应用于存算一体电路的10晶体管SRAM存储单元结构,包括:4个PMOS晶体管M1、M2、M5、M6和6个NMOS晶体管M3、M4、M7、M8、M9、M10;M5、M6的源极连接存储单元工作电源,M5、M6的漏极分别连接M3、M4的漏极;M5的栅极连接M3的栅极形成第一存储节点N1,M6的栅极连接M4的栅极形成第二存储节点N2;M3、M4的源极连接地线;M1的源极连接信号BL_W,漏极连接第一存储节点N1,栅极连接信号WL_W;M2的源极连接信号BLB_W,漏极连接第二存储节点N2,栅极连接信号WL_W;M7的源极连接地线,栅极连接第一存储节点N1,漏极连接M8的源极。相对于现有技术中的双6晶体管双字线SRAM存储单元的结构,本发明的10晶体管三字线SRAM存储单元,在同等功能下可节约20%的面积。

技术研发人员:陈蓓,范茂成

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!