非易失性可编程异质结存储器的制作方法

1.本发明涉及半导体技术领域,尤其涉及一种非易失性可编程异质结存储器。

背景技术:

2.物联网时代,海量数据的获取和处理对信息传输能力、信息处理速度和能耗等都造成了巨大压力,发展边缘计算和存储成为解决该问题的有效途径之一,其中研制感、存、算一体的新型智能传感器,实现器件内的信息获取、处理与存储,对提升系统的能效、降低信号延迟,满足万物互联时代日益增长的海量数据获取和处理需求具有重要意义。视觉是信息获取的主要来源之一,其主要核心部位之一为光电探测器。

3.传统光电探测器功能单一,只具有光电转换功能,无法面对海量信息时代对智能传感器提出的更高要求,因此,发展感、存、算一体的新原理低功耗光电探测器元器件具有重要意义。

4.因此,有必要提供一种新型的非易失性可编程异质结存储器以解决现有技术中存在的上述问题。

技术实现要素:

5.本发明的目的在于提供一种非易失性可编程异质结存储器,实现所述异质结沟道层在不同pn结和非pn结之间的连续逻辑变化和存储,降低光电测试的高,实现感、存、算功能的一体化。

6.为实现上述目的,本发明的所述非易失性可编程异质结存储器,依次包括:

7.控制栅层;

8.第一电介质层,覆盖所述控制栅层的顶面;

9.浮栅层,覆盖所述第一电介质层的顶面;

10.第二电介质层,覆盖所述浮栅层的顶面;

11.异质结沟道层,所述异质结沟道层包括第一半导体和第二半导体,所述第一半导体和所述第二半导体中至少一种为双极性半导体,所述第一半导体和所述第二半导体共同覆盖所述第二电介质层的顶面;以及

12.电极,覆盖所述异质结沟道层的部分顶面。

13.所述非易失性可编程异质结存储器的有益效果在于:所述异质结沟道层包括第一半导体和第二半导体,所述第一半导体和所述第二半导体中至少一种为双极性半导体,使得施加在所述控制栅层上的控制栅电压可以实现所述异质结沟道层在不同pn结和非pn结之间的连续逻辑变化和存储,并可以利用pn结的光伏模式,实现低功耗的光电测试,从而实现所述非易失性可编程异质结存储器的感、存、算功能的一体化。

14.优选地,所述电极包括源电极和漏电极,所述源电极覆盖所述第一半导体的部分顶面,所述漏电极覆盖所述第二半导体的部分顶面。

15.进一步优选地,所述源电极的材料为金或铬,所述漏电极的材料为金或铬。

16.优选地,所述双极性半导体的材料为二硒化钨。

17.优选地,所述第一电介质层的材料和所述第二电介质层的材料均为二氧化铪。

18.优选地,所述浮栅层的材料和所述控制栅层的材料均为金。

附图说明

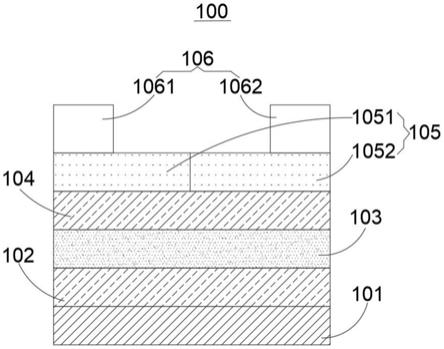

19.图1为本发明实施例的非易失性可编程异质结存储器的结构示意图;

20.图2为本发明实施例的非易失性可编程异质结存储器的功能曲线图。

具体实施方式

21.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。除非另外定义,此处使用的技术术语或者科学术语应当为本发明所属领域内具有一般技能的人士所理解的通常意义。本文中使用的“包括”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。

22.针对现有技术存在的问题,本发明的实施例提供了一种非易失性可编程异质结存储器。参照图1,所述非易失性可编程异质结存储器100依次包括控制栅层101、第一电介质层102、浮栅层103、第二电介质层104、异质结沟道层105和电极106,所述第一电介质层102覆盖所述控制栅层101的顶面,所述浮栅层103覆盖所述第一电介质层102的顶面,所述第二电介质104层覆盖所述浮栅层103的顶面,所述异质结沟道层105包括第一半导体1051和第二半导体1052,所述第一半导体1051和所述第二半导体1052中至少一种为双极性半导体,所述第一半导体1051和所述第二半导体1052共同覆盖所述第二电介质层104的顶面,所述电极覆盖所述异质结沟道层105的部分顶面。

23.所述非易失性可编程异质结存储器中所述异质结沟道层包括第一半导体和第二半导体,所述第一半导体和所述第二半导体中至少一种为双极性半导体,使得施加在所述控制栅层上的控制栅电压可以实现所述异质结沟道层在不同pn结和非pn结之间的连续逻辑变化和存储,并可以利用pn结的光伏模式,实现低功耗的光电测试,从而实现所述非易失性可编程异质结存储器的感、存、算功能的一体化,并且具有半导体工艺兼容性,具有大规模生产的潜力。

24.图2为本发明一些实施例中非易失性可编程异质结存储器的功能曲线图。参照图2,可以看出,在辐照所述非易失性可编程异质结存储器上的光功率为10nw时,施加在所述控制栅层上的控制栅电压v

cg

可以连续调制所述非易失性可编程异质结存储器所产生的光伏电压v

oc

,即使得所述非易失性可编程异质结存储器的光电探测能力得到连续调制,并具有存储功能。

25.参照图1,所述电极106包括源电极1061和漏电极1062,所述源电极1061覆盖所述第一半导体1051的部分顶面,所述漏电极1062覆盖所述第二半导体1052的部分顶面,其中,所述源电极1061的材料为金或铬,所述漏电极1062的材料为金(au)或铬(cr)。

26.一些实施中,所述双极性半导体的材料为二硒化钨(wse2),所述第一电介质层的

材料和所述第二电介质层的材料均为二氧化铪(hfo2),所述浮栅层的材料和所述控制栅层的材料均为金(au)。

27.虽然在上文中详细说明了本发明的实施方式,但是对于本领域的技术人员来说显而易见的是,能够对这些实施方式进行各种修改和变化。但是,应理解,这种修改和变化都属于权利要求书中所述的本发明的范围和精神之内。而且,在此说明的本发明可有其它的实施方式,并且可通过多种方式实施或实现。

技术特征:

1.一种非易失性可编程异质结存储器,其特征在于,依次包括:控制栅层;第一电介质层,覆盖所述控制栅层的顶面;浮栅层,覆盖所述第一电介质层的顶面;第二电介质层,覆盖所述浮栅层的顶面;异质结沟道层,所述异质结沟道层包括第一半导体和第二半导体,所述第一半导体和所述第二半导体中至少一种为双极性半导体,所述第一半导体和所述第二半导体共同覆盖所述第二电介质层的顶面;以及电极,覆盖所述异质结沟道层的部分顶面。2.根据权利要求1所述的非易失性可编程异质结存储器,其特征在于,所述电极包括源电极和漏电极,所述源电极覆盖所述第一半导体的部分顶面,所述漏电极覆盖所述第二半导体的部分顶面。3.根据权利要求2所述的非易失性可编程异质结存储器,其特征在于,所述源电极的材料为金或铬,所述漏电极的材料为金或铬。4.根据权利要求1所述的非易失性可编程异质结存储器,其特征在于,所述双极性半导体的材料为二硒化钨。5.根据权利要求1所述的非易失性可编程异质结存储器,其特征在于,所述第一电介质层的材料和所述第二电介质层的材料均为二氧化铪。6.根据权利要求1所述的非易失性可编程异质结存储器,其特征在于,所述浮栅层的材料和所述控制栅层的材料均为金。

技术总结

本发明提供了一种非易失性可编程异质结存储器,包括控制栅层、第一电介质层、浮栅层、第二电介质层、异质结沟道层和电极,所述第一电介质层覆盖所述控制栅层的顶面,所述浮栅层覆盖所述第一电介质层的顶面,所述第二电介质层设置于所述浮栅层的上侧,所述异质结沟道层包括第一半导体和第二半导体,所述第一半导体和所述第二半导体中至少一种为双极性半导体,所述第一半导体和所述第二半导体共同覆盖所述第二电介质层的顶面,所述电极覆盖所述异质结沟道层的部分顶面,使得施加在所述控制栅层上的控制栅电压可以实现所述异质结沟道层在不同PN结和非PN结之间的连续逻辑变化和存储,实现低功耗的光电测试,从而实现感、存、算功能的一体化。的一体化。的一体化。

技术研发人员:张增星 盛喆 余睿

受保护的技术使用者:上海集成电路制造创新中心有限公司

技术研发日:2021.07.29

技术公布日:2021/11/2

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1