高电子迁移率晶体管元件及其制造方法与流程

本发明涉及一种半导体元件及其制造方法,且特别是涉及一种高电子迁移率晶体管(high electron mobility transistor device,hemt)元件及其制造方法。

背景技术:

1、目前,在对高电子迁移率晶体管进行操作之后,负电荷会被捕捉在阻障层的表面,而产生电流崩塌(current collapse)现象。由于电流崩塌现象会增加高电子迁移率晶体管的沟道电阻,因此会降低高电子迁移率晶体管的跨导(transconductance,gm)。

技术实现思路

1、本发明提供一种高电子迁移率晶体管元件及其制造方法,其可提升高电子迁移率晶体管的跨导。

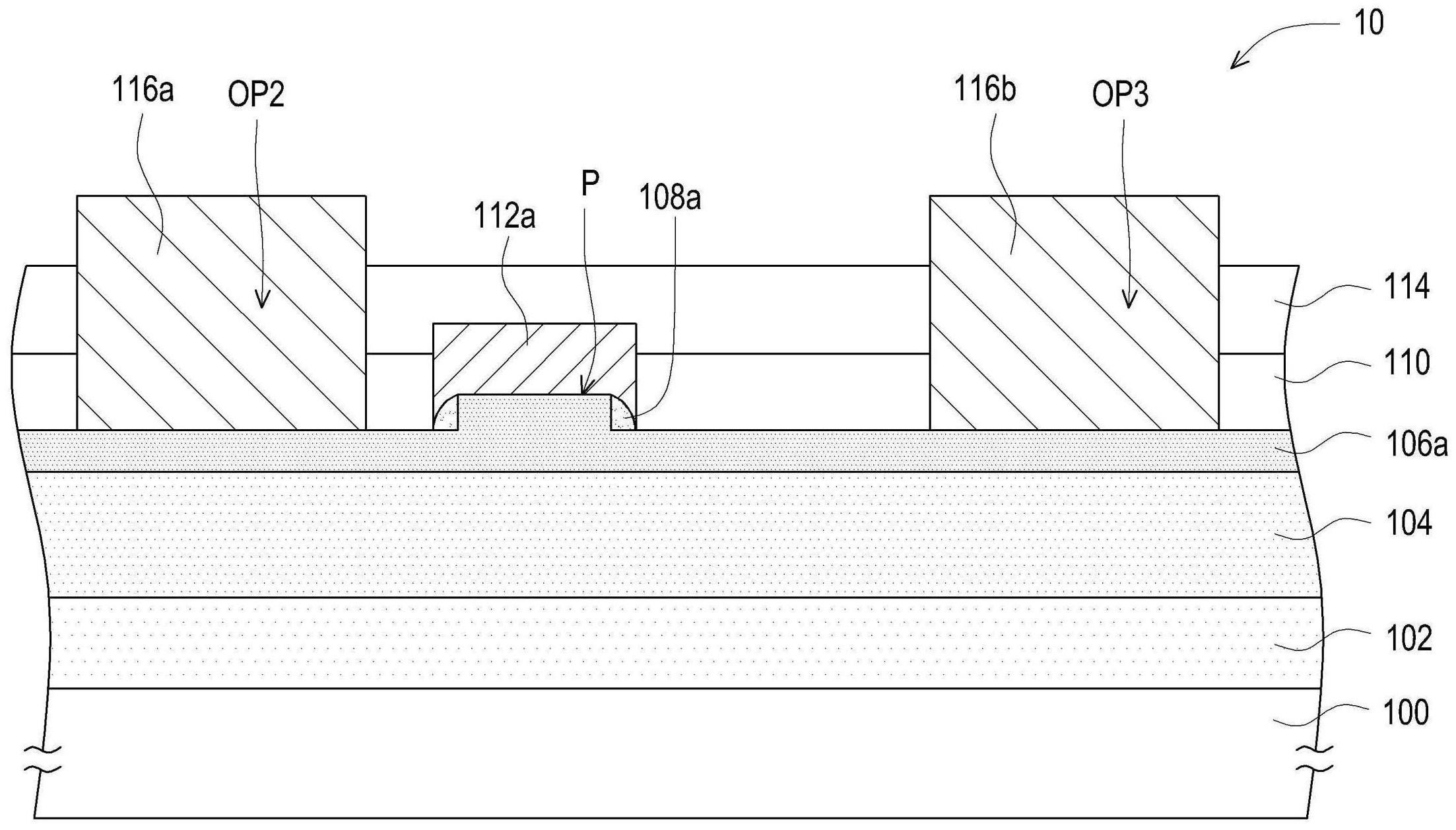

2、本发明提出一种高电子迁移率晶体管元件,包括基底、沟道层、阻障层、p型氮化镓间隙壁(p-type gan spacer)、栅极、源极与漏极。沟道层设置在基底上。阻障层设置在沟道层上,且具有突出部。p型氮化镓间隙壁设置在突出部的侧壁上。栅极设置在突出部与p型氮化镓间隙壁上。源极与漏极设置在栅极两侧。

3、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件中,栅极可直接接触突出部与p型氮化镓间隙壁。

4、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件中,p型氮化镓间隙壁可位于部分栅极与部分阻障层之间。

5、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件中,沟道层的材料例如是氮化镓(gan)。

6、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件中,阻障层的材料例如是氮化铝镓(algan)。

7、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件中,栅极的材料可不同于源极的材料与漏极的材料。

8、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件中,栅极的功函数(work function)可不同于源极的功函数与漏极的功函数。

9、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件中,更可包括缓冲层。缓冲层设置在沟道层与基底之间。

10、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件中,高电子迁移率晶体管元件例如是耗尽型高电子迁移率晶体管(depletion-mode(d-mode)hemt)元件。

11、本发明提出一种高电子迁移率晶体管元件的制造方法,包括以下步骤。提供基底。在基底上形成沟道层。在沟道层上形成阻障层,其中阻障层具有突出部。在突出部的侧壁上形成p型氮化镓间隙壁。在突出部与p型氮化镓间隙壁上形成栅极。在栅极两侧形成源极与漏极。

12、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,沟道层的形成方法例如是外延成长法(epitaxial growth method)。

13、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,阻障层的形成方法可包括以下步骤。形成阻障材料层。对阻障材料层进行图案化,而形成阻障层。

14、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,阻障材料层的形成方法例如是外延成长法。

15、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,p型氮化镓间隙壁的形成方法可包括以下步骤。形成p型氮化镓材料层。对p型氮化镓材料层进行回蚀刻制作工艺(etch-back process),而形成p型氮化镓间隙壁。

16、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,p型氮化镓材料层的形成方法例如是外延成长法。

17、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,回蚀刻制作工艺例如是干式蚀刻制作工艺。

18、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,栅极的形成方法可包括以下步骤。在阻障层与p型氮化镓间隙壁上形成第一介电层。在第一介电层中形成第一开口。第一开口可暴露出突出部与p型氮化镓间隙壁。在第一介电层上且在第一开口中形成第一导电层。对第一导电层进行图案化,而形成栅极。栅极可位于第一开口中。

19、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,源极与漏极的形成方法可包括以下步骤。在第一介电层与栅极上形成第二介电层。在第二介电层与第一介电层中形成第二开口与第三开口。在第二介电层上且在第二开口与第三开口中形成第二导电层。对第二导电层进行图案化,而形成源极与漏极。源极可位于第二开口中,且漏极可位于第三开口中。

20、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,还可包括以下步骤。在形成沟道层之前,在基底上形成缓冲层。

21、依照本发明的一实施例所述,在上述高电子迁移率晶体管元件的制造方法中,缓冲层的形成方法例如是外延成长法。

22、基于上述,在本发明所提出的高电子迁移率晶体管元件及其制造方法中,p型氮化镓间隙壁位于阻障层的突出部的侧壁上,且栅极位于突出部与p型氮化镓间隙壁上。因此,可通过在恢复时段(recovery time period)的恢复操作(recovery operation)来产生空穴注入(hole injection)的效果。如此一来,可利用空穴来中和(neutralize)或补偿(compensate)被捕捉在阻障层的表面上的负电荷,由此可解决电流崩塌的问题并且可提升高电子迁移率晶体管的跨导。

23、为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

技术特征:

1.一种高电子迁移率晶体管元件,包括:

2.如权利要求1所述的高电子迁移率晶体管元件,其中所述栅极直接接触所述突出部与所述p型氮化镓间隙壁。

3.如权利要求1所述的高电子迁移率晶体管元件,其中所述p型氮化镓间隙壁位于部分所述栅极与部分所述阻障层之间。

4.如权利要求1所述的高电子迁移率晶体管元件,其中所述沟道层的材料包括氮化镓。

5.如权利要求1所述的高电子迁移率晶体管元件,其中所述阻障层的材料包括氮化铝镓。

6.如权利要求1所述的高电子迁移率晶体管元件,其中所述栅极的材料不同于所述源极的材料与所述漏极的材料。

7.如权利要求1所述的高电子迁移率晶体管元件,其中所述栅极的功函数不同于所述源极的功函数与所述漏极的功函数。

8.如权利要求1所述的高电子迁移率晶体管元件,还包括:

9.如权利要求1所述的高电子迁移率晶体管元件,其中所述高电子迁移率晶体管元件包括耗尽型高电子迁移率晶体管元件。

10.一种高电子迁移率晶体管元件的制造方法,包括:

11.如权利要求10所述的高电子迁移率晶体管元件的制造方法,其中所述沟道层的形成方法包括外延成长法。

12.如权利要求10所述的高电子迁移率晶体管元件的制造方法,其中所述阻障层的形成方法包括:

13.如权利要求10所述的高电子迁移率晶体管元件的制造方法,其中所述阻障材料层的形成方法包括外延成长法。

14.如权利要求10所述的高电子迁移率晶体管元件的制造方法,其中所述p型氮化镓间隙壁的形成方法包括:

15.如权利要求14所述的高电子迁移率晶体管元件的制造方法,其中所述p型氮化镓材料层的形成方法包括外延成长法。

16.如权利要求14所述的高电子迁移率晶体管元件的制造方法,其中所述回蚀刻制作工艺包括干式蚀刻制作工艺。

17.如权利要求10所述的高电子迁移率晶体管元件的制造方法,其中所述栅极的形成方法包括:

18.如权利要求17所述的高电子迁移率晶体管元件的制造方法,其中所述源极与所述漏极的形成方法包括:

19.如权利要求10所述的高电子迁移率晶体管元件的制造方法,还包括:

20.如权利要求19所述的高电子迁移率晶体管元件的制造方法,其中所述缓冲层的形成方法包括外延成长法。

技术总结

本发明公开一种高电子迁移率晶体管元件及其制造方法,其中该高电子迁移率晶体管元件包括基底、沟道层、阻障层、P型氮化镓间隙壁、栅极、源极与漏极。沟道层设置在基底上。阻障层设置在沟道层上,且具有突出部。P型氮化镓间隙壁设置在突出部的侧壁上。栅极设置在突出部与P型氮化镓间隙壁上。源极与漏极设置在栅极两侧。

技术研发人员:李皞明,罗大刚,陈再富,谢守伟

受保护的技术使用者:联华电子股份有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!