高压金属栅极器件的制造方法与流程

本发明涉及半导体制造技术,特别是涉及一种高压金属栅极器件的制造方法。

背景技术:

1、从28nm节点向下,高性能工艺会采用hk(高介电常数)介质搭配金属栅极来提高器件性能,金属栅极工艺中不可避免需要使用金属的cmp(chemical mechanical polishing,化学机械抛光)工艺,金属cmp工艺中,大块图形不可避免会出现dishing(碟形下凹),所以栅极的尺寸不能设计得太大,但对高压器件(操作电压8v~40v)来说,不可避免的需要比较大的栅极尺寸来承担高电压操作,这样就会造成大块金属栅极中栅极高度的下降甚至缺失,具体包括以下步骤:

2、一.经过前序工艺,进行栅极光刻和刻蚀、侧墙工艺后,定义出伪多晶硅栅极(dummy poly gate),其中至少有一个伪多晶硅高压栅极2,伪多晶硅栅极的伪多晶硅(dummy polycrystalline)3形成在栅介质层8上,如图1所示;

3、二.在伪多晶硅栅极之间填充隔离介质4进行cmp(chemical mechanicalpolishing,化学机械抛光)工艺,如图2所示;

4、三.通过选择性刻蚀,去除伪多晶硅栅极的栅介质层8上的伪多晶硅3,如图3所示;

5、四.在晶圆上进行栅极金属5淀积,如图4所示;

6、五.进行栅极金属cmp(chemical mechanical polishing,化学机械抛光)。因为高压栅极2上的栅极金属5比较大,会造成cmp碟形下凹(dishing),导致高压栅极2上的栅极金属5的中间偏薄甚至空缺,如图5所示。

7、为了解决这个问题,目前比较通用的方法是在大面积的高压栅极中增加沟槽,具体工艺包括以下步骤:

8、(一)在伪多晶硅栅极(dummy poly gate)光刻和刻蚀时,通过光罩在高压栅极2上的大面积的伪多晶硅3中间挖出连通到栅介质层8的沟槽,如图6所示;

9、(二).在伪多晶硅栅极之间填充隔离介质4,进行cmp(chemical mechanicalpolishing,化学机械抛光)工艺;

10、(三).通过选择性刻蚀,去除高压栅极2上的伪多晶硅3;

11、(四).在晶圆上进行栅极金属5淀积;

12、(五).进行栅极金属cmp(chemical mechanical polishing,化学机械抛光)工艺。

13、在大面积的高压栅极2的伪多晶硅3中增加沟槽的方法,高压栅极2的大面积的伪多晶硅3中间因为有填充在沟槽中的隔离介质4阻挡,不会造成cmp碟形下凹(dishing)。但是,在高压栅极2的大面积的伪多晶硅3中增加沟槽的方法,如图6所示,由于高压栅极2的大面积的伪多晶硅3中的沟槽会把其下方的栅介质层8暴露出来,后续工艺包括离子注入、金属硅化物等工艺会在栅极介质层8中引入离子,同时蚀刻和酸洗也会影响暴露在外的栅极介质层8,高压器件的电性会受影响,造成高压器件电性在高压和高温下偏移,降低高压器件的可靠性。

技术实现思路

1、本发明要解决的技术问题是提供一种高压金属栅极器件的制造方法,不但不存在大块栅极金属的碟形下凹问题,同时也能避免因影响栅极介质层而导致影响高压器件的电性。

2、为解决上述技术问题,本发明提供的高压金属栅极器件的制造方法,其包括以下步骤:

3、s1.经过前序工艺,进行栅极光刻和刻蚀、侧墙工艺后,定义出伪多晶硅栅极,其中至少有一个伪多晶硅高压栅极2,伪多晶硅栅极的伪多晶硅3形成在栅介质层8上;

4、s2.在伪多晶硅栅极之间填充隔离介质4,进行cmp工艺;

5、s3.通过选择性刻蚀,去除伪多晶硅栅极的栅介质层8上的伪多晶硅;

6、s4.在晶圆上进行栅极金属5淀积;

7、s5.进行栅极金属cmp工艺,减小晶圆上淀积的栅极金属5的厚度;

8、s6.在栅极金属5上淀积一层阻挡介质层6;

9、s7.通过光刻打开高压栅极2区域,通过蚀刻把高压栅极2区域之外的阻挡介质层6去除;

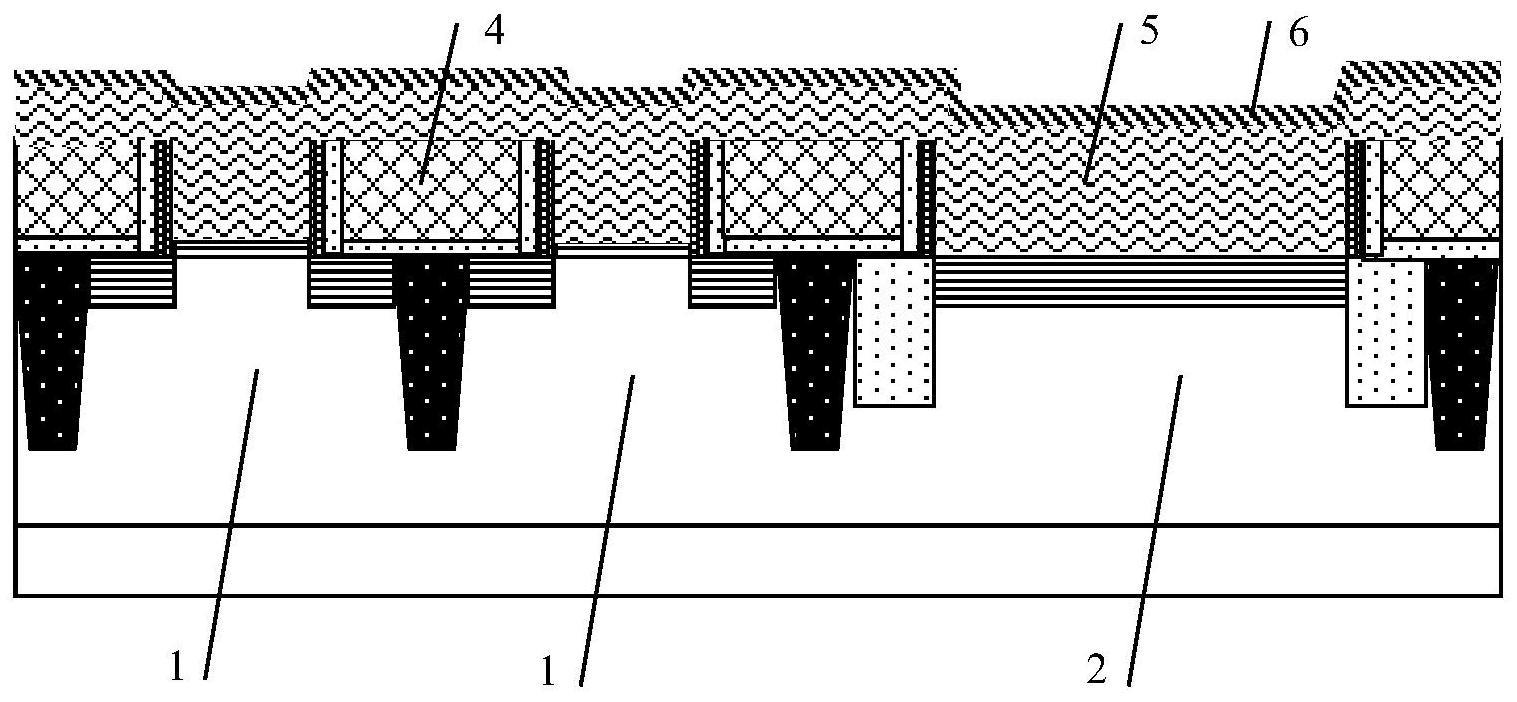

10、s8.进行栅极金属cmp工艺,减小晶圆上淀积的栅极金属5的厚度,由于覆盖的阻挡介质层6的阻挡,高压栅极2区域的栅极金属5会高于高压栅极2区域之外的栅极金属5;

11、s9.干刻或者酸洗,去除高压栅极2区域的栅极金属5上的阻挡介质层6。

12、较佳的,s9之后还进行s10,进行栅极金属cmp工艺,调整栅极金属5高度。

13、较佳的,s8中,进行栅极金属cmp工艺,去除高压栅极2区域之外的高于隔离介质4的栅极金属5,由于覆盖的阻挡介质层6的阻挡,高压栅极2区域上的栅极金属5会高于阻挡介质层6。

14、较佳的,s1中,定义出的伪多晶硅栅极,其中至少有一个伪多晶硅高压栅极2及一个伪多晶硅低压栅极1。

15、较佳的,高压栅极2的长度大于2.5μm。

16、较佳的,s4中,在晶圆上淀积的栅极金属5的厚度大于s2之后的栅极之间的隔离介质4的厚度。

17、较佳的,s4中,在晶圆上淀积的栅极金属5的厚度为30nm~200nm。

18、较佳的,s5中,进行栅极金属cmp工艺,减小晶圆上淀积的栅极金属5的厚度,并且栅极金属5上表面最低处高于栅极之间的隔离介质4。

19、较佳的,s5中,进行栅极金属cmp工艺,将晶圆上淀积的栅极金属5的厚度减少1/3~2/3。

20、较佳的,栅介质层8为sion、hfo2或sio2;

21、隔离介质4为sin或sio2;

22、阻挡介质层6为sin或sio2;

23、栅极金属5为al、ti或w。

24、本发明的高压金属栅极器件的制造方法,经过正常工艺的栅极金属5沉积之后,进行栅极金属5的cmp工艺时,先进行第一次cmp工艺将栅极金属5预先减薄到一定厚度,然后沉积一层阻挡介质层6,通过光刻打开大面积的高压栅极2区域,通过蚀刻把除大面积的高压栅极2区域之外的阻挡介质层6去除,在对栅极金属5进行第二次cmp工艺时,由于高压栅极2区域的大面积栅极金属5的表面有阻挡介质层6,研磨偏慢,不会造成cmp碟形下凹(dishing)。该高压金属栅极器件的制造方法,不但不存在大块栅极金属的碟形下凹(dishing)问题,同时也能避免因影响栅极介质层8而导致影响高压器件的电性。

技术特征:

1.一种高压金属栅极器件的制造方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的高压金属栅极器件的制造方法,其特征在于,

3.根据权利要求1所述的高压金属栅极器件的制造方法,其特征在于,

4.根据权利要求1所述的高压金属栅极器件的制造方法,其特征在于,

5.根据权利要求1所述的高压金属栅极器件的制造方法,其特征在于,

6.根据权利要求1所述的高压金属栅极器件的制造方法,其特征在于,

7.根据权利要求6所述的高压金属栅极器件的制造方法,其特征在于,

8.根据权利要求1所述的高压金属栅极器件的制造方法,其特征在于,

9.根据权利要求8所述的高压金属栅极器件的制造方法,其特征在于,

10.根据权利要求1所述的高压金属栅极器件的制造方法,其特征在于,

技术总结

本发明公开了一种高压金属栅极器件的制造方法,经过正常工艺的栅极金属沉积之后,进行栅极金属的CMP工艺时,先进行第一次CMP工艺将栅极金属预先减薄到一定厚度,然后沉积一层阻挡介质层,过光刻打开大面积的高压栅极区域,通过蚀刻把除大面积的高压栅极区域之外的阻挡介质层去除,在对栅极金属进行第二次CMP工艺时,由于高压栅极区域的大面积栅极金属的表面有阻挡介质层,研磨偏慢,不会造成CMP碟形下凹。该高压金属栅极器件的制造方法,不但不存在大块栅极金属的碟形下凹问题,同时也能避免因影响栅极介质层而导致影响高压器件的电性。

技术研发人员:唐小亮,陈昊瑜,邵华

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!