半导体结构及其形成方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、在电路设计中,出于安全、噪声控制、交互操作等方面的考虑,数字隔离器的使用是必不可少的。

2、当前的数字隔离器主要有三种隔离方式,即光电耦合、电磁耦合以及电容耦合。其中,采用电容耦合隔离方式的电容隔离器的主要结构是通过金属层为上下极板的平行板电容器,两极板间填充以二氧化硅为主要电介质的绝缘材料,因其体积小、集成度高、功耗低、通讯速度高等特点,在工业、医疗、汽车等领域得到越来越多的应用。

3、然而,现有技术中电容隔离器的性能仍有待提升。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构及其形成方法,提高半导体结构的性能。

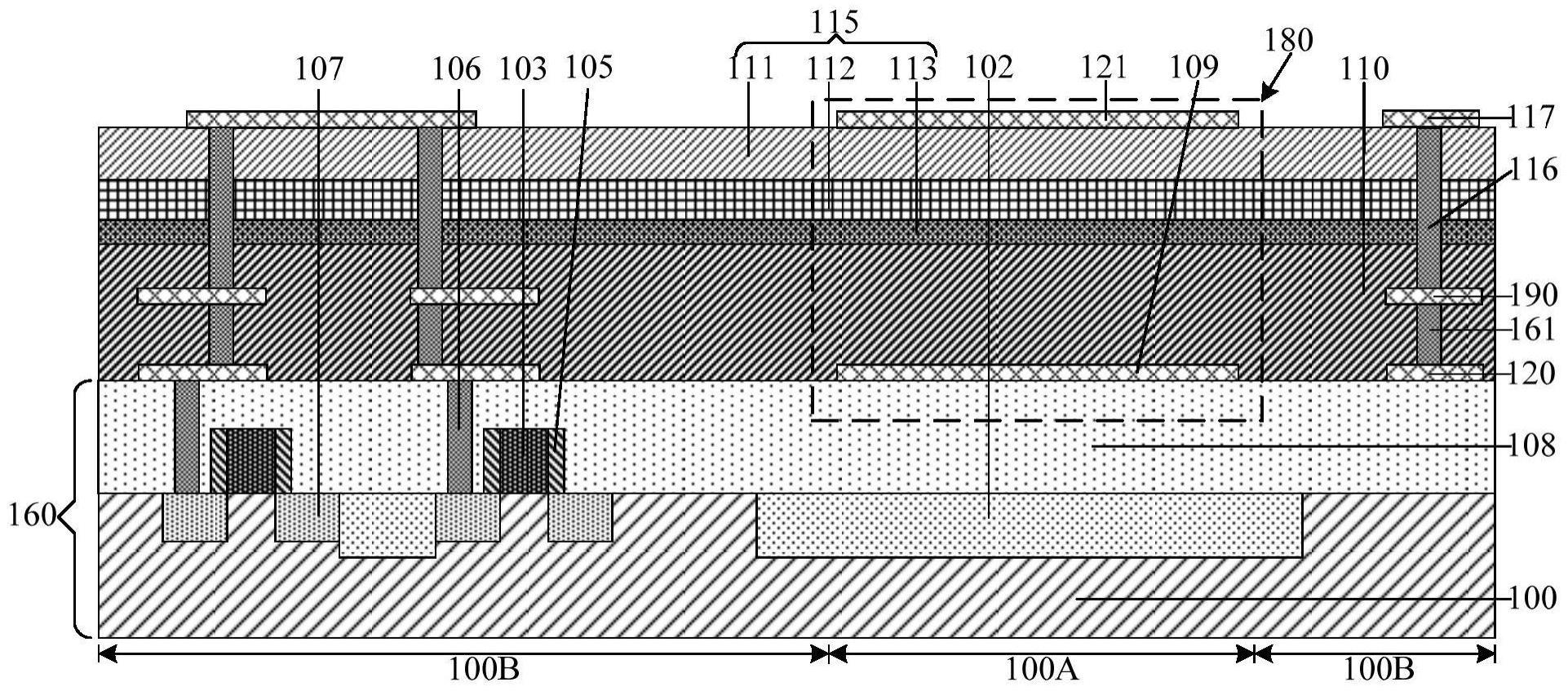

2、为解决上述问题,本发明实施例提供一种半导体结构,包括:基底层,所述基底层包括电容区和位于所述电容区侧部的器件区;逻辑器件结构,位于所述器件区的所述基底层的顶部且与所述基底层电连接;第一极板,位于所述电容区中,且位于所述基底层的顶部;绝缘层,位于所述基底层和第一极板的顶部,所述绝缘层包括叠层结构的主介电层和电场调节层,所述电场调节层的介电常数大于主介电层的介电常数;第二极板,位于所述电容区的所述绝缘层的顶部,且位于所述第一极板的顶部上方,所述第二极板、第一极板、以及位于所述第二极板和第一极板之间的绝缘层用于构成电容结构;其中,所述电场调节层位于所述主介电层和第二极板之间,或者,所述电场调节层位于所述主介电层和第一极板之间,或者,所述电场调节层分别位于所述主介电层和第一板机之间、以及位于所述主介电层和第二极板之间;钝化层,位于所述绝缘层的顶部,且露出所述第二互连层和第二极板。

3、相应的,本发明实施例还提供一种半导体结构的形成方法,包括:提供基底层,所述基底层包括电容区;在所述电容区中,在所述基底层的顶部形成第一极板;在所述基底层的顶部和第一极板的顶部形成绝缘层,所述绝缘层包括叠层结构的主介电层和电场调节层,所述电场调节层的介电常数大于所述主介电层的介电常数,其中,所述电场调节层位于所述主介电层和第一极板之间,或者,所述电场调节层位于所述主介电层的顶部,或者,所述电场调节层分别位于所述主介电层和第一极板之间、以及所述主介电层的顶部;形成所述绝缘层之后,在所述电容区的所述绝缘层的顶部形成第二极板,所述第二极板位于所述第一极板的顶部上方,所述第二极板、第一极板、以及位于所述第二极板和第一极板之间的绝缘层用于构成电容结构。

4、与现有技术相比,本发明实施例的技术方案具有以下优点:

5、本发明实施例提供一种半导体结构的形成方法,在第一极板和第二极板之间形成绝缘层,绝缘层包括叠层结构的主介电层和电场调节层,电场调节层的介电常数大于主介电层的介电常数,由于电场调节层位于主介电层和第二极板之间,或者,电场调节层位于主介电层和第一极板之间,或者,电场调节层位于主介电层和第一极板之间、以及位于主介电层和第二极板之间,根据静电场的高斯定理,在电场调节层的介电常数大于主介电层的介电常数情况下,且电场调节层离第一极板或第二极板的距离越近,第一极板和第二极板的四周的电场强度也就越弱,相应的,也就显著降低了第一极板和第二极板发射出的电子数量和发射速度,提高了第一极板和第二极板之间抗击穿能力,从而提高了半导体结构的性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述电场调节层包括多层子调节层;

3.如权利要求2所述的半导体结构,其特征在于,所述电场调节层包含的所述子调节层的层数为1层至6层。

4.如权利要求2所述的半导体结构,其特征在于,所述子调节层包括堆叠的第一子调节层、第二子调节层和第三子调节层,且所述第一子调节层、第二子调节层和第三子调节层的介电常数依次递增;

5.如权利要求1所述的半导体结构,其特征在于,所述电场调节层的介电常数为4至10。

6.如权利要求1所述的半导体结构,其特征在于,所述主介电层的厚度为3um至40um。

7.如权利要求1所述的半导体结构,其特征在于,所述电场调节层的厚度为0.5um至8um。

8.如权利要求1所述的半导体结构,其特征在于,所述电场调节层的材料包括氮、硅、碳和氧中的至少两种元素。

9.如权利要求1所述的半导体结构,其特征在于,所述主介电层的材料包括sio2。

10.如权利要求1所述的半导体结构,其特征在于,所述第一极板的材料包括al、cu或者cu和al的合金,所述第二极板的材料包括al、cu或者cu和al的合金。

11.如权利要求1所述的半导体结构,其特征在于,逻辑器件结构包括在纵向上相间隔的第一互连层和第二互连层,所述第一互连层和第二互连层之间实现电连接,所述第一互连层最靠近所述基底层顶部且被所述绝缘层覆盖,所述第二互连层位于所述绝缘层的顶部;

12.如权利要求10所述的半导体结构,其特征在于,所述电场调节层全面覆盖所述基底层;或者所述电场调节层仅覆盖位于所述电容区的所述基底层。

13.一种半导体结构的形成方法,其特征在于,包括:

14.如权利要求13所述的半导体结构的形成方法,其特征在于,在所述基底层的顶部和第一极板的顶部形成绝缘层的步骤中,所述电场调节层包括多层子调节层;

15.如权利要求14所述的半导体结构的形成方法,其特征在于,采用沉积工艺形成所述电场调节层,且在同一沉积设备中,通过原位切换每一层所述子调节层对应的沉积参数,依次形成所述多层子调节层。

16.如权利要求13所述的半导体结构的形成方法,其特征在于,所述电场调节层的介电常数为4至10。

17.如权利要求13所述的半导体结构的形成方法,其特征在于,所述电场调节层的材料包括氮、硅、碳和氧中的至少两种元素。

18.如权利要求13所述的半导体结构的形成方法,其特征在于,形成所述电场调节层的工艺包括化学气相沉积工艺或旋涂工艺。

19.如权利要求13所述的半导体结构的形成方法,其特征在于,提供基底层的步骤中,所述基底层为前端器件层,所述基底还包括位于所述电容区侧部的器件区;

技术总结

一种半导体结构及其形成方法,方法包括:提供基底层,基底层包括电容区;在电容区中,在基底层的顶部形成第一极板;在基底层的顶部和第一极板的顶部形成绝缘层,绝缘层包括叠层结构的主介电层和电场调节层,电场调节层的介电常数大于主介电层的介电常数,其中,电场调节层位于主介电层和第一极板之间,或者,电场调节层位于主介电层的顶部,或者,电场调节层分别位于主介电层和第一极板之间、以及主介电层的顶部;在电容区的绝缘层的顶部形成第二极板,第二极板位于第一极板的顶部上方,第二极板、第一极板、以及位于第二极板和第一极板之间的绝缘层用于构成电容结构。提高第一极板和第二极板之间抗击穿能力,提高半导体结构的性能。

技术研发人员:丁亚,王劲松,杨林宏,张艳红,杜义琛,陈秋颖

受保护的技术使用者:中芯国际集成电路制造(天津)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!