碲基半导体器件的制造方法、由此制造的碲基半导体器件以及薄膜晶体管

本发明涉及一种碲基半导体器件的制造方法、由此制造的碲基半导体器件以及包含其的薄膜晶体管,更详细而言,涉及一种通过实用性工艺制造电特性优异的p型碲基半导体器件的方法、通过所述方法制造的碲基半导体器件、以及包括所述碲基半导体器件的薄膜晶体管。

背景技术:

1、晶体管(transistor)是一种利用半导体放大或切换电子信号和功率的器件,广泛应用于显示器、扬声器等各种电子设备中。用于这些晶体管的半导体,通过单元器件的小型化实现了集成度的提高,但随着半导体的技术节点发展到10nm波段,小型化已经达到了技术极限。因此,作为克服这些极限的技术,已经提出了所谓的三维半导体技术,其通过将二维半导体层叠多层来实现三维形式,从而,可以提高半导体的集成度。

2、然而,作为最常用的半导体材料的硅基半导体,由于在制造过程中需要高温热处理,因此,存在难以在耐热性低的基板上形成,并且难以应用于三维半导体技术的缺点。此外,存在电场迁移率低的局限。因此,正在开发各种替代材料来弥补这些硅基半导体的缺点。

3、作为硅基半导体的替代方案之一,使用氧化物半导体,例如氧化锌(zno)、氧化铟锌(indium zinc oxide,izo)、氧化铟镓锌(indium gallium zinc oxide,igzo)等。这种氧化物半导体,由于可以在比硅基半导体更低的温度下制造,因此,可以应用于三维半导体技术的实现,而且,由于可见光透射率高而适合用于透明电子器件,因此,具有能带隙和电场迁移率高的优点。但是,这种氧化物半导体,主要具有n型半导体的特性,因此作为p型半导体使用时,存在难以获得均匀的质量,电场迁移率及开关电流比等的电特性差的问题。

4、例如,韩国专利公开第10-2015-0108168号公报公开了一种p型氧化物半导体,其中在cus及sno、ito、izto、igzo、izo等附加结合ga,所述p型氧化物半导体可通过溶液工艺容易制造,并且可以实现具有高迁移率的高性能薄膜晶体管。但是,由于此技术采用了溶液工艺,因此,存在半导体生产线亲和力降低的问题,并且,为了提高薄膜晶体管的迁移率,需要在300℃以上的高温进行热处理的工艺,所以,在三维半导体技术的应用上受限制。

5、作为替代方案,正在研究将碲用作p型半导体的材料。碲(tellurium,te)是一种准金属元素,原子序数为52,电子排布为4d105s25p4,晶体呈六方晶系(hexagonal)结构。虽然碲在带隙能量和空穴迁移率高的方面具有优异的特性,但存在难以进行大面积沉积,在应用于晶体管时,缺乏开关特性的问题。为了克服这种问题,在文件[chunsong zhao et al.,nature nanotechnology,volume 15,pages 53-58(2020)]中,作为在硅集成电路、玻璃及塑胶等各种基板上沉积超薄型碲薄膜的技术,公开了使用热蒸发的方法。然而,此技术,由于在-80℃的极低温度下沉积碲薄膜,因此,实用性降低。

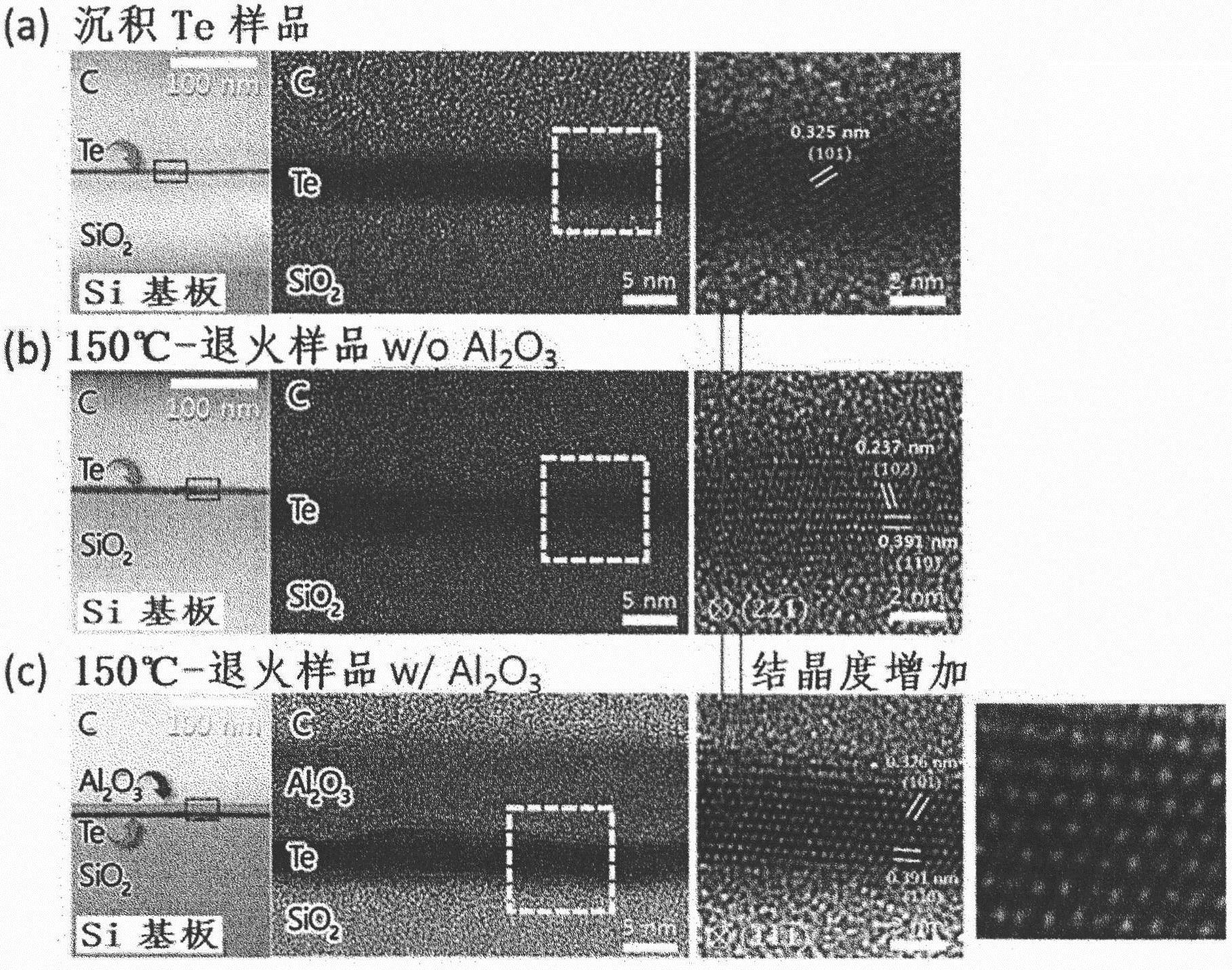

6、鉴于此,本发明的发明人发现通过在基板上沉积包括碲和氧化碲的碲基半导体材料之后,在上部沉积钝化层的方法,在无需进行高温热处理的情况下,可通过实用性工艺制造电特性优异的p型半导体,从而,完成了本发明。

技术实现思路

1、本发明的目的在于,提供一种可以制造结晶度高、电特性优异的p型碲基半导体器件的方法。

2、本发明的其他目的在于,提供一种通过上述方法制造的碲基半导体器件。

3、本发明的其他另一目的在于,提供一种包括所述碲基半导体器件的薄膜晶体管。

4、为了达成所述目的,本发明提供一种碲基半导体器件的制造方法,其中,包括:(i)准备基板的步骤;(ii)在所述基板上沉积包括碲和氧化碲中的至少一种的碲基半导体层的步骤;以及(iii)在所述碲基半导体层上形成钝化层的步骤。

5、本发明的方法,在所述基板上还可以包括绝缘层。

6、在本发明中,所述碲基半导体层可以含有te及teo2。

7、在本发明中,所述碲基半导体层,还可以以掺杂或合金的形式包含选自由sn、al、sb、hf、la、y、zr及zn组成的组中的至少一种金属。

8、在本发明中,所述碲基半导体层的沉积,可以通过溅射、化学气相沉积、热真空沉积、电子束沉积或原子层沉积而执行。

9、在本发明中,优选地,所述碲基半导体层的沉积可以在5至15%的氧分压条件下执行。

10、在本发明中,优选地,所述碲基半导体层的厚度为2至7nm。

11、本发明的制造方法,还可以包括在所述步骤(ii)之后,在100至200℃的温度下进行热处理的步骤。

12、在本发明中,优选地,所述钝化层包括选自由al2o3、hfo2、zro2、ta2o5、la2o3、y2o3、alhfox、hfzrox及alzrox组成的组中的至少一种。

13、在本发明中,优选地,所述钝化层的形成可以通过原子层沉积、化学气相沉积、热真空沉积、溅射或电子束沉积而执行。

14、在本发明中,优选地,所述钝化层的形成在100至200℃的温度下执行。

15、在本发明中,优选地,所述钝化层的厚度为1至30nm。

16、本发明还提供一种碲基半导体器件,其中,由上述的制造方法而制造,包括:基板;碲基半导体层,位于所述基板上;以及钝化层,位于所述碲基半导体层上。

17、在本发明的碲基半导体器件中,所述碲基半导体层以80∶20至90∶10的原子比包含te及te4+。

18、本发明提供一种薄膜晶体管,其包含上述的碲基半导体器件。

19、发明效果

20、根据本发明的制造方法,可以通过不需要高温热处理或极低温条件的实用性工艺,制造电特性优异的碲基p型半导体器件。另外,由于在制造过程中,碲基半导体层的结晶度得以提高,因此,可以提供具有优异的电场迁移率、开关电流比等电特性的p型半导体器件及薄膜晶体管。

技术特征:

1.一种碲基半导体器件的制造方法,其特征在于,包括:

2.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,在所述基板上还包括绝缘层。

3.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,所述碲基半导体层含有te及teo2。

4.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,所述碲基半导体层以掺杂或合金的形式还包括选自由sn、al、sb、hf、la、y、zr及zn组成的组中的至少一种金属。

5.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,所述碲基半导体层的沉积通过溅射、化学气相沉积、热真空沉积、电子束沉积或原子层沉积而执行。

6.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,所述碲基半导体层的沉积在5至15%的氧分压条件下执行。

7.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,所述碲基半导体层的厚度为2至7nm。

8.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,还包括在所述步骤(ii)之后,在100至200℃的温度下进行热处理的步骤。

9.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,所述钝化层包括选自由al2o3、hfo2、zro2、ta2o5、la2o3、y2o3、alhfox、hfzrox及alzrox组成的组中的至少一种。

10.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,所述钝化层的形成通过原子层沉积、化学气相沉积、热真空沉积、溅射或电子束沉积而执行。

11.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,所述钝化层的形成在100至200℃的温度下执行。

12.根据权利要求1所述的碲基半导体器件的制造方法,其特征在于,所述钝化层的厚度为1至30nm。

13.一种碲基半导体器件,其特征在于,由权利要求1至12中任一项所述的制造方法而制造,包括:

14.根据权利要求13所述的碲基半导体器件,其特征在于,所述碲基半导体层以80∶20至90∶10的原子比包含te及te4+。

15.一种薄膜晶体管,其特征在于,其包含权利要求13所述的碲基半导体器件。

技术总结

本发明涉及一种碲基半导体器件的制造方法,本发明的制造方法,包括:准备基板的步骤;在所述基板上沉积包括碲和氧化碲的碲基半导体材料,来形成碲基半导体层的步骤;以及在所述碲基半导体层上形成钝化层的步骤。根据本发明的制造方法,由于不需要高温热处理或极低温条件,因此,可以通过实用性工艺制造半导体器件。此外,由于在制造过程中,碲基半导体层的结晶度得以提高,因此,可以提供电场迁移率和开关电流比等的电特性优异的p型半导体器件。

技术研发人员:郑在景,金兑圭

受保护的技术使用者:汉阳大学校产学协力团

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!