元件封装以及半导体装置的制作方法

本说明书中的公开内容涉及元件封装以及具备该元件封装的半导体装置。

背景技术:

1、专利文献1公开了具备半导体元件、再布线层和密封树脂体的元件封装。现有技术文献的记载内容作为本说明书中的技术要素的说明通过参照而被引用。

2、现有技术文献

3、专利文献

4、专利文献1:日本特开2020-77743号公报

技术实现思路

1、功率元件等半导体元件在半导体衬底的一面侧具有主电极和焊盘。主电极及焊盘以能够实现与再布线层的连接的方式从配置在一面上的保护膜的开口部露出。保护膜没有配置在半导体元件的划线区域。根据专利文献1,必须在保护膜的上表面与半导体衬底的一面中的划线区域之间的阶差构造部形成再布线层。根据上述的观点或者没有提及的其他观点,对于元件封装要求进一步的改良。

2、本公开鉴于这样的课题,目的在于提供能够使再布线层的平坦性提高的元件封装以及半导体装置。

3、这里公开的元件封装,具备:半导体元件,具备:半导体衬底,具有形成元件的元件区域和设在距衬底端部为规定的范围内且包围元件区域的划线区域;主电极及焊盘,形成在半导体衬底的一面上;以及保护膜,以露出主电极及焊盘的方式配置在一面中的元件区域上;密封树脂体,以露出主电极及焊盘的方式将半导体元件密封;再布线层,具有绝缘体和配置于绝缘体的布线,相对于半导体元件配置在一面侧;以及绝缘部,以具有不超过元件区域上的保护膜的上表面的外周侧缘部的高度的方式在半导体元件的一面中配置在划线区域上;再布线层配置在保护膜到绝缘部的范围中。

4、根据公开的元件封装,绝缘部配置在划线区域上。绝缘部具有不超过保护膜的上表面的外周侧缘部的高度。并且,再布线层配置在保护膜到绝缘部的范围中。因而,与不配置绝缘部的结构相比,能够提高再布线层的平坦性。

5、这里公开的另一元件封装,具备:半导体元件,具备:半导体衬底,具有形成元件的元件区域和设在距衬底端部为规定的范围内且包围元件区域的划线区域;以及主电极及焊盘,形成在半导体衬底的一面上;密封树脂体,以露出主电极及焊盘的方式将半导体元件密封;以及再布线层,具有绝缘体和配置于绝缘体的布线,相对于半导体元件配置在一面侧;绝缘体在元件区域到划线区域的范围中与半导体衬底的一面接触。

6、根据公开的元件封装,再布线层的绝缘体在元件区域到划线区域的范围中与半导体衬底的一面接触。即,从半导体元件将保护膜排除。因而,能够提高再布线层的平坦性。

7、这里公开的半导体装置,具备元件封装、散热部件以及信号端子;元件封装具备:半导体元件,具备:半导体衬底,具有形成元件的元件区域和设在距衬底端部为规定的范围内且包围元件区域的划线区域;主电极及焊盘,形成在半导体衬底的一面上;以及保护膜,以露出主电极及焊盘的方式配置在一面中的元件区域上;密封树脂体,以露出主电极及焊盘的方式将半导体元件密封;再布线层,具有绝缘体和配置于绝缘体的布线,相对于半导体元件配置在一面侧;以及绝缘部,以具有不超过元件区域上的保护膜的上表面的外周侧缘部的高度的方式在半导体元件的一面中配置在划线区域上;再布线层配置在保护膜到绝缘部的范围中;布线具有与焊盘连接的信号布线;信号布线在半导体衬底的板厚方向上的平面视图中跨元件区域与划线区域的边界而延伸设置;散热部件在板厚方向上夹着半导体元件而配置;信号端子与信号布线中从绝缘体露出的端子部接合,经由信号布线而与对应的焊盘电连接。

8、根据公开的半导体装置,绝缘部配置在划线区域上。绝缘部具有不超过保护膜的上表面的外周侧缘部的高度。并且,再布线层配置在保护膜到绝缘部的范围中。因而,与不配置绝缘部的结构相比,能够提高再布线层的平坦性。此外,通过平坦性的提高,在边界的正上方周边能够抑制信号布线的厚度变薄或者断线。能够将键合线排除而简化连接构造,并且提高焊盘与信号端子的电连接可靠性。

9、这里公开的另一半导体装置,具备元件封装、散热部件以及信号端子;元件封装具备:半导体元件,具备:半导体衬底,具有形成元件的元件区域和设在距衬底端部为规定的范围内且包围元件区域的划线区域;以及主电极及焊盘,形成在半导体衬底的一面上;密封树脂体,以露出主电极及焊盘的方式将半导体元件密封;以及再布线层,具有绝缘体和配置于绝缘体的布线,相对于半导体元件配置在一面侧;绝缘体在元件区域到划线区域的范围中与半导体衬底的一面接触;布线具有与焊盘连接的信号布线,信号布线在半导体衬底的板厚方向上的平面视图中跨元件区域与划线区域的边界而延伸设置;散热部件在板厚方向上夹着半导体元件而配置;信号端子与信号布线中从绝缘体露出的端子部接合,经由信号布线而与对应的焊盘电连接。

10、根据公开的半导体装置,再布线层的绝缘体在元件区域到划线区域的范围中与半导体衬底的一面接触。即,从半导体元件将保护膜排除。因而,能够提高再布线层的平坦性。此外,通过平坦性的提高,能够在边界的正上方周边抑制信号布线的厚度变薄或者断线。能够将键合线排除而简化连接构造,并且提高焊盘与信号端子的电连接可靠性。

11、本说明书所公开的多个形态为了达成各自的目的而采用互不相同的技术手段。权利要求及其项目中记载的括号内的标记例示性地表示与后述的实施方式的部分的对应关系,并不意欲限定技术范围。本说明书所公开的目的、特征及效果通过参照后续的详细说明以及附图会更加明确。

技术特征:

1.一种元件封装,其特征在于,

2.如权利要求1所述的元件封装,其特征在于,

3.如权利要求1或2所述的元件封装,其特征在于,

4.如权利要求3所述的元件封装,其特征在于,

5.如权利要求3或4所述的元件封装,其特征在于,

6.如权利要求1或2所述的元件封装,其特征在于,

7.如权利要求1或2所述的元件封装,其特征在于,

8.一种元件封装,其特征在于,

9.如权利要求1~8中任一项所述的元件封装,其特征在于,

10.如权利要求1~9中任一项所述的元件封装,其特征在于,

11.一种半导体装置,其特征在于,

12.一种半导体装置,其特征在于,

技术总结

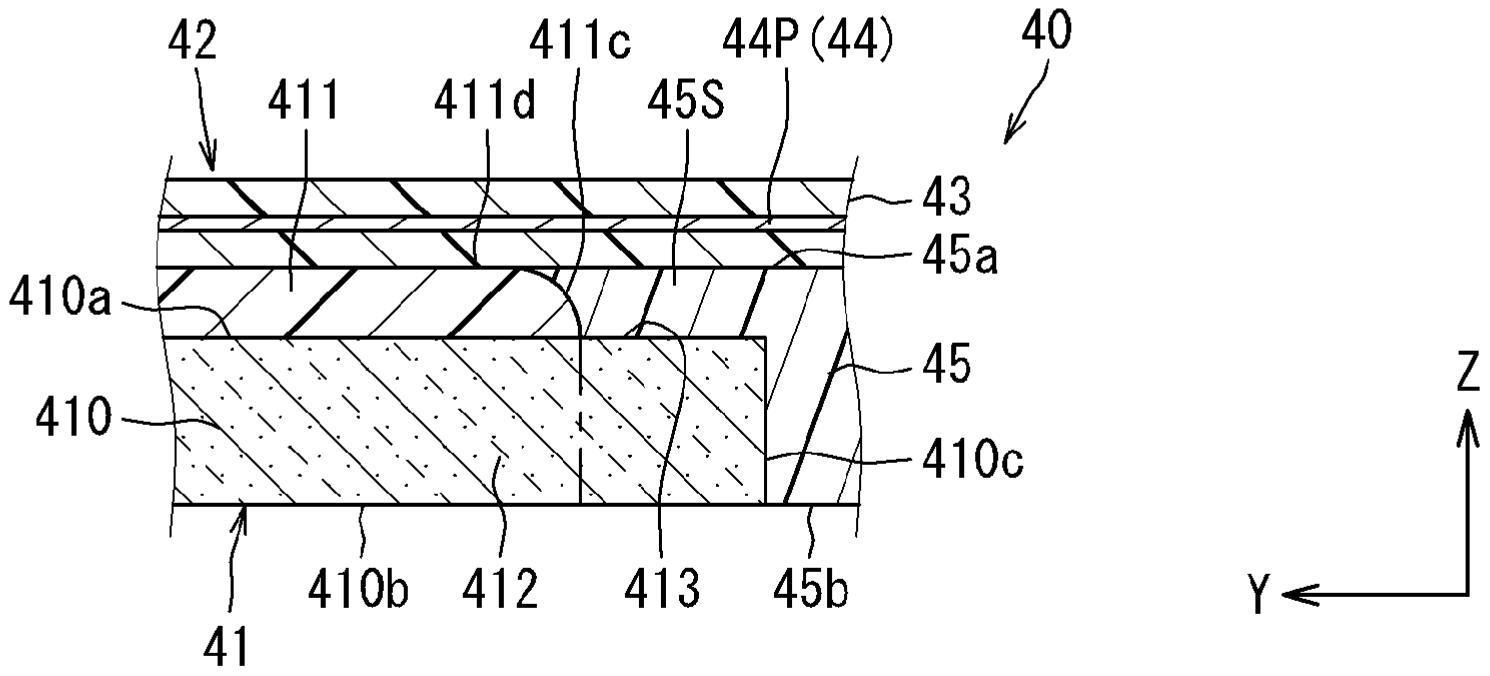

元件封装(40)具备半导体元件(41)、再布线层(42)以及密封树脂体(45)。半导体元件(41)具备:半导体衬底(410),具有元件区域(412)及划线区域(413);源极电极及焊盘,形成在半导体衬底的一面(410a);以及保护膜(411),配置在一面中的元件区域上。密封树脂体包含以具有不超过保护膜的上表面的缘部(411d)的高度的方式配置在划线区域(413)的一面上的密封树脂体(45S)。再布线层配置在保护膜到划线区域上的密封树脂体的范围中。

技术研发人员:犬塚仁浩,中野贵博,竹中正幸,水野直仁,大泽青吾,大仓康嗣

受保护的技术使用者:株式会社电装

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!