包括具有高分辨率矩形截面互连件的衬底的封装件的制作方法

各种特征涉及包括集成器件的封装件,但是更具体地涉及包括集成器件和具有基本矩形截面的互连件的衬底的封装件,并且涉及用于制造这种封装件的工艺。

背景技术:

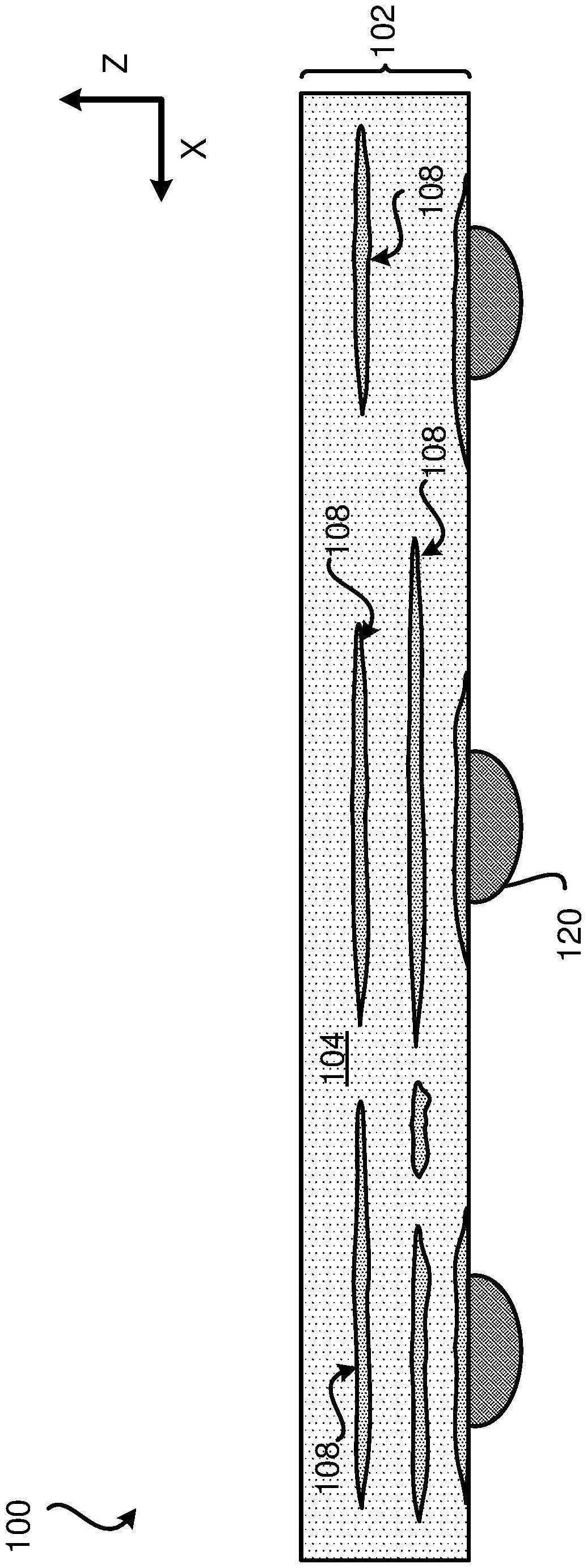

1、图1图示了包括衬底102和多个焊料互连件120的封装件100。衬底102包括至少一个电介质层104和多个大体上水平的互连件108(仅利用附图标记来具体标识互连件108中的一些互连件)。虽然未被示出,但是该封装件可以附加地包括将各种互连件108互连的垂直过孔。

2、图1的互连件108具有粗糙或不平坦的截面,这是由于实际的厚膜浆料制造程序中的限制造成的。即,尽管初始封装件的设计规则可能指定了精确的矩形截面,但是所得到的制造后互连件(当在陶瓷电介质中制造时)是长椭圆透镜形状,或者可能具有其他非矩形形状。例如,当前的丝网印刷制造程序可以产生图1中所示类型的制造后互连件。因此,尽管制造工艺的目的可能是形成具有精确矩形侧截面(side cross-section)(或其他精确的截面形状)的互连件,但是实际得到的互连件通常具有仅粗略地近似于预期形状的侧截面形状。

3、注意,封装衬底的技术图通常显示具有尖锐且精确的矩形截面的互连件。这样做可能是为了绘图方便,但是这种图通常无法准确地捕捉使用厚膜丝网印刷制造工艺形成的互连件和其他结构的实际制造形状。实际得到的制造形状通常与规定设计的理想期望形状大不相同。

4、在衬底内的电互连件的情况下,与具有矩形截面的互连件相比,由于集肤效应,所得到的互连件的粗糙的、长椭圆形或透镜形截面会引起射频(rf)性能的损失。此外,在线/宽度分辨率或准确性方面,丝网印刷制造工艺中的实际限制会限制所制造的互连件的分辨率。此外,使用丝网印刷工艺制造的平面互连件中的切口(例如针孔状开口)往往会由于表面张力而闭合,从而使性能降级。

5、持续需要提供包括具有侧截面矩形设计的形状的互连件的封装件和衬底,以及提供用于形成这种封装件和衬底的制造工艺。

技术实现思路

1、各种特征涉及封装件或衬底,但更具体地涉及包括具有矩形侧截面的互连件的衬底的封装件。

2、一个示例提供了一种封装件,封装件包括集成器件和耦合到集成器件的衬底。衬底包括至少一个电介质层和位于至少一个电介质层中的多个互连件,其中至少一个互连件具有沿该互连件的长度变化不超过3微米的截面厚度。

3、另一个示例提供了一种衬底,衬底包括至少一个电介质层和位于至少一个电介质层中的多个互连件,其中至少一个互连件具有在大约1微米-3微米的范围内的表面粗糙度。

4、另一个示例提供了一种制造衬底的方法。方法形成至少一个电介质层。方法在至少一个电介质层中或在至少一个电介质层之上形成多个互连件,其中至少一个互连件具有在大约1微米-3微米的范围内的表面粗糙度。

技术特征:

1.一种封装件,包括:

2.根据权利要求1所述的封装件,其中所述至少一个互连件具有在大约1微米-3微米的范围内的表面粗糙度。

3.根据权利要求1所述的封装件,其中所述至少一个互连件具有侧截面,所述侧截面具有拐角半径在大约0.5微米-2微米的范围内的至少一个拐角。

4.根据权利要求1所述的封装件,其中所述至少一个互连件的侧截面具有有效形状,所述有效形状为矩形、方形或椭圆形中的一者或多者。

5.权利要求1所述的封装件,

6.根据权利要求1所述的封装件,其中所述至少一个互连件具有大约1:2或更小的高度与宽度纵横比。

7.根据权利要求1所述的封装件,其中所述至少一个电介质层包括陶瓷、低温共烧陶瓷(ltcc)、高温共烧陶瓷(htcc)、氮化铝(aln)、氧化锌(zno)、氧化锆(zro2)和/或其组合。

8.根据权利要求1所述的封装件,其中所述至少一个互连件包括银(ag)、金(au)、钼(mo)、钨(w)、铂(pt)、钯(pd)、三氧化二钌(ru2o3)和/或其组合。

9.根据权利要求1所述的封装件,其中所述集成器件包括射频(rf)器件、模拟器件、无源器件、滤波器、电容器、电感器、天线、发射器、接收器、表面声波(saw)滤波器、体声波(baw)滤波器、发光二极管(led)集成器件、硅(si)基集成器件、碳化硅(sic)基集成器件、gaas基集成器件、gan基集成器件、存储器、电源管理处理器和/或其组合。

10.一种衬底,包括:

11.根据权利要求10所述的衬底,其中所述至少一个互连件具有沿该互连件的长度变化不超过3微米的截面厚度。

12.根据权利要求10所述的衬底,其中所述至少一个互连件具有侧截面,所述侧截面具有拐角半径在大约0.5微米-2微米的范围内的至少一个拐角。

13.根据权利要求10所述的衬底,其中所述至少一个互连件的侧截面具有有效形状,所述有效形状为矩形、方形或椭圆形中的一者或多者。

14.根据权利要求10所述的衬底,

15.根据权利要求10所述的衬底,其中所述至少一个互连件具有大约1:2或更小的高度与宽度纵横比。

16.根据权利要求10所述的衬底,其中所述至少一个电介质层包括陶瓷、低温共烧陶瓷(ltcc)、高温共烧陶瓷(htcc)、氮化铝(aln)、氧化锌(zno)、氧化锆(zro2)和/或其组合。

17.一种用于制造衬底的方法,所述方法包括:

18.根据权利要求17所述的方法,其中形成所述多个互连件包括:

19.根据权利要求18所述的方法,其中将所述uv光施加到所述浆料上包括:使用直接成像将uv光束引导到所述浆料上,以选择性地硬化所述浆料的对应于互连件的数字直接成像图案的部分。

20.根据权利要求18所述的方法,其中将所述uv光施加到所述浆料上包括:将来自蒸汽灯的uv光束通过掩模引导到所述浆料上,以选择性地硬化所述浆料的对应于互连件的图案的部分。

21.根据权利要求18所述的方法,其中所述浆料包括厚膜浆料,并且所述导电材料包括导电材料的颗粒和/或晶体。

22.根据权利要求17所述的方法,其中所述电介质层包括陶瓷、低温共烧陶瓷(ltcc)、高温共烧陶瓷(htcc)、玻璃、氧化锌(zno)、氧化锆(zro2)、氮化铝(aln)和/或其组合中的一者或多者。

23.根据权利要求17所述的方法,其中所述至少一个互连件被形成为具有有效形状,所述有效形状为矩形、方形或椭圆形中的一者或多者。

24.根据权利要求17所述的方法,

25.根据权利要求17所述的方法,其中所述至少一个互连件被形成为具有在大约1:2与1:1之间的高度与宽度纵横比。

26.根据权利要求17所述的方法,其中至少一个互连件具有侧截面,所述侧截面具有拐角半径在大约0.5微米-2微米的范围内的至少一个拐角。

技术总结

一种封装件,包括集成器件、耦合到集成器件的衬底和耦合到衬底的包封层。包封层将集成器件包封。衬底包括至少一个电介质层、位于至少一个电介质层中的多个互连件,其中互连件中的至少一个互连件具有矩形侧截面,矩形侧截面具有拐角半径小于拐角半径阈值的至少一个拐角。

技术研发人员:S·布伦纳

受保护的技术使用者:高通股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!