具有漏极接法场板的坚固的LDMOS的制作方法

本说明书涉及微电子器件领域。更具体地但不排它地,本说明书涉及横向扩散金属氧化物半导体(ldmos)器件。

背景技术:

1、本发明涉及(ldmos)晶体管,并且具体涉及一种坚固性改进的ldmos晶体管。随着诸如dc-dc转换器之类的功率半导体器件按比例缩放到下一代器件,期望改进性能、减小管芯尺寸并增加半导体器件的安全操作区域(soa)。增加半导体器件的soa是改进器件的整体坚固性的一种方法。

技术实现思路

1、提供该

技术实现要素:

以简化形式介绍所描述概念的简要选择,这些概念将在下面包括所提供的附图的详细描述中进一步描述。该发明内容不限制要求保护的主题的范围。

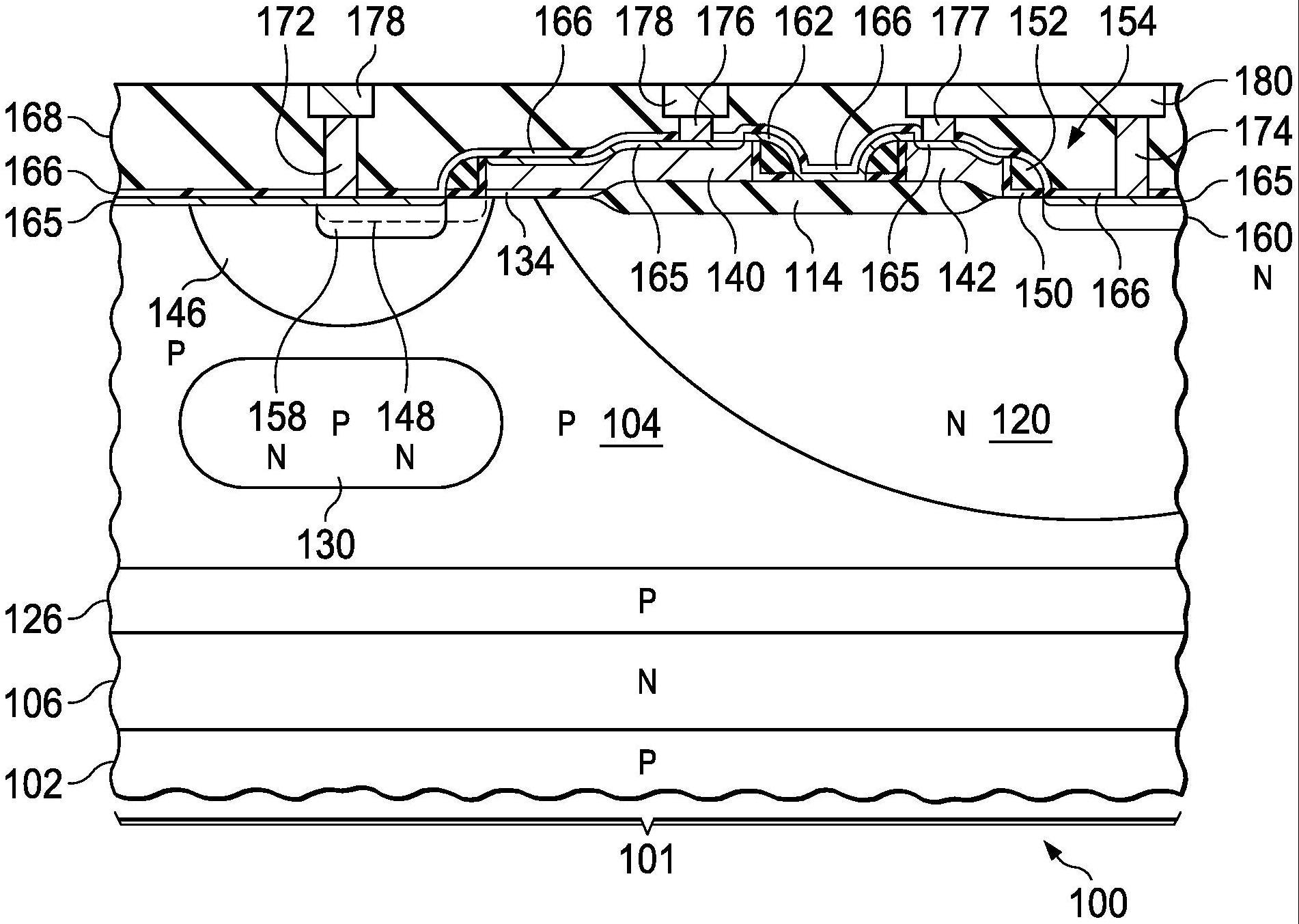

2、所描述的示例包括半导体器件,该半导体器件包括漏极扩展金属氧化物半导体(mos)晶体管,本文称为demos晶体管,其包括与漏极欧姆接触区相邻的漏极接法(drain-tied)场板。所描述的示例提供了用于形成此类demos晶体管的相关联的工艺流程。

技术特征:

1.一种半导体器件,其包括:

2.根据权利要求1所述的半导体器件,其中所述漏极接法场板遵循具有圆角的路径,所述圆角的半径大于所述场板的厚度。

3.根据权利要求1所述的半导体器件,其中所述场板大约平行于所述漏极区延伸。

4.根据权利要求1所述的半导体器件,其中所述场释放电介质层包括具有锥形边缘的二氧化硅的硅的硅局部氧化层即locos层,并且所述场板位于所述锥形边缘上方。

5.根据权利要求1所述的半导体器件,其中:

6.根据权利要求1所述的半导体器件,其中所述第一导电型为p型,并且所述第二导电型为n型。

7.根据权利要求1所述的半导体器件,其中所述场板包含多晶硅。

8.根据权利要求1所述的半导体器件,其中所述栅极电极和所述场板具有闭环配置。

9.根据权利要求1所述的半导体器件,其中所述场板在所述漏极区和所述栅极之间延伸的距离至少是所述场释放电介质层的厚度的两倍。

10.根据权利要求1所述的半导体器件,其中所述场板在所述场释放电介质层的锥形边缘上方延伸。

11.一种形成半导体器件的方法,其包括:

12.根据权利要求11所述的方法,其中与所述栅极电极同时形成所述场板。

13.根据权利要求11所述的方法,其中通过使用所述场板将所述第二导电类型的掺杂剂注入所述漂移区以在所述漏极区的周边阻挡所述第二导电类型的所述掺杂剂来形成所述漏极区。

14.根据权利要求11所述的方法,其中所述场板位于所述场释放电介质层的边缘上方。

15.根据权利要求11所述的方法,其还包括:

16.根据权利要求11所述的方法,其中所述场释放电介质层通过硅局部氧化工艺即locos工艺形成。

17.根据权利要求11所述的方法,其中所述第一导电类型为p型并且所述第二导电类型为n型。

18.根据权利要求11所述的方法,其还包括形成电介质材料的侧壁间隔物,所述侧壁间隔物邻接所述场板并且在所述场板和所述漏极区之间。

技术总结

一种半导体器件,其包括衬底,该衬底具有包含横向扩散金属氧化物半导体晶体管的半导体层,该半导体层包括第一导电类型的管体区和相反导电类型的漂移区。在管体的沟道区上方的栅极电介质层,栅极电介质在管体区和漏极区之间的结上方延伸;栅极电介质上的栅极电极;以及在漏极漂移区中的漏极触点,漏极区具有第二导电类型。在漏极漂移区上的场释放电介质层,其从漏极区延伸到栅极电介质,其厚度大于栅极电介质层。场释放电介质上的漏极接法场板,漏极接法场板从漏极区朝向栅极延伸,其中在漏极接法场板和漏极区之间具有电连接。

技术研发人员:H·L·爱德华兹,G·薛

受保护的技术使用者:德克萨斯仪器股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!