包括拉伸应变和压缩应变的鳍片部分的鳍片堆叠的制作方法

本发明一般涉及电气、电子和计算机领域,并且更具体地涉及鳍式半导体结构和器件以及在鳍片堆叠(fin stack)的不同部分中具有不同应变的这样的结构和器件的制造。

背景技术:

1、鳍式场效应晶体管(finfet)具有三维非平面配置,包括在衬底上方延伸的鳍状结构。一些nfet器件需要半导体层处于拉伸应变下以提高电子迁移率。诸如pfet器件的其它器件或元件需要半导体层处于压缩应变下以增强空穴迁移率。通过提供选定范围内的锗原子百分比,可以设计在弛豫si1-xgex层上外延生长的硅或硅锗层上的应变量。当前技术涉及使用sige合金,该sige合金在缓冲层(si0.75ge0.25)中具有例如百分之二十五(25%)的锗,并且在邻接的pfet层中具有包含更高百分比的锗的合金(例如si 0.5ge 0.5)。

技术实现思路

1、提供了用于制造在相同鳍的电隔离部分中具有不同应变属性的堆叠的鳍型cmos器件的技术。还提供了包括堆叠的鳍型nfet和pfet器件的单片半导体结构,其表现出增强的载流子迁移率。

2、在一个方面,一种制造鳍式单片半导体结构的方法包括在电介质层内形成至少一个沟槽,并向下延伸到半导体衬底层,以及在所述至少一个沟槽内外延地形成底部半导体基础区,并邻接所述半导体衬底层。通过纵横比俘获来俘获底部半导体基础区内的缺陷。第一半导体鳍片区外延形成在底部半导体基础区上的至少一个沟槽内。第一半导体鳍片区具有第一应变类型。该方法进一步包括在该第一半导体鳍片区上方的该至少一个沟槽内外延形成第二半导体鳍片区,该第二半导体鳍片区具有第二应变类型。第一应变类型不同于第二应变类型。

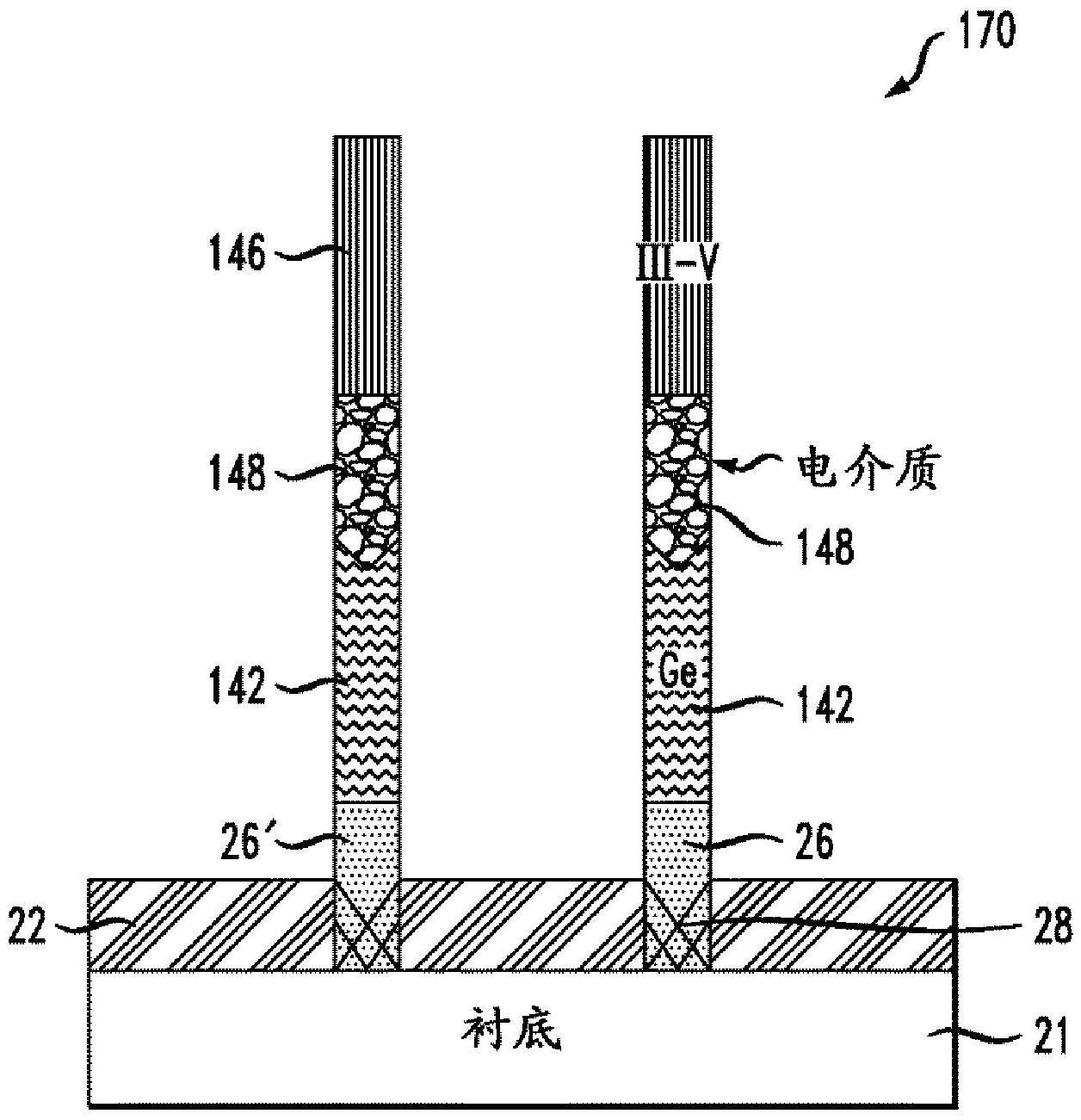

3、在另一方面,鳍式单片半导体结构包括衬底层和相对于衬底层垂直延伸的鳍式结构。该鳍片结构包括垂直堆叠层,该垂直堆叠层包括具有第一应变类型的底部半导体鳍片区和具有第二应变类型的顶部半导体鳍区。第一应变类型不同于第二应变类型。电介质层使底部半导体鳍片区相对于顶部半导体鳍片区电隔离。

4、根据本发明的另一方面的半导体器件包括半导体衬底层和相对于半导体衬底层垂直延伸的多层叠层。该多层堆叠包括:n型finfet,包括拉伸应变沟道区;p型finfet,包括压缩应变沟道区;以及电介质层,垂直地位于n型finfet和p型finfet之间并将n型finfet与p型finfet电隔离。

5、如本文所公开的技术可以提供实质上有益的技术效果。仅作为示例而非限制,一个或多个实施例可提供以下优点中的一个或多个:

6、■增加的晶体管密度;

7、■增强的载流子迁移率;

8、■在电隔离的鳍片部分的不同部分中的不同应变。

9、从以下结合附图阅读的对本发明的说明性实施例的详细描述中,这些和其它特征和优点将变得显而易见。

技术特征:

1.一种制造鳍式单片半导体结构的方法,包括:

2.根据权利要求1所述的方法,其中,形成所述第一半导体鳍片区包括在所述底部半导体基区上外延生长第一半导体材料,并且使所述第一半导体材料凹陷在所述至少一个沟槽内。

3.根据权利要求2所述的方法,还包括:

4.根据权利要求3所述的方法,其中,所述底部半导体基础区包括硅锗,并且所述第一半导体材料包括大于所述底部半导体基础区的锗浓度。

5.根据权利要求3所述的方法,还包括:

6.根据权利要求5所述的方法,其中,所述凹陷和所述电介质锚结构延伸到所述半导体衬底层中。

7.根据权利要求1所述的方法,还包括:

8.根据权利要求7所述的方法,其中,所述第二半导体鳍片区包括iii-v族化合物。

9.根据权利要求7所述的方法,其中,外延地形成所述第二半导体鳍片区包括在所述顶部半导体基础区的所述刻面的顶部表面上生长化合物半导体材料。

10.根据权利要求1所述的方法,还包括:

11.一种鳍式单片半导体结构,包括:

12.根据权利要求11所述的鳍式单片半导体结构,其中,所述鳍片结构还包括外延底部半导体基础区,所述外延底部半导体基础区位于所述衬底层上并包括弛豫的上部,所述底部半导体鳍片区相对于所述底部半导体基础区是外延的。

13.根据权利要求12所述的鳍式单片半导体结构,其中,所述底部半导体鳍片区和所述底部半导体基础区包含锗,所述底部半导体基础区具有与所述底部半导体鳍片区不同的锗浓度。

14.根据权利要求13所述的鳍式单片半导体结构,还包括在所述底部半导体鳍片区和所述电介质层之间的硅层。

15.根据权利要求12所述的鳍式单片半导体结构,其中,所述底部半导体鳍片区和所述顶部半导体鳍片区包括{100}或{110}侧壁面。

16.根据权利要求11所述的鳍式单片半导体结构,其中,所述顶部半导体鳍片区包括化合物半导体材料。

17.根据权利要求16所述的鳍式单片半导体结构,其中,所述底部半导体鳍片区包括具有邻接所述电介质层的刻面的顶表面的锗或硅锗层。

18.根据权利要求11所述的鳍式单片半导体结构,还包括:

19.一种半导体器件,包括:

20.根据权利要求19所述的半导体器件,其中,所述多层堆叠包括:

21.根据权利要求20所述的半导体器件,其中,所述底部半导体鳍片区和所述底部半导体基础区包括锗,所述底部半导体基础区具有与所述底部半导体鳍片区不同的锗浓度。

22.根据权利要求20所述的半导体器件,其中,所述底部半导体鳍片区的一部分包括所述p型finfet的所述沟道区,并且所述顶部半导体鳍片区的一部分包括所述n型finfet的所述沟道区。

23.根据权利要求22所述的半导体器件,其中,所述底部半导体鳍片区是具有带刻面的顶表面的锗或硅锗鳍片区,并且所述顶部半导体鳍片区包括化合物半导体材料。

24.根据权利要求22所述的半导体器件,其中,所述底部半导体鳍片区包括具有n型导电性的硅锗,并且所述顶部半导体鳍片区包括具有p型导电性的硅。

25.根据权利要求19所述的半导体器件,其中,所述拉伸应变沟道区和所述压缩应变沟道区包括具有{100}或{110}面的鳍片侧壁部分。

技术总结

提供了一种鳍式单片半导体结构、其制造方法和半导体器件。该鳍式单片半导体结构包括衬底层(21),相对于衬底层垂直延伸的鳍片结构,该鳍片结构包括垂直堆叠的层,其包括具有第一应变类型的底部半导体鳍区(34),具有第二应变类型的顶部层半导体鳍区(26”),以及在顶部半导体鳍片区(26”)和底部半导体鳍片区之间且将其电隔离的介电层(36A),其中第一应变类型与第二应变类型不同。制造结构的方法包括在电介质层(22)内形成至少一个沟槽(24)并向下延伸至衬底层(21),在至少一个沟槽(24)内并与衬底层(21)相邻地外延形成底部半导体基础区,其中外延形成底部半导体基础区进一步包括通过纵横比俘获在底部半导体基区内的缺陷,在底部半导体基底区上的至少一个沟槽(24)内外延形成第一半导体鳍片区(34),该第一半导体鳍片区(34)具有第一应变类型,以及在第一半导体鳍片区域(34)上方的至少一个沟槽(24)内外延形成第二半导体鳍片区域(26”),该第二半导体鳍片区域(26')具有第二应变类型,其中该第一应变类型与该第二应变类型不同。包括鳍式单片半导体结构的半导体器件在相同鳍的电隔离部分具有不同的应变特性。

技术研发人员:程慷果,J·弗鲁吉尔,谢瑞龙,朴灿鲁

受保护的技术使用者:国际商业机器公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!