拓扑半金属互连的制作方法

背景技术:

1、本发明涉及电气、电子和计算机领域。具体地,本公开涉及拓扑半金属互连(topological semi-metal interconnect)及其制造方法。

2、在半导体制造中,在已经创建半导体器件之后,将它们彼此连接以形成期望的电路。这在一系列步骤中完成,这些步骤统称为后端制程(beol)处理。beol处理涉及创建各种金属互连(例如,导线和通孔(via)),通过电介质层(dielectric layer)将它们彼此隔离,以将半导体器件连接在一起。

技术实现思路

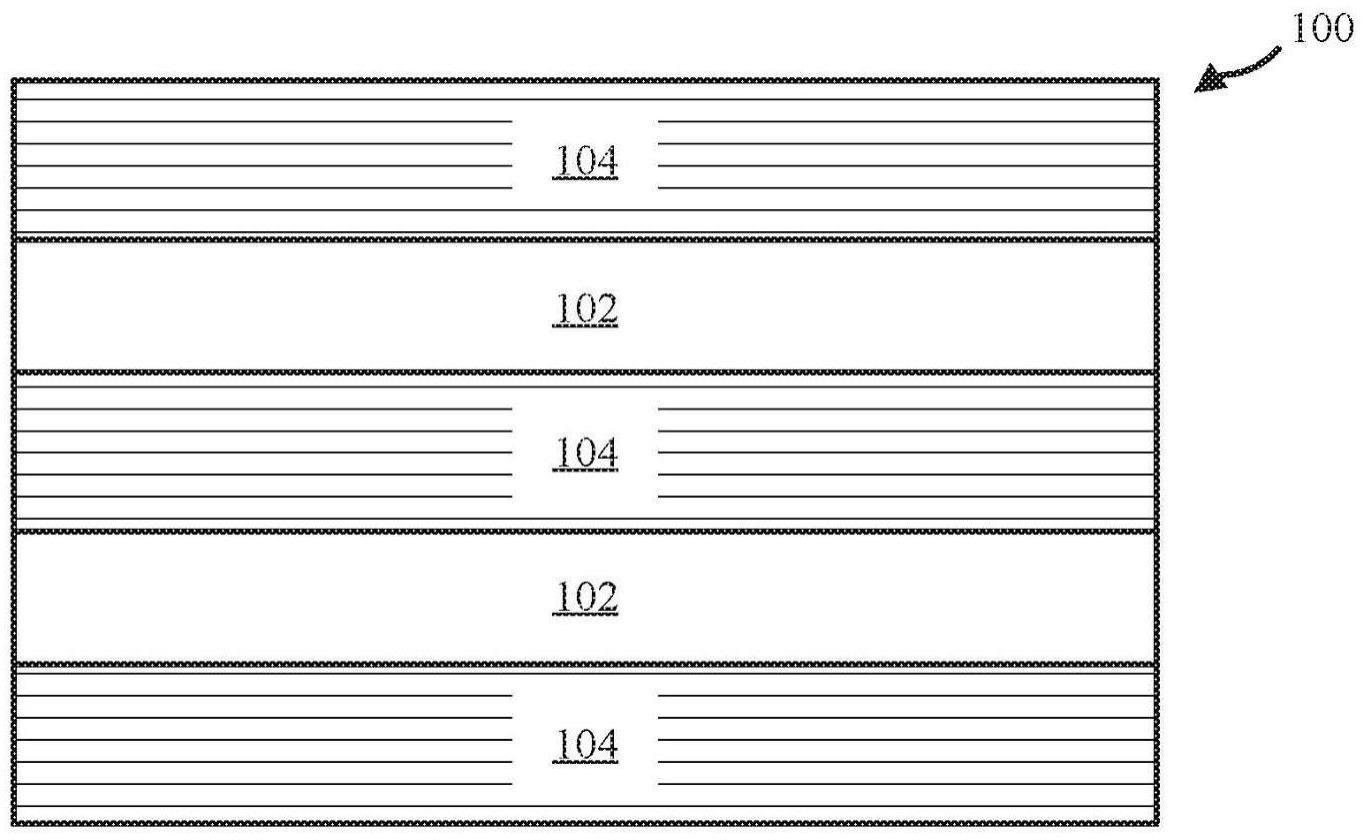

1、本公开的实施例包括一种用于制造互连的方法。该方法包括形成拓扑半金属层。该方法还包括图案化拓扑半金属层以形成一个或多个互连。该方法还包括在一个或多个互连之间形成电介质层。该方法还包括在一个或多个互连和电介质层的顶部上形成密封电介质盖层。

2、本公开的另外的实施例包括半导体器件。半导体器件包括一个或多个后段制程互连。一个或多个后端制程互连包括拓扑半金属导体。

3、本公开的附加实施例包括互连。互连包括拓扑半金属材料。

4、上述

技术实现要素:

并非旨在描述本公开的每个所示实施例或每种实施方式。

技术特征:

1.一种方法,包括:

2.根据权利要求1所述的方法,其中所述拓扑半金属层是nbas。

3.根据权利要求1所述的方法,其中所述方法还包括:

4.根据权利要求3所述的方法,其中所述保护层包括选自包括以下的组中的一种或多种:

5.根据权利要求1所述的方法,其中在所述一个或多个互连之间形成所述电介质层将所述一个或多个互连彼此电隔离。

6.根据权利要求1所述的方法,其中在所述一个或多个互连之间形成所述电介质层还包括:

7.根据权利要求1所述的方法,其中所述电介质层包括低k电介质。

8.根据权利要求1所述的方法,其中所述一个或多个互连的厚度在1nm和100nm之间。

9.根据权利要求1所述的方法,其中所述拓扑半金属层包括具有在所述拓扑半金属的weyl结点的能量的25mev内的费米能量的拓扑半金属。

10.一种半导体器件,包括一个或多个后段制程互连,所述后段制程互连包括拓扑半金属导体。

11.根据权利要求10所述的半导体器件,其中所述拓扑半金属导体包括非磁性非中心对称weyl半金属。

12.根据权利要求10所述的半导体器件,其中所述拓扑半金属导体包括磁性weyl半金属。

13.根据权利要求10所述的半导体器件,其中所述拓扑半金属导体包括多重叠费米子半金属。

14.根据权利要求10所述的半导体器件,其中所述拓扑半金属导体包含kramers-weyl半金属。

15.根据权利要求10所述的半导体器件,其中所述一个或多个后端工艺互连连接各个半导体器件以创建一个或多个集成电路。

16.一种互连,包括拓扑半金属材料。

17.根据权利要求16所述的互连,其中所述拓扑半金属材料的费米能在其weyl结点的能量的25mev内。

18.根据权利要求16所述的互连,其中所述拓扑半金属材料的厚度在1nm与100nm之间。

19.根据权利要求16所述的互连,其中所述拓扑半金属材料的厚度在3nm与10nm之间。

20.根据权利要求16所述的互连,其中所述互连是包括导线和通孔的组中的一者。

技术总结

提供一种互连的制造方法。该方法包括形成拓扑半金属层。该方法还包括图案化拓扑半金属层以形成一个或多个互连。该方法还包括在一个或多个互连之间形成电介质层。该方法还包括在一个或多个互连和电介质层的顶部上形成密封电介质盖层。

技术研发人员:陈敬慈,N·A·兰兹洛,V·纳拉亚南,野上毅

受保护的技术使用者:国际商业机器公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!