功率器件的封装结构及封装方法

本发明涉及半导体封装,尤其涉及一种功率器件的封装结构及封装方法。

背景技术:

1、电子设备实现预设功能的主要部件是芯片,随着集成电路技术的不断进步,芯片的集成度越来越高,芯片的功能越来越强大,而芯片的尺寸越来越小,故芯片需要通过封装形成封装结构,以便于芯片与外部电路板电连接。

2、集成控制电路的功率器件结构较为复杂,引出端比单独的功率器件更多,对应的功能更多。该类功率器件的芯片常包含各种大功率焊盘以及小功率焊盘。对于芯片的大功率焊盘,通过的电压电流较大,要求封装引入的导通电阻越小越好。而相关技术中,通过采用单一的封装形式来进行芯片的封装,这样容易造成封装后的导通电阻超标,从而导致芯片发热,甚至损坏。

技术实现思路

1、鉴于上述问题,提出了本发明以便提供一种克服上述问题或者至少部分地解决上述问题的一种功率器件的封装结构及封装方法。

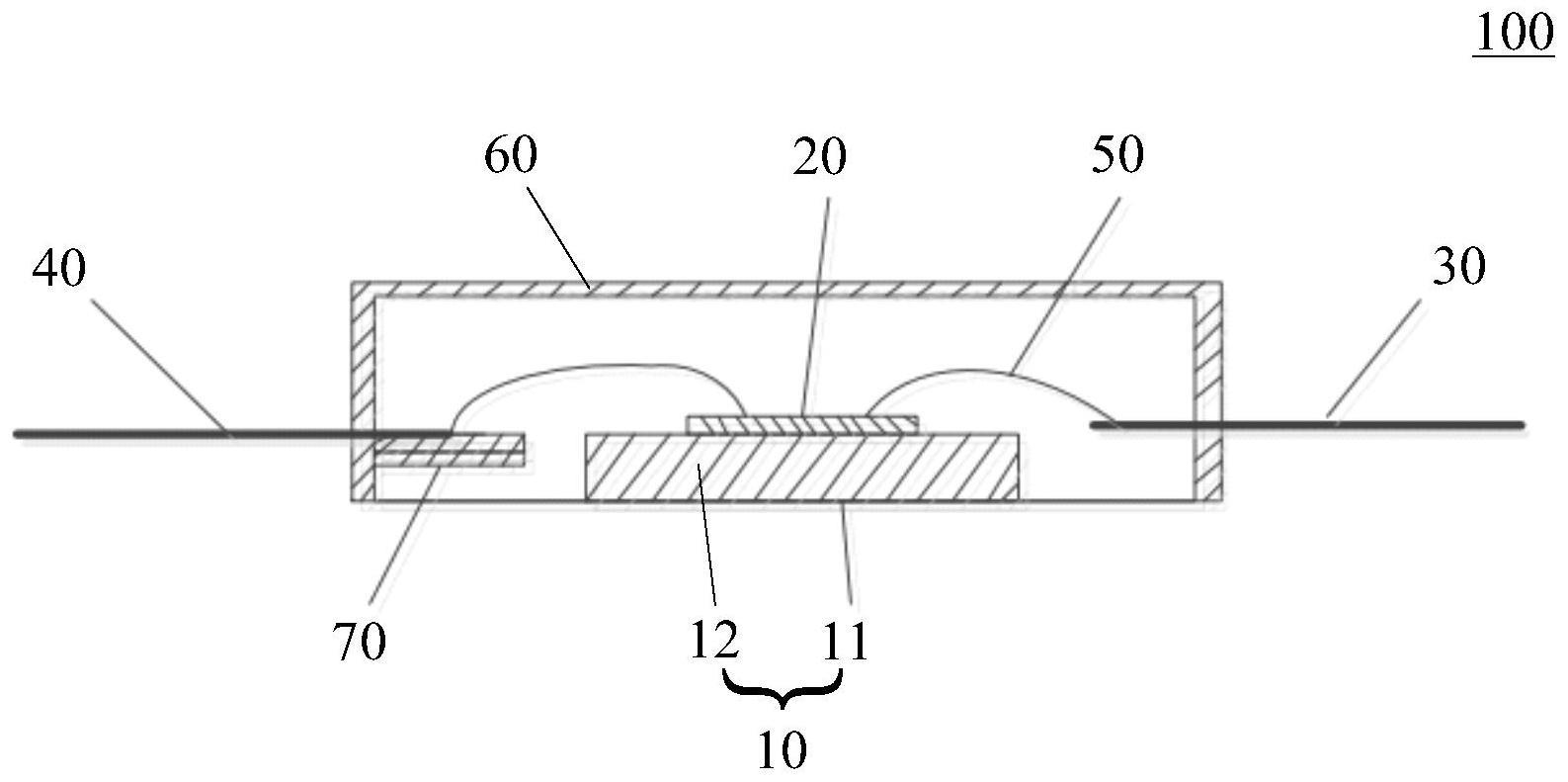

2、一方面,本发明提供了一种功率器件的封装结构,所述封装结构包括功率器件的芯片、底座、至少一个高阻外接引脚、至少一个低阻外接引脚和多根键合丝;

3、所述底座用于支撑所述芯片,所述芯片具有至少一个大功率焊盘和至少一个小功率焊盘,所述至少一个大功率焊盘通过所述键合丝与所述至少一个低阻外接引脚电连接,所述至少一个小功率焊盘通过所述键合丝与所述至少一个高阻外接引脚连接。

4、可选的,所述高阻外接引脚的材料为可伐合金材料。

5、可选的,所述低阻外接引脚的材料为纯铜或锆铜材料。

6、可选的,所述高阻外接引脚和所述低阻外接引脚为片状或柱状。

7、可选的,所述底座包括底板和位于所述底板上的基座,所述芯片位于所述基座的远离所述底板的一面上。

8、可选的,所述芯片通过连接材料粘附在所述基座上,所述连接材料为焊料片或粘片胶。

9、可选的,所述封装结构还包括封装罩,所述封装罩覆盖所述底座、所述芯片、所述至少一个高阻外接引脚、所述至少一个低阻外接引脚和所述多根键合丝,且所述至少一个高阻外接引脚和所述至少一个低阻外接引脚部分裸露在所述封装罩外。

10、可选的,所述封装罩内还设有用于支撑所述至少一个低阻外接引脚的垫片。

11、可选的,所述封装罩与所述底座之间密封连接。

12、另一方面,本发明提供了一种功率器件的封装方法,所述封装方法包括:

13、提供一功率器件的芯片,所述芯片具有至少一个大功率焊盘和至少一个小功率焊盘;

14、采用键合丝将所述大功率焊盘与低阻外接引脚电连接;

15、采用键合丝将所述小功率焊盘与高阻外接引脚电连接。

16、本发明实施例中提供的技术方案,至少具有如下技术效果或优点:

17、本发明实施例提供的一种功率器件的封装结构及封装方法,可以通过键合丝将芯片上的大功率焊盘与低阻外接引脚电连接,通过键合丝将芯片上的小功率焊盘与高阻外接引脚电连接。这样,可以有效降低封装引入的导通电阻的阻值,防止因封装引入的导通电阻的阻值过大,造成的功率器件芯片发热损坏等问题。

18、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

技术特征:

1.一种功率器件的封装结构,其特征在于,所述封装结构包括功率器件的芯片、底座、至少一个高阻外接引脚、至少一个低阻外接引脚和多根键合丝;

2.根据权利要求1所述的封装结构,其特征在于,所述高阻外接引脚的材料为可伐合金材料。

3.根据权利要求1所述的封装结构,其特征在于,所述低阻外接引脚的材料为纯铜或锆铜材料。

4.根据权利要求1所述的封装结构,其特征在于,所述高阻外接引脚和所述低阻外接引脚为片状或柱状。

5.根据权利要求1所述的封装结构,其特征在于,所述底座包括底板和位于所述底板上的基座,所述芯片位于所述基座的远离所述底板的一面上。

6.根据权利要求5所述的封装结构,其特征在于,所述芯片通过连接材料粘附在所述基座上,所述连接材料为焊料片或粘片胶。

7.根据权利要求1所述的封装结构,其特征在于,所述封装结构还包括封装罩,所述封装罩覆盖所述底座、所述芯片、所述至少一个高阻外接引脚、所述至少一个低阻外接引脚和所述多根键合丝,且所述至少一个高阻外接引脚和所述至少一个低阻外接引脚部分裸露在所述封装罩外。

8.根据权利要求7所述的封装结构,其特征在于,所述封装罩内还设有用于支撑所述至少一个低阻外接引脚的垫片。

9.根据权利要求7所述的封装结构,其特征在于,所述封装罩与所述底座之间密封连接。

10.一种功率器件的封装方法,其特征在于,采用如权利要求1至9任一项所述的封装结构,所述封装方法包括:

技术总结

本发明公开了一种功率器件的封装结构及封装方法,包括功率器件的芯片、底座、至少一个高阻外接引脚、至少一个低阻外接引脚和多根键合丝;所述底座用于支撑所述芯片,所述芯片具有至少一个大功率焊盘和至少一个小功率焊盘,每个所述大功率焊盘通过一根所述键合丝与一个所述低阻外接引脚电连接,每个所述小功率焊盘通过一根所述键合丝与一个所述高阻外接引脚连接。该封装结构可以有效降低封装引入的导通电阻的阻值,防止因封装引入的导通电阻的阻值过大,造成的功率器件芯片发热损坏等问题。

技术研发人员:王可,高见头,曾传滨,孙澎,周净男,蔡小五,赵发展

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!