一种失效定位方法与流程

本发明涉及半导体,特别是涉及一种失效定位方法。

背景技术:

1、在集成电路工艺中,随着金属层次的不断增加,金属互连之间的失效已经成为影响芯片良率的一个非常重要的因素。

2、传统分析金属互连断路失效的方法,是在待观测金属层露出后,利用激光或离子束将金属线的一端接地,另一端浮空。利用vc(电压衬度)分析方法,就可以定位出断路的位置,然后再在该位置进行tem切片分析,最终找到产生断路的工艺原因。

3、随着工艺的不断发展,能够造成失效的缺陷也变得原来越小,传统的分析方法在定位此类微小缺陷时也越来越困难,急需开发一种新的方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种失效定位方法,用于解决现有技术中在定位微小缺陷方面,无法找出产生断路原因的问题。

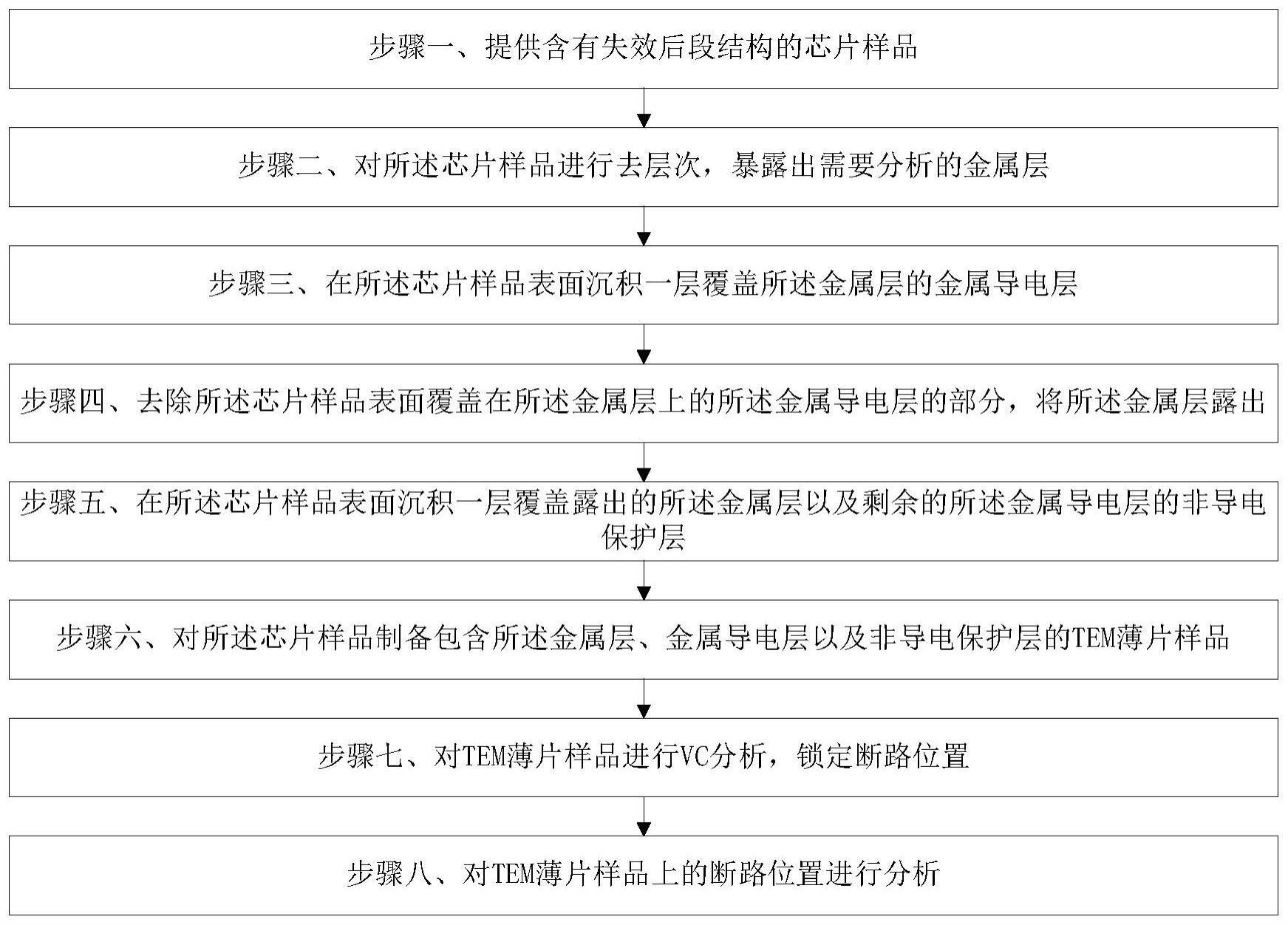

2、为实现上述目的及其他相关目的,本发明提供一种失效定位方法,该方法至少包括以下步骤:

3、步骤一、提供含有失效后段结构的芯片样品;

4、步骤二、对所述芯片样品进行去层次,暴露出需要分析的金属层;

5、步骤三、在所述芯片样品表面沉积一层覆盖所述金属层的金属导电层;

6、步骤四、去除所述芯片样品表面覆盖在所述金属层上的所述金属导电层的部分,将所述金属层露出;

7、步骤五、在所述芯片样品表面沉积一层覆盖露出的所述金属层以及剩余的所述金属导电层的非导电保护层;

8、步骤六、对所述芯片样品制备包含所述金属层、金属导电层以及非导电保护层的tem薄片样品;

9、步骤七、对tem薄片样品进行vc分析,锁定断路位置;

10、步骤八、对tem薄片样品上的断路位置进行分析。

11、优选地,步骤三中采用fib沉积所述金属导电层。

12、优选地,步骤四中采用fib去除覆盖在所述金属层上的所述金属导电层的部分。

13、优选地,步骤五中采用fib沉积所述非导电保护层。

14、优选地,步骤五中的所述非导电保护层为碳保护层。

15、优选地,步骤六中采用fib制备tem薄片样品。

16、优选地,步骤七中采用fib对所述tem薄片样品进行vc分析。

17、优选地,步骤八中采用tem对所述tem薄片样品上的断路位置进行分析。

18、如上所述,本发明的失效定位方法,具有以下有益效果:本发明解决了微小缺陷造成的金属后段断路问题无法定位分析的困难,并且可以在失效定位后,不需再加工样品,直接进行tem分析,极大地提高了分析的成功率和质量。

技术特征:

1.一种失效定位方法,其特征在于,该方法至少包括以下步骤:

2.根据权利要求1所述的失效定位方法,其特征在于:步骤三中采用fib沉积所述金属导电层。

3.根据权利要求1所述的失效定位方法,其特征在于:步骤四中采用fib去除覆盖在所述金属层上的所述金属导电层的部分。

4.根据权利要求1所述的失效定位方法,其特征在于:步骤五中采用fib沉积所述非导电保护层。

5.根据权利要求4所述的失效定位方法,其特征在于:步骤五中的所述非导电保护层为碳保护层。

6.根据权利要求1所述的失效定位方法,其特征在于:步骤六中采用fib制备tem薄片样品。

7.根据权利要求1所述的失效定位方法,其特征在于:步骤七中采用fib对所述tem薄片样品进行vc分析。

8.根据权利要求1所述的失效定位方法,其特征在于:步骤八中采用tem对所述tem薄片样品上的断路位置进行分析。

技术总结

本发明提供一种失效定位方法,提供含有失效后段结构的芯片样品;对芯片样品进行去层次,暴露出需要分析的金属层;在芯片样品表面沉积一层覆盖所述金属层的金属导电层;去除芯片样品表面覆盖在金属层上的所述金属导电层的部分,将金属层露出;在芯片样品表面沉积一层覆盖露出的金属层以及剩余的金属导电层的非导电保护层;对芯片样品制备包含金属层、金属导电层以及非导电保护层的TEM薄片样品;对TEM薄片样品进行VC分析,锁定断路位置;对TEM薄片样品上的断路位置进行分析。本发明解决了微小缺陷造成的金属后段断路问题无法定位分析的困难,并且可以在失效定位后,不需再加工样品,直接进行TEM分析,极大地提高了分析的成功率和质量。

技术研发人员:陈强,高金德

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!