半导体结构的制作方法及半导体结构与流程

本公开涉及半导体,尤其涉及一种半导体结构的制作方法及半导体结构。

背景技术:

1、动态随机存取存储器(dynamic random access memory,简称dram)体积小、集成度高、功耗低,随着动态随机存取存储器集成度提高,字线(wordline,简称wl)的特征尺寸不断减小,甚至已经减小到10nm以下,字线的线宽减小直接导致字线电阻的急剧增大,同时字线的线宽减小还会导致栅诱导漏极泄漏电流(gate induced drain leakage,简称gidl)增加,影响字线晶体管的可靠性。

技术实现思路

1、以下是对本公开详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本公开提供了一种半导体结构的制作方法及半导体结构。

3、本公开的第一方面提供了一种半导体结构的制作方法,所述半导体结构的制作方法包括:

4、提供衬底;

5、在所述衬底中形成字线沟槽;

6、于所述字线沟槽的槽壁形成栅氧层;

7、于所述字线沟槽中形成栅极导电层,所述栅极导电层覆盖部分所述栅氧层,所述栅极导电层的顶面形成凸面。

8、根据本公开的一些实施例,所述字线沟槽包括第一沟槽以及形成于所述第一沟槽底部的第二沟槽;

9、形成于所述第一沟槽的侧壁的所述栅氧层的厚度大于形成于所述第二沟槽的槽壁的所述栅氧层的厚度。

10、根据本公开的一些实施例,所述第一沟槽的侧壁的所述栅氧层和所述第二沟槽的侧壁的所述栅氧层的内壁面平齐。

11、根据本公开的一些实施例,所述在所述衬底中形成字线沟槽,包括:

12、去除部分所述衬底,形成第一沟槽;

13、基于所述第一沟槽刻蚀部分所述衬底,在所述第一沟槽的下方形成所述第二沟槽,所述第一沟槽的槽宽大于所述第二沟槽的槽宽。

14、根据本公开的一些实施例,所述于所述字线沟槽的槽壁形成栅氧层,包括:

15、形成第一氧化层,所述第一氧化层至少覆盖所述第一沟槽的侧壁;

16、形成第二氧化层,所述第二氧化层覆盖所述第二沟槽的槽壁以及位于所述第一沟槽的侧壁的所述第一氧化层,所述第二氧化层和位于所述第一沟槽的侧壁的所述第一氧化层共同形成所述栅氧层。

17、根据本公开的一些实施例,所述于所述字线沟槽中形成栅极导电层,包括:

18、形成初始栅极导电层,所述初始栅极导电层部分填充所述字线沟槽,所述初始栅极导电层的顶面低于所述衬底的顶面;

19、在预定条件下,刻蚀所述初始栅极导电层的顶面,去除部分所述初始栅极导电层,形成所述凸面,被保留的所述初始栅极导电层形成所述栅极导电层。

20、根据本公开的一些实施例,沿所述衬底的厚度方向,所述凸面的最低点高于所述第二沟槽,且所述凸面的最高点低于所述衬底的顶面。

21、根据本公开的一些实施例,所述制作方法包括:

22、刻蚀所述初始栅极导电层时,所述初始栅极导电层的顶面的边缘的刻蚀速率大于所述初始栅极导电层的顶面的中心的刻蚀速率。

23、根据本公开的一些实施例,所述凸面为弧面,由所述弧面的边缘至所述弧面的中心,刻蚀速率逐渐减小。

24、根据本公开的一些实施例,所述制作方法,还包括:

25、形成阻挡层,所述阻挡层覆盖部分所述栅氧层,所述阻挡层位于所述栅极导电层的侧壁和所述栅氧层之间,以及所述栅极导电层的底壁和所述栅氧层之间。

26、根据本公开的一些实施例,所述形成阻挡层,还包括:

27、形成初始阻挡层,所述初始阻挡层覆盖所述栅氧层;

28、沿所述衬底的厚度方向,去除位于所述凸面的最低点以上的所述初始阻挡层,被保留的所述初始阻挡层形成阻挡层。

29、根据本公开的一些实施例,还包括:

30、形成隔离层,所述隔离层覆盖所述栅极导电层的顶面并填充所述字线沟槽的未被填充的区域,所述隔离层的顶面与所述衬底的顶面平齐。

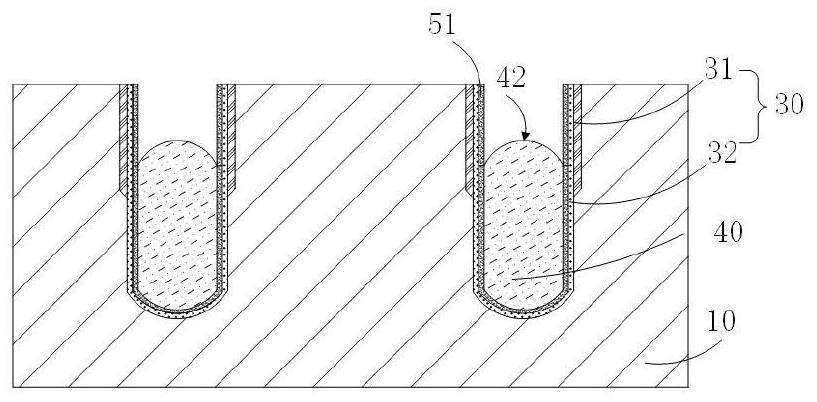

31、本公开的第二方面提供了一种半导体结构,所述半导体结构包括:

32、衬底;

33、字线沟槽,所述字线沟槽设置在所述衬底中,所述字线沟槽的槽壁设置有栅氧层;

34、栅极导电层,所述栅极导电层覆盖部分所述栅氧层,所述栅极导电层的顶面被设置成凸面。

35、根据本公开的一些实施例,所述字线沟槽包括第一沟槽以及设置于所述第一沟槽底部的第二沟槽;

36、覆盖所述第一沟槽的侧壁的所述栅氧层的厚度大于覆盖所述第二沟槽的槽壁的所述栅氧层的厚度。

37、根据本公开的一些实施例,所述第一沟槽的侧壁的所述栅氧层和所述第二沟槽的侧壁的所述栅氧层的内壁面平齐。

38、根据本公开的一些实施例,沿所述衬底的厚度方向,所述凸面的最低点高于所述第二沟槽,且所述凸面的最高点低于所述衬底的顶面。

39、根据本公开的一些实施例,所述半导体结构,还包括:

40、阻挡层,所述阻挡层覆盖部分所述栅氧层,所述阻挡层位于所述栅极导电层的侧壁和所述栅氧层之间,以及所述栅极导电层的底壁和所述栅氧层之间;

41、隔离层,所述隔离层覆盖所述栅极导电层的顶面并填充所述字线沟槽的未被填充的区域,所述隔离层的顶面与所述衬底的顶面平齐。

42、本公开实施例所提供的半导体结构的制作方法及半导体结构中,栅极导电层的顶面为凸面,增加了栅极导电层的截面面积,减小了栅极导电层的电阻;且栅极导电层的顶面的边缘距离衬底的顶面最远,减小了以栅极导电层作为栅极形成的晶体管的栅漏交叠区域,以避免或减小栅诱导漏极泄漏电流,提高了晶体管的可靠性并减小晶体管的功率。

43、在阅读并理解了附图和详细描述后,可以明白其他方面。

技术特征:

1.一种半导体结构的制作方法,其特征在于,所述半导体结构的制作方法包括:

2.根据权利要求1所述的半导体结构的制作方法,其特征在于,所述字线沟槽包括第一沟槽以及形成于所述第一沟槽底部的第二沟槽;

3.根据权利要求2所述的半导体结构的制作方法,其特征在于,所述第一沟槽的侧壁的所述栅氧层和所述第二沟槽的侧壁的所述栅氧层的内壁面平齐。

4.根据权利要求2所述的半导体结构的制作方法,其特征在于,所述在所述衬底中形成字线沟槽,包括:

5.根据权利要求4所述的半导体结构的制作方法,其特征在于,所述于所述字线沟槽的槽壁形成栅氧层,包括:

6.根据权利要求2所述的半导体结构的制作方法,其特征在于,所述于所述字线沟槽中形成栅极导电层,包括:

7.根据权利要求2所述的半导体结构的制作方法,其特征在于,

8.根据权利要求6所述的半导体结构的制作方法,其特征在于,所述制作方法包括:

9.根据权利要求6所述的半导体结构的制作方法,其特征在于,所述凸面为弧面,由所述弧面的边缘至所述弧面的中心,刻蚀速率逐渐减小。

10.根据权利要求1所述的半导体结构的制作方法,其特征在于,所述制作方法,还包括:

11.根据权利要求10所述的半导体结构的制作方法,其特征在于,所述形成阻挡层,还包括:

12.根据权利要求1所述的半导体结构的制作方法,其特征在于,所述制作方法,还包括:

13.一种半导体结构,其特征在于,所述半导体结构包括:

14.根据权利要求13所述的半导体结构,其特征在于,所述字线沟槽包括第一沟槽以及设置于所述第一沟槽底部的第二沟槽;

15.根据权利要求14所述的半导体结构,其特征在于,所述第一沟槽的侧壁的所述栅氧层和所述第二沟槽的侧壁的所述栅氧层的内壁面平齐。

16.根据权利要求14所述的半导体结构,其特征在于,沿所述衬底的厚度方向,所述凸面的最低点高于所述第二沟槽,且所述凸面的最高点低于所述衬底的顶面。

17.根据权利要求13所述的半导体结构,其特征在于,所述半导体结构,还包括:

技术总结

本公开提供了一种半导体结构的制作方法及半导体结构,半导体结构的制作方法包括,提供衬底;在衬底中形成字线沟槽;于所线沟槽的槽壁形成栅氧层;于字线沟槽中形成栅极导电层,栅极导电层覆盖部分所述栅氧层,栅极导电层的顶面形成凸面。本公开提供的半导体结构的制作方法形成的半导体结构中,栅极导电层的顶面为凸面,增加了栅极导电层的截面面积,减小了栅极导电层的电阻;且栅极导电层的顶面的边缘距离衬底的顶面最远,减小了以栅极导电层作为栅极形成的晶体管的栅漏交叠区域,以避免或减小栅诱导漏极泄漏电流,提高了晶体管的可靠性并减小晶体管的功率。

技术研发人员:崔兆培,宋影

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!