碳化硅器件的制造方法与流程

本发明属于碳化硅器件,特别是涉及一种碳化硅器件的制造方法。

背景技术:

1、碳化硅材料作为第三代宽禁带半导体材料的代表之一,具有禁带宽度大、临界击穿电场高、热导率高和电子饱和漂移速度高等特点,在大功率、高温及高频电力电子领域具有广阔的应用前景。沟槽型碳化硅器件消除了平面型碳化硅器件中寄生的jfet电阻,减小了元胞尺寸,使得电流密度显著提高,同时也降低了导通电阻,因此沟槽型碳化硅器件逐步取代平面型碳化硅器件成为主流。碳化硅器件通常采用二氧化硅作为栅介质层材料,由于碳化硅的介电常数约是二氧化硅的2.5倍,在碳化硅器件处于阻断状态时栅介质层承受了约2.5倍的漂移层电场。在沟槽型碳化硅器件中,栅沟槽底部拐角处的电场分布集中,使得栅沟槽底部拐角处的栅介质层更容易在碳化硅器件发生雪崩击穿前被击穿,使得碳化硅器件的可靠性降低。

技术实现思路

1、有鉴于此,本发明的目的是提供一种碳化硅器件的制造方法,以提高碳化硅器件的可靠性。

2、本发明实施例提供的一种碳化硅器件的制造方法,包括:

3、在提供的n型碳化硅层上形成硬掩膜层,通过光刻工艺定义出栅沟槽的位置,对所述硬掩膜层进行刻蚀将所述n型碳化硅层暴露出来;

4、以剩余的所述硬掩膜层为掩膜,对所述n型碳化硅层进行各向异性刻蚀在所述n型碳化硅层内形成浅沟槽,在所述浅沟槽内对所述n型碳化硅层进行各向同性刻蚀在所述n型碳化硅层内形成栅沟槽;

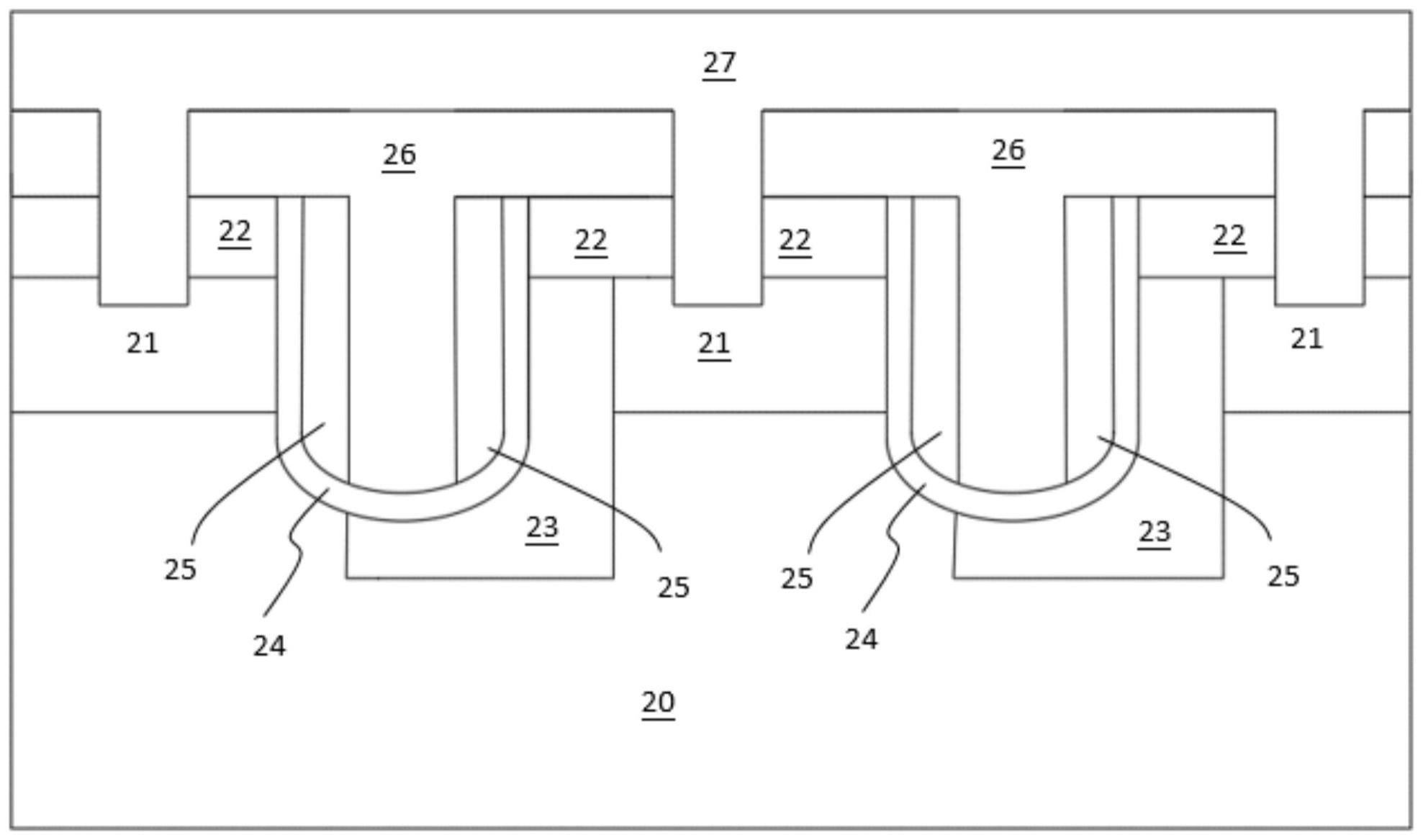

5、进行垂直的p型离子注入和倾斜的p型离子注入,在所述n型碳化硅层内形成p+区域,所述p+区域位于所述栅沟槽的一侧并从所述栅沟槽的侧壁位置处延伸至所述栅沟槽的底部;

6、在所述栅沟槽的表面形成栅介质层,淀积一层导电层并以剩余的所述硬掩膜层为掩膜回刻所述导电层,在所述栅沟槽的侧壁处形成栅极。

7、可选的,本发明的碳化硅器件的制造方法,还包括:

8、去除所述硬掩膜层,在所形成结构的表面形成钝化层,并对所述钝化层进行刻蚀形成接触孔,形成正面金属层。

9、可选的,本发明的碳化硅器件的制造方法,所述钝化层填充所述栅沟槽。

10、可选的,本发明的碳化硅器件的制造方法,所述n型碳化硅层包括n型外延层,以及位于所述n型外延层顶部的p型体区和位于所述p型体区内的n型源区,所述栅沟槽的深度大于所述p型体区的深度。

11、可选的,本发明的碳化硅器件的制造方法,所述导电层为掺杂的多晶硅。

12、本发明通过自对准刻蚀方式优化栅沟槽的底部形貌,可以有效降低栅沟槽底部拐角处的电场强度,使得栅沟槽底部拐角处的栅介质层不容易被击穿,从而提高碳化硅器件的可靠性。同时,本发明使用刻蚀形成栅沟槽的硬掩膜层来实现p+区域的自对准离子注入和栅极的自对准刻蚀,可大幅精简制造工艺,降低制造成本。

技术特征:

1.一种碳化硅器件的制造方法,其特征在于,包括:

2.如权利要求1所述的碳化硅器件的制造方法,其特征在于,还包括:

3.如权利要求2所述的碳化硅器件的制造方法,其特征在于,所述钝化层填充所述栅沟槽。

4.如权利要求1所述的碳化硅器件的制造方法,其特征在于,所述n型碳化硅层包括n型外延层,以及位于所述n型外延层顶部的p型体区和位于所述p型体区内的n型源区,所述栅沟槽的深度大于所述p型体区的深度。

5.如权利要求1所述的碳化硅器件的制造方法,其特征在于,所述导电层为掺杂的多晶硅。

技术总结

本发明实施例提供的一种碳化硅器件的制造方法,包括:在n型碳化硅层上形成硬掩膜层,通过光刻工艺定义出栅沟槽的位置,然后对硬掩膜层进行刻蚀并以剩余的硬掩膜层为掩膜,通过各向异性刻蚀和各向同性刻蚀相结合的方法在n型碳化硅层内形成栅沟槽;进行垂直的p型离子注入和倾斜的p型离子注入,在n型碳化硅层内形成p+区域,p+区域位于栅沟槽的一侧并从栅沟槽的侧壁位置处延伸至栅沟槽的底部;在栅沟槽的表面形成栅介质层,然后淀积一层导电层并回刻,在栅沟槽的侧壁处形成栅极。本发明使用刻蚀形成栅沟槽的硬掩膜层来实现p+区域的自对准离子注入和栅极的自对准刻蚀,可大幅精简制造工艺,降低制造成本。

技术研发人员:范让萱,缪进征,王鹏飞

受保护的技术使用者:苏州东微半导体股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!