电子封装件及其制法的制作方法

本发明有关一种半导体装置,尤指一种电子封装件及其制法。

背景技术:

1、随着电子产业的蓬勃发展,电子产品也逐渐迈向多功能、高性能的趋势。目前应用于芯片封装领域的技术,包含有例如芯片尺寸构装(chip scale package,简称csp)、芯片直接贴附封装(direct chip attached,简称dca)或多芯片模块封装(multi-chip module,简称mcm)等覆晶型态的封装模块,或将芯片立体堆叠化整合为三维积体电路(3d ic)堆叠技术等。

2、图1为现有三维积体电路堆叠的封装结构1的剖面示意图。如图1所示,该封装结构1将一硅中介板(through silicon interposer,简称tsi)1a经由焊锡凸块16设于封装基板19上,且以底胶191包覆该些焊锡凸块16。该硅中介板1a具有一硅板体10及多个形成于其中的导电硅穿孔(through-silicon via,简称tsv)101,且该硅板体10的表面上形成有一电性连接该导电硅穿孔101的线路重布结构(redistribution layer,简称rdl),其中,该线路重布结构包含一介电层11及一形成于该介电层11上的线路层12,且该线路层12电性连接该导电硅穿孔101,并形成一绝缘保护层13于该介电层11与该线路层12上,且该绝缘保护层13外露部分该线路层12,以结合多个焊锡凸块14,供设置半导体芯片17,再以底胶171包覆该些焊锡凸块14。之后,形成封装材18于该封装基板19上,以令该封装材18包覆该半导体芯片17与该硅中介板1a。

3、再者,可形成另一绝缘保护层15于该硅板体10上,且该绝缘保护层15外露该些导电硅穿孔101的端面,以于该些导电硅穿孔101的端面上结合并电性连接多个焊锡凸块16,其中,可选择性于该导电硅穿孔101的端面上形成供接置该焊锡凸块16的凸块底下金属层(under bump metallurgy,简称ubm)160。

4、于后续应用中,该封装结构1可形成多个焊球192于该封装基板19的下侧,以接置于一电路板1b上。

5、然而,现有封装结构1于制作该硅中介板1a时,需先将硅板体10置放于一玻璃载板上,再进行该导电硅穿孔101与rdl的制作,待制作该导电硅穿孔101与rdl后,需再移除该玻璃载板,造成材料成本增加与制程的困扰。

6、因此,如何克服上述现有技术的问题,实已成为目前业界亟待克服的难题。

技术实现思路

1、鉴于上述现有技术的种种缺陷,本发明提供一种电子封装件及其制法,可有效的缩短电流传输路径,以提升电性表现。

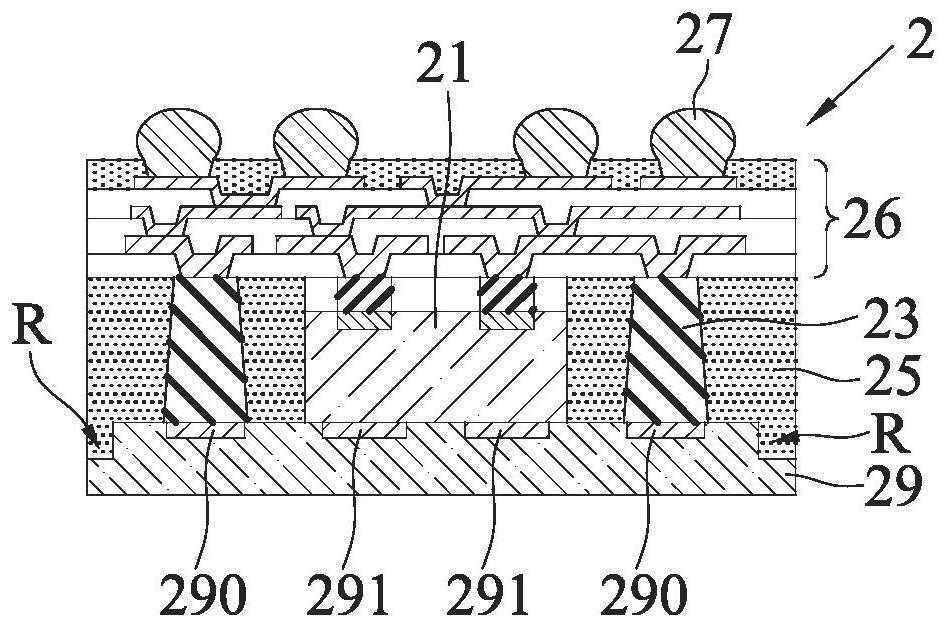

2、本发明的电子封装件,包括:电子结构,其具有多个接点,且该多个接点未凸出该电子结构的表面;电子元件,其叠设于该电子结构上;多个导电柱,其设于该电子结构上,以电性连接该电子结构的多个接点;包覆层,其形成于该电子结构上,以包覆该电子元件与该多个导电柱;以及线路结构,其设于该包覆层上,以电性连接该多个导电柱。

3、本发明还提供一种电子封装件的制法,包括:提供一整版面晶圆体,其包含多个阵列排设的电子结构,且各该电子结构具有多个接点;将一电子元件设于各该电子结构上,且各该电子结构上形成有多个电性连接该多个接点的多个导电柱;于各该电子结构之间形成凹槽,且该凹槽并未贯穿该电子结构;形成包覆层于该整版面晶圆体上,以令该包覆层包覆该电子元件与该多个导电柱;形成线路结构于该包覆层上,以令该线路结构电性连接该多个导电柱;以及沿该凹槽进行切单制程。

4、前述的电子封装件及其制法中,该电子元件接触该电子结构的表面。

5、前述的电子封装件及其制法中,该电子元件经由结合层黏固于该电子结构上。

6、前述的电子封装件及其制法中,该电子元件电性连接该线路结构。

7、前述的电子封装件及其制法中,该电子元件具有多个电极垫,以令该电子元件以该多个电极垫对应接合于该电子结构的多个接点上并电性连接该多个接点。

8、前述的电子封装件及其制法中,该电子结构配置有布线结构,以供接置及电性连接该多个导电柱。进一步,该布线结构上还接置及电性连接该电子元件。

9、前述的电子封装件及其制法中,该电子结构的边缘形成有阶梯部。

10、前述的电子封装件及其制法中,该多个导电柱的端面齐平该包覆层的表面。

11、前述的电子封装件及其制法中,还包括形成多个导电元件于该线路结构上,且令该多个导电元件电性连接该线路结构。

12、由上可知,本发明的电子封装件及其制法中,主要经由该整版面晶圆体取代传统无线路的玻璃载板,故相比于现有技术,本发明的制法免用玻璃载板而可节省材料成本。

13、再者,该电子结构无需形成焊锡凸块,故可降低该电子封装件的整体高度,且可有效的缩短电流传输路径,以提升电性表现。

14、另外,该包覆层于五个面向封装该电子结构与该电子元件,使该电子结构的五个面与该电子元件的五个面受到保护,以避免该电子结构与该电子元件于制程中崩坏。

技术特征:

1.一种电子封装件,包括:

2.如权利要求1所述的电子封装件,其中,该电子元件接触该电子结构的表面。

3.如权利要求1所述的电子封装件,其中,该电子元件经由结合层黏固于该电子结构上。

4.如权利要求1至3中任一者所述的电子封装件,其中,该电子元件电性连接该线路结构。

5.如权利要求1所述的电子封装件,其中,该电子元件具有多个电极垫,且令该电子元件以该多个电极垫对应接合并电性连接于该电子结构的多个接点。

6.如权利要求1所述的电子封装件,其中,该电子结构配置有布线结构,以供接置及电性连接该多个导电柱。

7.如权利要求6所述的电子封装件,其中,该电子元件设置并电性连接于该布线结构上。

8.如权利要求1所述的电子封装件,其中,该电子结构的边缘形成有阶梯部。

9.如权利要求1所述的电子封装件,其中,该多个导电柱的端面齐平该包覆层的表面。

10.如权利要求1所述的电子封装件,其中,该电子封装件还包括形成于该线路结构上的多个导电元件,且令该多个导电元件电性连接该线路结构。

11.一种电子封装件的制法,包括:

12.如权利要求11所述的电子封装件的制法,其中,该电子元件接触该电子结构的表面。

13.如权利要求11所述的电子封装件的制法,其中,该电子元件经由结合层黏固于该电子结构上。

14.如权利要求11至13中任一者所述的电子封装件的制法,其中,该电子元件电性连接该线路结构。

15.如权利要求11所述的电子封装件的制法,其中,该电子元件具有多个电极垫,且令该电子元件以该多个电极垫对应接合并电性连接于该电子结构的多个接点上。

16.如权利要求11所述的电子封装件的制法,其中,该电子结构配置有布线结构,以供接置及电性连接该多个导电柱。

17.如权利要求16所述的电子封装件的制法,其中,该电子元件设置并电性连接于该布线结构上。

18.如权利要求11所述的电子封装件的制法,其中,该电子结构的边缘形成有阶梯部。

19.如权利要求11所述的电子封装件的制法,其中,该多个导电柱的端面齐平该包覆层的表面。

20.如权利要求11所述的电子封装件的制法,其中,该制法还包括形成多个导电元件于该线路结构上,且令该多个导电元件电性连接该线路结构。

技术总结

本发明涉及一种电子封装件及其制法,包括提供包含多个阵列排设的电子结构的整版面晶圆体,以将电子元件叠设于各该电子结构上,其中,该电子结构上形成有多个导电柱,且于各该电子结构之间形成凹槽,接着形成包覆层于该整版面晶圆体上,并于形成线路结构于该包覆层上后,沿该凹槽进行切单制程,使该电子结构无需形成焊锡凸块,故可降低该电子封装件的整体高度,且可有效的缩短电流传输路径,以提升电性表现。

技术研发人员:李孟杰,蔡芳霖

受保护的技术使用者:矽品精密工业股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!