用于优化信号路由的管芯基板的制作方法

本申请总体上涉及管芯基板及其制造方法,并且具体地,涉及包括该管芯基板的集成电路封装。

背景技术:

1、随着半导体工艺技术的进步,相同大小的管芯(或芯片)可以集成越来越多的晶体管,以为更高的存储器带宽,并且因此为(诸如图形处理集群(gpc)、纹理处理集群(tpc)或其他多处理器应用中的)高电流需求应用给予更大的功能和性能。然而,更大的功能和更高的电流需求进而要求更大数量的焊球,以在管芯基板的下侧提供更大和/或更密集的球栅阵列(bga)尺寸以承载电流。这种高电流需求和增加的bga尺寸对印刷电路板(pcb)设计布局造成了增加的负担。

2、减小专用于电流输送的bga的尺寸以及提供更高效的电流传导能力对于促进增加计算性能的目标是重要的。

技术实现思路

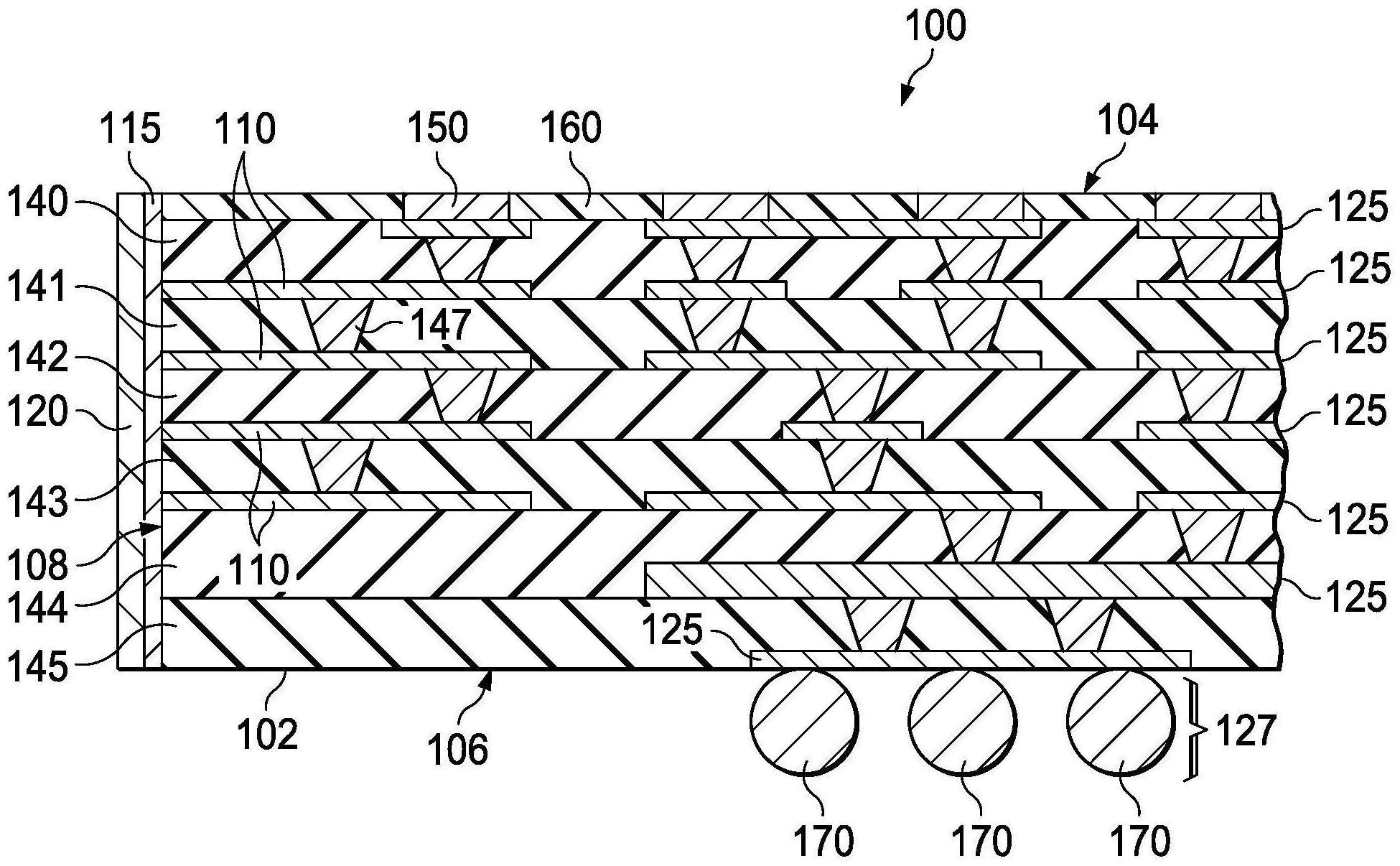

1、一个方面提供了一种管芯基板,该管芯基板包括:电介质本体;位于该电介质本体中的载流金属线;位于至少一个本体边缘表面上的终止层;以及位于至少一个本体边缘表面上的导电镀层。电介质本体具有第一本体表面、在电介质本体的第一表面的相对侧上的第二本体表面、以及位于第一表面和第二表面之间的本体边缘表面。载流金属线中的至少一个或更多个被路由(route)到本体边缘表面中的一个或更多个。终止层被电连接到路由到本体边缘表面的金属线中的至少一个。导电镀层被连接至终止层,用于电流连接或接地连接到至少一个载流金属线。

2、另一方面是一种制造集成电路封装的方法,该方法包括:提供管芯基板。该方法可包括:将管芯基板安装到封装基板,其中导电镀层被电连接到封装基板上的载流线;将电容器安装在封装基板上,其中电容器被电连接到导电镀层;以及将管芯安装到位于第一本体表面上的管芯安装垫。

3、另一方面是一种集成电路封装,该集成电路封装包括管芯基板。封装可包括连接到位于管芯基板的第一本体表面上的管芯安装垫的管芯,其中载流金属线中的一些被连接到管芯安装垫。封装可以包括封装基板,其中管芯基板被安装到封装基板,并且导电镀层被电连接到封装基板上的载流线。封装可包括位于封装基板上的一个或更多个电容器,其中电容器中的每个电容器被电连接至管芯基板的导电镀层中的一个导电镀层。

4、另一方面是一种计算机,该计算机具有包括本文所公开的管芯基板的任何实施例的一个或更多个电路。

技术特征:

1.一种管芯基板,包括:

2.根据权利要求1所述的管芯基板,还包括信号承载金属线,其连接至位于所述第二本体表面上的信号承载焊球阵列。

3.根据权利要求1所述的管芯基板,还包括连接至位于所述第二本体表面上的载流焊球阵列的所述载流金属线中的一个或更多个。

4.根据权利要求3所述的管芯基板,其中所述载流金属线中的一个载流金属线与所述终止层之间的接触面积的导电率大于所述载流金属线中的一个载流金属线连接到所述焊球阵列之间的接触面积的导电率。

5.根据权利要求4所述的管芯基板,其中在所述载流金属线中的一个载流金属线与所述终止层之间的接触面积大于所述载流金属线中的一个载流金属线连接到所述焊球阵列之间的接触面积。

6.根据权利要求1所述的管芯基板,其中所述电介质本体包括电介质层的堆叠,其中所述电介质层中的顶部电介质层提供所述第一本体表面,所述电介质层中的底部电介质层提供所述第二本体表面,并且所述电介质层中的所述顶部电介质层、所述底部电介质层以及中间电介质层中的每个电介质层均提供所述本体边缘表面的部分。

7.根据权利要求6所述的管芯基板,其中所述载流金属线位于所述电介质层上,并且金属过孔将各自位于所述电介质层中的两个不同的电介质层上的所述金属线中的至少两个互连。

8.根据权利要求1所述的管芯基板,其中所述载流金属线中的一些被连接至位于所述第一本体表面上的管芯安装垫。

9.根据权利要求8所述的管芯基板,其中所述管芯基板是集成电路的一部分,其中所述集成电路的管芯被安装至所述管芯安装垫。

10.根据权利要求9所述的管芯基板,其中所述管芯是图形处理单元电路管芯。

11.根据权利要求1所述的管芯基板,其中所述电介质本体由电介质材料组成,所述终止层由焊料合金组成,并且所述导电镀层由铜组成。

12.根据权利要求1所述的管芯基板,其中所述管芯基板是集成电路封装的一部分,并且被安装至所述集成电路封装的封装基板。

13.根据权利要求12所述的管芯基板,其中所述导电镀层被电连接至所述封装基板上的载流线。

14.根据权利要求12所述的管芯基板,还包括连接至位于所述第二本体表面上的焊球阵列的信号承载金属线,其中所述焊球阵列中的焊球电连接至所述封装基板上的信号承载线。

15.根据权利要求12所述的管芯基板,还包括位于所述封装基板上的一个或更多个电容器,其中所述电容器中的每个电容器电连接至所述导电镀层中的一个导电镀层。

16.根据权利要求12所述的管芯基板,其中所述载流金属线中的一些被路由至所述本体边缘表面中的第二本体边缘表面,所述终止层中的第二终止层位于所述第二本体边缘表面上,并且所述导电镀层中的第二导电镀层被连接至所述第二终止层,并且所述第二电容器电连接至所述第二导电镀层。

17.一种制造集成电路封装的方法,包括:

18.根据权利要求17所述的方法,其中提供所述管芯基板还包括:

19.一种集成电路封装,包括:

20.一种计算机,其具有包括根据权利要求19所述的集成电路封装的一个或更多个电路。

技术总结

公开了用于优化信号路由的管芯基板。一种管芯基板,包括:电介质本体,所述本体具有第一本体表面、位于相对侧上的第二本体表面以及位于其间的本体边缘表面。载流金属线,其位于电介质本体中。金属线中的一个或更多个被路由到本体边缘表面的一个或更多个。终止层,其位于至少一个本体边缘表面上并电连接至被路由到所述本体边缘表面的所述金属线中的至少一个。导电镀层,其位于至少一个本体边缘表面上。该镀层连接至终止层,用于电流连接或接地连接到至少一个金属线。还公开了一种制造集成电路封装的方法、集成电路封装以及一种具有管芯基板的计算机。

技术研发人员:延双虎,蔡晓茁,朱浩,易定海,李华明

受保护的技术使用者:辉达公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!