半导体装置及其制造方法与流程

本发明涉及半导体技术,特别是涉及一种包含沟槽型功率晶体管的半导体装置及其制造方法。

背景技术:

1、在电力电子技术中通常会使用功率晶体管,功率金属氧化物半导体场效晶体管(power mosfet)是最常被应用在功率转换系统的组件,其包含水平式结构,例如横向扩散金属氧化物半导体(laterally-diffused metal-oxide semiconductor,ldmos)场效晶体管(field effect transistor,fet),以及垂直式结构,例如平面型栅极金属氧化物半导体场效晶体管(planar gate mosfet)、沟槽型栅极金属氧化物半导体场效晶体管(trenchgate mosfet),沟槽型栅极mosfet将栅极设置于沟槽内,沟槽型栅极mosfet相较于平面型栅极mosfet具有缩小组件单元尺寸、降低寄生电容等好处,但是在导通电阻(on-stateresistance,ron)和击穿电压(breakdown voltage)等方面,传统的沟槽型栅极mosfet仍无法完全满足在电力电子应用上的各种需求。

技术实现思路

1、有鉴于此,本发明提出一种包含沟槽型功率晶体管的半导体装置及其制造方法,以满足沟槽型功率晶体管在电力电子应用上的各种需求,例如降低导通电阻、降低单位阻值(spreading resistance,rsp)、提高或维持击穿电压等,以利于大电流、低电压组件的需求,使其更有效率地应用于电源管理系统(battery management system,bms)。

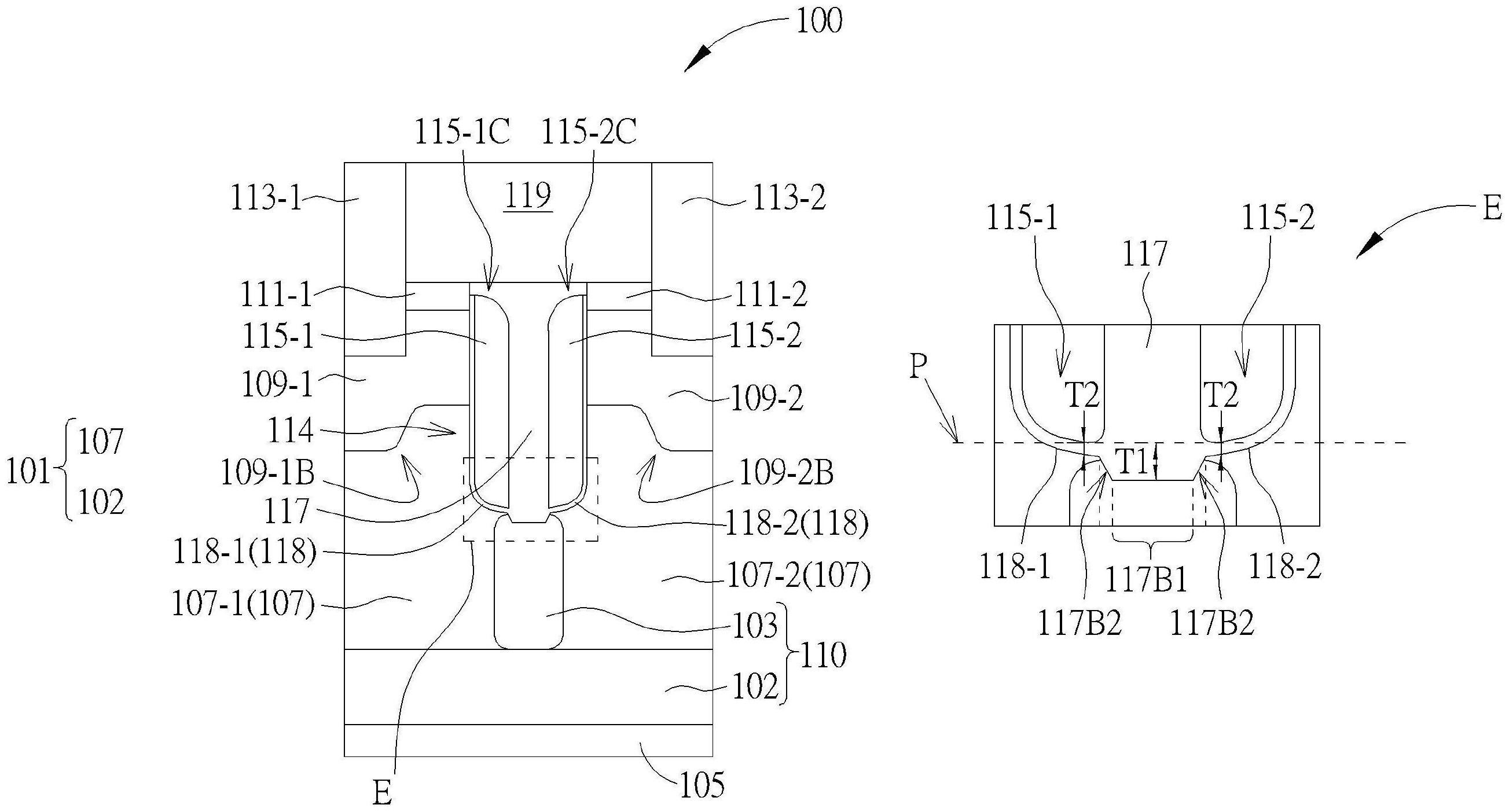

2、根据本发明的一实施例,提供一种半导体装置,包括基底、阱区、沟槽、第一沟槽栅极、第二沟槽栅极、介电分隔部及介电衬层。基底具有第一导电类型,阱区具有第一导电类型且设置于基底内,沟槽设置于基底内,且位于阱区的正上方。第一沟槽栅极和第二沟槽栅极彼此侧向分离,且设置于沟槽内。介电分隔部设置于沟槽内,且位于第一沟槽栅极和第二沟槽栅极之间,其中介电分隔部的底面中心线区域向下突出,低于介电分隔部的底面两侧区域。介电衬层设置于沟槽内,且位于第一沟槽栅极和第二沟槽栅极的底面下方,其中在第一沟槽栅极和第二沟槽栅极的底面的水平线以下,介电分隔部的厚度大于介电衬层的厚度。

3、根据本发明的一实施例,提供一种半导体装置,包括基底、阱区、沟槽、第一沟槽栅极、第二沟槽栅极、介电分隔部、第一掺杂区及第二掺杂区。基底具有第一导电类型,阱区具有第一导电类型,且设置于基底内,沟槽设置于基底内,且位于阱区的正上方。第一沟槽栅极和第二沟槽栅极彼此侧向分离,且设置于沟槽内。介电分隔部设置于沟槽内,且位于第一沟槽栅极和第二沟槽栅极之间。第一掺杂区和第二掺杂区具有第一导电类型,彼此侧向分离,且设置于基底内,其中第一掺杂区和第二掺杂区分别位于阱区的两侧,且阱区的掺杂浓度高于第一掺杂区和第二掺杂区各自的掺杂浓度。

4、根据本发明的一实施例,提供一种半导体装置,包括基底、阱区、沟槽、第一沟槽栅极、第二沟槽栅极及介电分隔部。基底具有第一导电类型,阱区具有第一导电类型,且设置于基底内,沟槽设置于基底内,且位于阱区的正上方。第一沟槽栅极和第二沟槽栅极彼此侧向分离,且设置于沟槽内,介电分隔部设置于沟槽内,且第一沟槽栅极和第二沟槽栅极之间的空间被介电分隔部填满。

5、根据本发明的一实施例,提供一种半导体装置的制造方法,包括以下步骤:提供具有第一导电类型的基底,形成沟槽于基底内;在沟槽的侧壁和底面上顺向地形成介电衬层;在沟槽内形成彼此侧向分离的第一沟槽栅极和第二沟槽栅极,并露出位于沟槽的底面上的介电衬层的一部分;形成阱区于基底内,其中阱区位于第一沟槽栅极和第二沟槽栅极之间的区域正下方;进行热氧化工艺,以在沟槽内形成氧化层;以及在沟槽内填充介电材料层,其中介电材料层和氧化层构成介电分隔部,介电分隔部位于第一沟槽栅极和第二沟槽栅极之间,且介电分隔部的底面中心线区域向下突出,低于介电分隔部的底面两侧区域。

技术特征:

1.一种半导体装置,其特征在于,包括:

2.如权利要求1所述的半导体装置,其特征在于,还包括:

3.如权利要求2所述的半导体装置,其特征在于,所述第一掺杂区和所述第二掺杂区具有一相同的掺杂浓度,且所述阱区的掺杂浓度高于所述第一掺杂区的掺杂浓度。

4.如权利要求2所述的半导体装置,其特征在于,还包括:

5.如权利要求4所述的半导体装置,其特征在于,所述阱区侧向分离于所述第一基体区及所述第二基体区,且所述阱区的顶面低于所述第一基体区及所述第二基体区的底面。

6.如权利要求4所述的半导体装置,其特征在于,还包括:

7.如权利要求6所述的半导体装置,其特征在于,所述第一源极区延伸在所述第一源极电极的底部的两侧,所述第二源极区延伸在所述第二源极电极的底部的两侧。

8.如权利要求6所述的半导体装置,其特征在于,所述第一基体区和所述第二基体区各自具有一第一倾斜底面与一第二倾斜底面,所述第一倾斜底面对应所述第一源极区处较高,且对应到所述第一源极电极处较低,所述第二倾斜底面对应所述第二源极区处较高,且对应到所述第二源极电极处较低。

9.如权利要求8所述的半导体装置,其特征在于,所述第一倾斜底面与所述第二倾斜底面为一多阶梯状底面或一多圆弧状底面。

10.如权利要求4所述的半导体装置,其特征在于,所述第一基体区和所述第二基体区的最低底面高于所述沟槽的底面。

11.如权利要求1所述的半导体装置,其特征在于,所述介电衬层内衬于所述沟槽的侧壁和底面,且所述介电衬层邻接所述介电分隔部的部分的厚度大于所述介电衬层远离所述介电分隔部的部分的厚度。

12.如权利要求1所述的半导体装置,其特征在于,所述介电分隔部的顶面的宽度大于所述介电分隔部的底面的宽度。

13.如权利要求1所述的半导体装置,其特征在于,所述第一沟槽栅极的最大宽度和所述第二沟槽栅极的最大宽度均小于所述介电分隔部的最小宽度。

14.如权利要求1所述的半导体装置,其特征在于,所述第一沟槽栅极具有一第一圆弧顶角邻接所述介电分隔部,且所述第二沟槽栅极具有一第二圆弧顶角邻接所述介电分隔部。

15.一种半导体装置,其特征在于,包括:

16.一种半导体装置,其特征在于,包括:

17.如权利要求16所述的半导体装置,其特征在于,还包括一第一掺杂区和一第二掺杂区,具有所述第一导电类型,彼此侧向分离且设置于所述基底内,其中所述第一掺杂区和所述第二掺杂区分别位于所述阱区的两侧,且所述阱区的掺杂浓度高于所述第一掺杂区和所述第二掺杂区各自的掺杂浓度。

18.如权利要求15或17所述的半导体装置,其特征在于,还包括一第一基体区和一第二基体区,具有与所述第一导电类型相反的一第二导电类型,分别设置于所述第一掺杂区和所述第二掺杂区的正上方,且位于所述沟槽的两侧,其中所述阱区的顶面低于所述第一基体区及所述第二基体区的底面。

19.如权利要求18所述的半导体装置,其特征在于,还包括:

20.如权利要求1、15和16中任一项所述的半导体装置,其特征在于,所述基底的底部的掺杂浓度高于所述阱区的掺杂浓度,且所述基底的所述底部和所述阱区一起作为一共享漏极区。

21.如权利要求15或16所述的半导体装置,其特征在于,还包括一介电衬层内衬于所述沟槽的侧壁和底面,且位于所述第一沟槽栅极和所述第二沟槽栅极的底面下方,其中所述介电衬层邻接所述介电分隔部的部分的厚度大于所述介电衬层远离所述介电分隔部的部分的厚度。

22.一种半导体装置的制造方法,其特征在于,包括:

23.如权利要求22所述的半导体装置的制造方法,其特征在于,所述基底的掺杂浓度在由底部至顶部的方向上逐渐减少,且靠近所述基底的顶面的掺杂浓度较低的部分构成一第一掺杂区和一第二掺杂区,所述第一掺杂区和所述第二掺杂区位于所述阱区的两侧,且所述阱区的掺杂浓度高于所述第一掺杂区和所述第二掺杂区的掺杂浓度。

24.如权利要求23所述的半导体装置的制造方法,其特征在于,还包括:

25.如权利要求24所述的半导体装置的制造方法,其特征在于,还包括:

26.如权利要求25所述的半导体装置的制造方法,其特征在于,所述第一基体区和所述第二基体区一起由多次离子注入工艺形成,且所述第一基体区和所述第二基体区各自具有一多阶梯状底面或一多圆弧状底面,所述第一基体区的底面对应到所述第一源极区处较高,且对应到所述第一源极电极处较低,所述第二基体区的底面对应到所述第二源极区处较高,且对应到所述第二源极电极处较低。

27.如权利要求22所述的半导体装置的制造方法,其特征在于,所述第一沟槽栅极和所述第二沟槽栅极的材料包括多晶硅、掺杂的多晶硅、金属或合金。

技术总结

本发明公开半导体装置及其制造方法,包括第一导电类型的基底和阱区、沟槽、第一沟槽栅极、第二沟槽栅极、介电分隔部及介电衬层。阱区设置于基底内,沟槽设置于基底内,且位于阱区的正上方。第一和第二沟槽栅极彼此侧向分离,且设置于沟槽内。介电分隔部设置于沟槽内,且位于第一和第二沟槽栅极之间,其中介电分隔部的底面中心线区域向下突出,低于介电分隔部的底面两侧区域。介电衬层设置于沟槽内,且位于第一和第二沟槽栅极的底面下方,其中在第一和第二沟槽栅极的底面的水平线以下,介电分隔部的厚度大于介电衬层的厚度。

技术研发人员:陈劲甫

受保护的技术使用者:艾科微电子(深圳)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!