封装结构以及封装方法与流程

本发明实施例涉及半导体封装领域,尤其涉及一种封装结构以及封装方法。

背景技术:

1、对于单片芯片的尺寸,常规的芯片制造技术正在被推向它们的极限。然而,应用却渴望使用最新技术实现大尺寸集成电路的能力,芯片之间实现高速和小体积互连具有较大的挑战。

2、目前的一种解决方案是使用嵌入在硅衬底中的硅桥(si bridge)芯片的较小的集成电路,以通过硅桥芯片实现芯片与芯片之间的互连,进而提供异质芯片封装。

3、但是,目前封装结构的结构较为复杂,且芯片之间的通信速度仍有待提高。

技术实现思路

1、本发明实施例解决的问题是提供一种封装结构以及封装方法,提升芯片之间的通信速度,优化封装结构的性能。

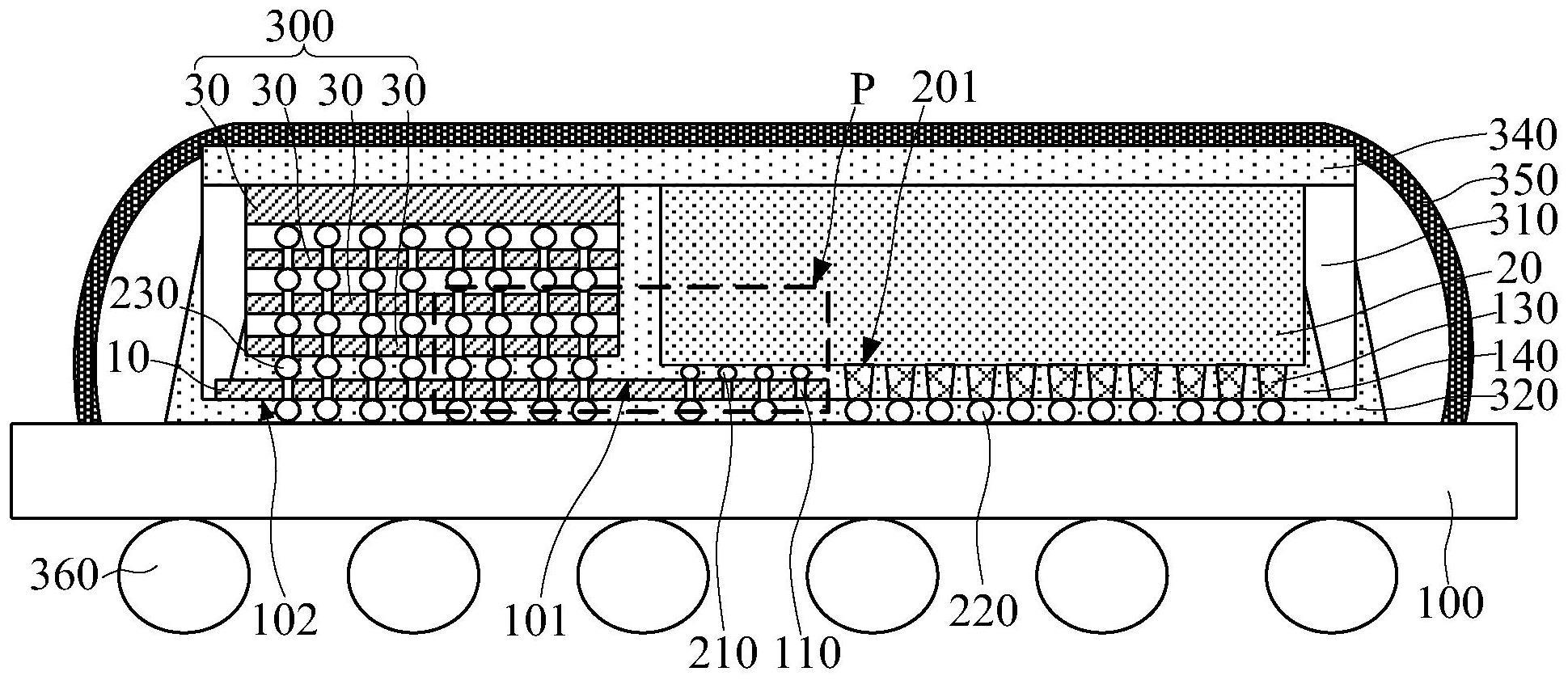

2、为解决上述问题,本发明实施例提供一种封装结构,包括:基板;第一芯片,包括相背的第一表面和第二表面,所述第一表面包括用于键合芯片组的第一键合区、以及用于键合第二芯片的第二键合区;所述第二表面键合于所述基板上;第二芯片,包括第三表面,所述第三表面包括键合于所述第二键合区上的第三键合区,所述第三表面的剩余区域作为第四键合区;导电柱,位于所述第四键合区上,且所述导电柱与所述第二芯片相背的一端键合于所述基板上;芯片组,键合于所述第一芯片的第一键合区上,且所述芯片组在所述第一芯片上的投影暴露出所述第二键合区;所述芯片组包括沿纵向堆叠的一个或多个第三芯片,且沿纵向上的相邻所述第三芯片之间电连接,与所述第一芯片相邻的所述第三芯片和所述第一芯片之间电连接。

3、相应的,本发明实施例还提供一种封装方法,包括:提供承载基底;在所述承载基底上贴合第一芯片,所述第一芯片包括相背的第一表面和第二表面,所述第一表面包括用于键合芯片组的第一键合区、以及用于键合第二芯片的第二键合区;提供第二芯片,包括第三表面,所述第三表面包括与第二键合区对应的第三键合区,所述第三表面的剩余区域作为第四键合区;在所述第二芯片的第四键合区上形成导电柱;实现所述第三键合区与所述第二键合区之间的键合、以及所述导电柱与所述承载基底之间的键合,所述第二芯片与所述第一芯片之间电连接;提供芯片组,包括沿纵向堆叠的一个或多个第三芯片,且沿纵向上的相邻所述第三芯片之间电连接;实现所述芯片组与所述第一键合区之间的键合,且所述芯片组在所述第一芯片上的投影暴露出所述第二键合区,与所述第一芯片相邻的所述第三芯片和所述第一芯片之间电连接;在实现所述第三键合区与所述第二键合区之间的键合、以及实现所述芯片组与所述第一键合区之间的键合之后,去除所述承载基底;实现基板与所述第一芯片的第二表面、以及与所述导电柱之间的键合,所述基板分别与所述第一芯片、以及所述导电柱之间电连接。

4、与现有技术相比,本发明实施例的技术方案具有以下优点:

5、本发明实施例提供的封装结构,所述第二芯片的第三表面包括键合于所述第二键合区上的第三键合区,所述第三表面的第四键合区上形成有导电柱,且所述导电柱与所述第二芯片相背的一端键合于所述基板上,芯片组键合于所述第一芯片的第一键合区上,且所述芯片组在所述第一芯片上的投影暴露出所述第二键合区,从而本发明实施例通过使所述芯片组在所述第一芯片上的投影暴露出所述第二键合区,能够为在第一芯片上键合部分第二芯片提供空间,进而将部分所述第二芯片直接堆叠并键合于第一芯片的第二键合区上,以实现第二芯片与所述第一芯片之间的电连接,进而通过第一芯片使第二芯片与第三芯片之间实现电连接,与通过芯片桥(bridge)实现第二芯片与第一芯片之间的电连接相比,本发明实施例省去了所述芯片桥,有利于简化封装结构、以及减薄封装结构,并且缩短第二芯片与第一芯片之间、以及第二芯片与第三芯片的传输路径,进而提高第二芯片与第一芯片之间、以及第二芯片与第三芯片之间的通信速度,优化了封装结构的性能。

6、本发明实施例提供的封装方法中,在所述第二芯片的第四键合区上形成导电柱,随后实现所述第三键合区与第二键合区之间的键合、以及所述导电柱与所述承载基底之间的贴合,并且实现所述芯片组与第一键合区之间的键合,从而通过使所述第一芯片的第一表面包括用于键合芯片组的第一键合区、以及用于键合第二芯片的第二键合区,能够为在第一芯片上键合部分第二芯片提供空间,进而将部分所述第二芯片直接堆叠并键合于第一芯片的第二键合区上,以实现第二芯片与所述第一芯片之间的电连接,与通过芯片桥(bridge)实现第二芯片与第一芯片之间的电连接相比,本发明实施例省去了所述芯片桥,有利于简化封装流程和封装结构、以及减薄封装结构,并且缩短第二芯片与第一芯片之间、以及第二芯片与第三芯片之间的传输路径,进而提高第二芯片与第一芯片之间、以及第二芯片与第三芯片之间的通信速度,优化了封装结构的性能。

技术特征:

1.一种封装结构,其特征在于,包括:

2.如权利要求1所述的封装结构,其特征在于,所述封装结构还包括:第一封装层,位于所述基板上且覆盖所述芯片组和第二芯片侧壁、以及所述第一芯片。

3.如权利要求1所述的封装结构,其特征在于,所述第二键合区与所述第三键合区相对设置;所述封装结构还包括:第一导电凸块,位于所述第二键合区与所述第三键合区之间。

4.如权利要求3所述的封装结构,其特征在于,所述封装结构还包括:第一密封层,位于所述第二键合区与所述第三键合区之间且填充所述第一导电凸块之间的空隙、以及填充所述第四键合区与所述导电柱围成的区域内。

5.如权利要求1所述的封装结构,其特征在于,所述封装结构还包括:第二导电凸块,位于所述基板与所述第一芯片的第二表面之间、以及所述基板和所述导电柱与第二芯片相背的一端之间。

6.如权利要求5所述的封装结构,其特征在于,所述封装结构还包括:第一封装层,位于所述基板上且覆盖所述芯片组和第二芯片侧壁、以及所述第一芯片;第二密封层,位于所述第二表面与所述基板之间的相邻所述第二导电凸块之间的间隙内,以及所述第一封装层的底面与基板之间的相邻第二导电凸块之间的间隙内。

7.如权利要求1所述的封装结构,其特征在于,所述封装结构还包括:第二封装层,位于所述芯片组侧部的所述第一芯片上且暴露出所述第二键合区。

8.如权利要求1所述的封装结构,其特征在于,所述封装结构还包括:第三导电凸块,位于所述第一芯片的第一键合区与所述芯片组之间。

9.如权利要求1所述的封装结构,其特征在于,所述封装结构还包括:第四导电凸块,位于所述基板与所述第一芯片相背的一侧表面上。

10.如权利要求1-9任一项所述的封装结构,其特征在于,所述第二键合区占所述第一芯片总面积的5%至20%。

11.如权利要求1-9任一项所述的封装结构,其特征在于,所述第一芯片为第一逻辑芯片,所述第二芯片为第二逻辑芯片,所述第三芯片为存储芯片。

12.如权利要求1-9任一项所述的封装结构,其特征在于,所述封装结构还包括:导热层,位于所述芯片组和第二芯片上;封装外壳,位于所述基板上且包封芯片组、第二芯片和第一芯片,所述封装外壳与所述导热层相接触。

13.一种封装方法,其特征在于,包括:

14.如权利要求13所述的封装方法,其特征在于,所述封装方法还包括:在实现所述第三键合区与所述第二键合区之间的键合、以及实现所述芯片组与所述第一键合区之间的键合之后,且在去除所述承载基底之前,在所述承载基底上形成覆盖所述芯片组和第二芯片侧壁、以及所述第一芯片的第一封装层。

15.如权利要求13所述的封装方法,其特征在于,在所述承载基底上贴合第一芯片之后,且在去除所述承载基底之前,实现所述芯片组与所述第一键合区之间的键合。

16.如权利要求13所述的封装方法,其特征在于,在所述承载基底上贴合第一芯片之前,实现所述芯片组与所述第一键合区之间的键合。

17.如权利要求16所述的封装方法,其特征在于,所述封装方法还包括:在实现所述芯片组与第一键合区之间的键合之后,且在所述承载基底上贴合第一芯片之前,在所述第一芯片上形成覆盖所述第二芯片侧壁的第二封装层,所述第二封装层覆盖所述第二键合区;

18.如权利要求17所述的封装方法,其特征在于,采用干法刻蚀工艺,去除位于所述第二键合区的第二封装层。

19.如权利要求13所述的封装方法,其特征在于,实现所述第三键合区与所述第二键合区之间的键合的步骤中,所述第三键合区与所述第二键合区相对设置,且所述第三键合区与所述第二键合区通过第一导电凸块电连接。

20.如权利要求13所述的封装方法,其特征在于,实现所述基板与所述第一芯片的第二表面、以及与所述导电柱之间的键合的步骤包括:利用第二导电凸块,实现所述基板与第一芯片的第二表面之间、以及所述基板与所述导电柱之间的电连接。

技术总结

一种封装结构以及封装方法,结构包括:基板;第一芯片,包括相背的第一表面和第二表面,第一表面包括用于键合芯片组的第一键合区、以及用于键合第二芯片的第二键合区;第二表面键合于基板上;第二芯片,包括第三表面,第三表面包括键合于第二键合区上的第三键合区,第三表面的剩余区域作为第四键合区;导电柱,位于第四键合区上,且导电柱与第二芯片相背的一端键合于基板上;芯片组,键合于第一芯片的第一键合区上,且芯片组在第一芯片上的投影暴露出第二键合区;芯片组包括沿纵向堆叠的一个或多个第三芯片,且沿纵向上的相邻第三芯片之间电连接,与第一芯片相邻的第三芯片和第一芯片之间电连接。本发明实施例提升芯片之间的通信速度。

技术研发人员:金吉松

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!