半导体结构和掩膜版版图的制作方法

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构和掩膜版版图。

背景技术:

1、随着半导体集成电路的集成度越来越高,芯片中晶体管的集成度逐渐达到上限,因此出现了3d集成电路(integrated circuit,ic)技术。3d集成电路被定义为一种系统级集成结构,3d集成电路通过键合工艺实现多个芯片之间的垂直互连,增加了芯片的空间,提高了晶体管的集成度,同时还能提高集成电路的工作速度,降低集成电路的功耗。目前,3d集成电路技术已成为集成电路设计的重要方向之一。

2、目前在3d集成电路技术中大都采用硅通孔(through silicon via,tsv)以及位于硅通孔上方的金属互连结构形成电连接,然后进一步实现晶圆之间的键合。晶圆水平上的金属-金属键合作为3dic中的一项关键技术,在高端产品上的有重要的应用趋势。

3、然而,采用现有技术的半导体结构的设计多样性有待提高。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构和掩膜版版图,有利于提高半导体结构的设计多样性。

2、为解决上述问题,本发明实施例提供一种半导体结构,包括:基底;介电层,位于所述基底上,沿平行于所述介电层表面的方向,所述介电层包括多个子区域;键合互连层,位于所述介电层中,所述键合互连层的顶面被所述介电层背向所述基底的表面暴露,所述键合互连层包括多个接合焊盘,多个所述子区域之间的接合焊盘的密度差异满足:使多个所述子区域中的接合焊盘顶面与介电层顶面均处于同一平面。

3、相应的,本发明实施例还提供一种掩膜版版图,用于形成半导体结构,所述半导体结构包括:基底;介电层,位于所述基底上,沿平行于所述介电层表面的方向,所述介电层包括多个子区域;键合互连层,位于所述介电层中,所述键合互连层的顶面被所述介电层背向所述基底的表面暴露,所述键合互连层包括多个接合焊盘;所述掩膜版版图包括:键合互连层版图,用于形成所述键合互连层,所述键合互连层版图包括多个所述子区域,且所述键合互连层版图包括位于所述子区域中的接合焊盘图形,所述接合焊盘图形用于形成所述接合焊盘,多个所述子区域之间的接合焊盘图形的密度差异满足:使多个所述子区域中的接合焊盘图形对应形成的所述接合焊盘顶面与所述介电层顶面均处于同一平面。

4、与现有技术相比,本发明实施例的技术方案具有以下优点:

5、本发明实施例提供的半导体结构,键合互连层包括多个接合焊盘,多个子区域之间的接合焊盘的密度差异满足:使多个所述子区域中的接合焊盘顶面与介电层顶面均处于同一平面,从而提高后续制程的工艺可靠性,例如,在晶圆键合的情况下,处于同一平面的接合焊盘和介电层有利于提高键合界面的接触紧密性,进而降低键合界面出现缝隙(bubble)的概率,而且,通过控制接合焊盘的密度来满足使多个所述子区域中的接合焊盘和介电层顶面均处于同一平面,以减小对接合焊盘的尺寸的限制,相应有利于增加所述接合焊盘的尺寸多样性,进而有利于提高设计灵活性。

6、本发明实施例提供的掩膜版版图,多个子区域之间的接合焊盘图形的密度差异满足:使多个所述子区域中的接合焊盘图形对应形成的接合焊盘顶面与介电层顶面均处于同一平面,从而提高后续制程的工艺可靠性,例如,在晶圆键合的情况下,处于同一平面的接合焊盘和介电层有利于提高键合界面的接触紧密性,进而降低键合界面出现缝隙的概率,而且,通过控制接合焊盘图形的密度来满足使对应形成的多个所述子区域中的接合焊盘和介电层顶面处于同一平面,以减小对接合焊盘图形的尺寸的限制,相应有利于增加所述接合焊盘图形的尺寸多样性,进而有利于提高设计灵活性。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括堆叠键合的第一晶圆和第二晶圆,所述第一晶圆和第二晶圆均包括所述基底、介电层和键合互连层;

3.如权利要求1所述的半导体结构,其特征在于,所述接合焊盘具有预设尺寸组,所述预设尺寸组包括所述接合焊盘的线宽和相邻接合焊盘的间隔距离,多个所述子区域之间具有多种不同数值的所述预设尺寸组。

4.如权利要求1所述的半导体结构,其特征在于,所述多个子区域的排布方式包括:所述多个子区域依次环绕排布、所述多个子区域沿特定方向并列排布、以及所述多个子区域呈阵列式排布中的一种或多种,其中,所述特定方向为沿平行于所述介电层表面的方向。

5.如权利要求1所述的半导体结构,其特征在于,所述子区域中的键合互连层由多个周期性重复排布的最小重复单元构成,所述最小重复单元包含一个接合焊盘,且所述最小重复单元的边界由两两相邻的四个接合焊盘的边界限定,所述子区域的接合焊盘的密度等于所述最小重复单元中的接合焊盘的密度。

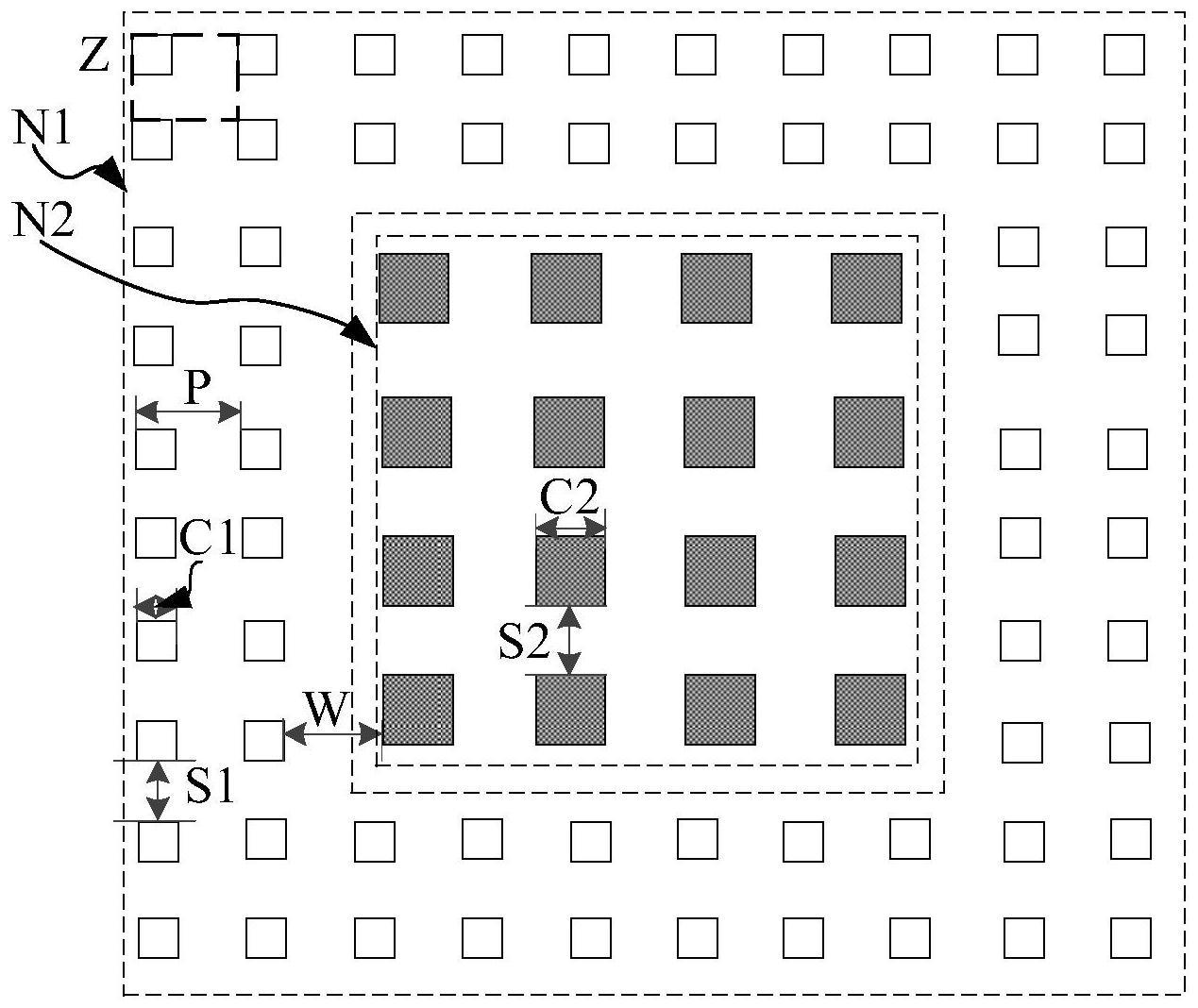

6.如权利要求5所述的半导体结构,其特征在于,所述子区域的最小重复单元的数量至少为4个,且呈2*2的阵列式排布。

7.如权利要求5所述的半导体结构,其特征在于,沿平行于所述介电层表面的方向,所述接合焊盘的形状为正方形,各个所述子区域中的所述接合焊盘的密度为d=c2/p2,其中,d为所述子区域中的接合焊盘的密度,c为所述子区域中的接合焊盘的线宽;p为所述子区域中的相邻所述接合焊盘的节距。

8.如权利要求1~7中任一项所述的半导体结构,其特征在于,各个所述子区域之间的接合焊盘的密度差值小于10%。

9.如权利要求1~7中任一项所述的半导体结构,其特征在于,沿平行于所述介电层表面的方向,相邻所述子区域的接合焊盘的间隔距离w满足s1<w<s2,其中,w为相邻所述子区域的接合焊盘的间隔距离,s1为其中一个子区域内的相邻接合焊盘的间隔距离,s2为另一个子区域内的相邻接合焊盘的间隔距离,且s1小于s2。

10.如权利要求1~7中任一项所述的半导体结构,其特征在于,相邻所述子区域的接合焊盘的间隔距离w满足w=(s1+s2)/2,其中,w为相邻所述子区域的接合焊盘的间隔距离,s1为其中一个子区域内的相邻接合焊盘的间隔距离,s2为另一个子区域内的相邻接合焊盘的间隔距离。

11.如权利要求1~7中任一项所述的半导体结构,其特征在于,所述接合焊盘的材料包括铜或铝。

12.一种掩膜版版图,用于形成半导体结构,所述半导体结构包括:基底;介电层,位于所述基底上,沿平行于所述介电层表面的方向,所述介电层包括多个子区域;键合互连层,位于所述介电层中,所述键合互连层的顶面被所述介电层背向所述基底的表面暴露,所述键合互连层包括多个接合焊盘;

13.如权利要求12所述的掩膜版版图,其特征在于,所述接合焊盘图形具有预设尺寸组,所述预设尺寸组包括所述接合焊盘图形的线宽和相邻接合焊盘图形的间隔距离,多个所述子区域之间具有多种不同数值的所述预设尺寸组。

14.如权利要求12所述的掩膜版版图,其特征在于,所述键合互连层版图适用于形成待堆叠键合的晶圆中的接合焊盘。

15.如权利要求12所述的掩膜版版图,其特征在于,所述多个子区域的排布方式包括:所述多个子区域依次环绕排布、所述多个子区域沿特定方向并列排布、以及所述多个子区域呈阵列式排布中的一种或多种,其中,所述特定方向为沿平行于所述介电层表面的方向。

16.如权利要求12所述的掩膜版版图,其特征在于,所述子区域中的键合互连层版图由多个周期性重复排布的最小重复单元构成,所述最小重复单元包含一个接合焊盘图形,且所述最小重复单元的边界由两两相邻的四个接合焊盘图形的边界限定,所述子区域的接合焊盘图形的密度等于所述最小重复单元中的接合焊盘图形的密度。

17.如权利要求16所述的掩膜版版图,其特征在于,所述子区域的最小重复单元的数量至少为4个,且呈2*2的阵列式排布。

18.如权利要求12~17中任一项所述的掩膜版版图,其特征在于,各个所述子区域之间的接合焊盘图形的密度差值小于10%。

19.如权利要求12~17中任一项所述的掩膜版版图,其特征在于,沿平行于所述介电层表面的方向,相邻所述子区域的接合焊盘图形的间隔距离w满足s1<w<s2,其中,w为相邻所述子区域的接合焊盘图形的间隔距离,s1为其中一个子区域内的相邻接合焊盘图形的间隔距离,s2为另一个子区域内的相邻接合焊盘图形的间隔距离,且s1小于s2。

20.如权利要求12~17中任一项所述的掩膜版版图,其特征在于,相邻所述子区域的接合焊盘图形的间隔距离w满足w=(s1+s2)/2,其中,w为相邻所述子区域的接合焊盘图形的间隔距离,s1为其中一个子区域内的相邻接合焊盘图形的间隔距离,s2为另一个子区域内的相邻接合焊盘图形的间隔距离。

技术总结

一种半导体结构和掩膜版版图,半导体结构包括:基底;介电层,位于所述基底上,沿平行于所述介电层表面的方向,所述介电层包括多个子区域;键合互连层,位于所述介电层中,所述键合互连层的顶面被所述介电层背向所述基底的表面暴露,所述键合互连层包括多个接合焊盘,多个所述子区域之间的接合焊盘的密度差异满足:使多个所述子区域中的接合焊盘顶面与介电层顶面均处于同一平面。本发明实施例通过使多个子区域之间的接合焊盘的密度差异满足:使多个子区域中的接合焊盘顶面与介电层顶面均处于同一平面,从而在降低键合界面出现缝隙的概率的同时,减小对接合焊盘的尺寸的限制,相应提高了半导体结构的设计多样性。

技术研发人员:唐鹤洹,石强,王志高,高长城

受保护的技术使用者:中芯国际集成电路制造(北京)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!